Τ

### MATERIAL / PACE

- Please classify your perspective on material covered in today's class (27 respondents):

- 1-mostly review, 5-equal new/review, 10-mostly new

- Average 6.27 (↑ previous 6.02)

- Please rate the pace of today's class:

- 1-slow, 5-just right, 10-fast

- Average 5.58 (↑ previous 5.46)

December 7, 2021

TCSS422: Computer Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

### **FEEDBACK**

- I have trouble understanding the math with byte sizes.

- >>> It is good to review charts and patterns:

- 8 bits = 1 byte

- 16 bits = 2 bytes

- 32 bits = 4 bytes

- 64 bits = 8 bytes

- 1,024 bytes = 1 kilobyte (2^10)

- 1,024 kilobytes = 1 megabyte (2^20)

- 1,024 megabytes = 1 gigabyte (2^30)

- 1,024 gigabytes = 1 terabyte (2^40)

- 1,024 terrabytes = 1 petabyte (2^50)

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

### FEEDBACK - 2

- For simplicity rounding is often acceptable:

- 1 kilobyte  $(2^10) = 1,024$  bytes  $\rightarrow$  1,000 bytes

- 1,024 kilobytes (2^20) = 1 megabyte  $\rightarrow$  1,000,000 bytes

- 1,024 megabytes = 1 gigabyte (2^30) → 1,000,000,000 bytes

- 1,024 gigabytes = 1 terabyte (2^40) → 1,000,000,000,000 bytes

- 1,024 terrabytes = 1 petabyte (2^50)→1,000,000,000,000,000 bytes

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, U

School of Engineering and Technology, University of Washington - Tacoma

7

| 21                       | 2      | 217                        | 131,072       | 233                         | 8,589,934,592       | 2 <sup>49</sup>         | 562,949,953,421,312        |

|--------------------------|--------|----------------------------|---------------|-----------------------------|---------------------|-------------------------|----------------------------|

| 22                       | 4      | 218                        | 262,144       | 234                         | 17,179,869,184      | 250                     | 1,125,899,906,842,624      |

| 2 <sup>3</sup>           | 8      | 219                        | 524,288       | 235                         | 34,359,738,368      | 251                     | 2,251,799,813,685,248      |

| 2 <sup>4</sup>           | 16     | 2 <sup>20</sup><br>megabyt | 1,048,576     | 2 <sup>36</sup>             | 68,719,476,736      | 252                     | 4,503,599,627,370,496      |

| 2 <sup>5</sup>           | 32     | 2 <sup>21</sup>            | 2,097,152     | 237                         | 137,438,953,472     | 253                     | 9,007,199,254,740,992      |

| 2 <sup>6</sup>           | 64     | 222                        | 4,194,304     | 238                         | 274,877,906,944     | 254                     | 18,014,398,509,481,984     |

| 27                       | 128    | 2 <sup>23</sup>            | 8,388,608     | 239                         | 549,755,813,888     | 255                     | 36,028,797,018,963,968     |

| 2 <sup>8</sup>           | 256    | 224                        | 16,777,216    | 2 <sup>40</sup><br>terabyte | 1,099,511,627,776   | 2 <sup>56</sup>         | 72,057,594,037,927,936     |

| 2 <sup>9</sup>           | 512    | 225                        | 33,554,432    | 241                         | 2,199,023,255,552   | 2 <sup>57</sup>         | 144,115,188,075,855,872    |

| 2 <sup>10</sup><br>kilob | 1,024  | 2 <sup>26</sup>            | 67,108,864    | 242                         | 4,398,046,511,104   | 258                     | 288,230,376,151,711,744    |

| 211                      | 2,048  | 227                        | 134,217,728   | 243                         | 8,796,093,022,208   | 259                     | 576,460,752,303,423,488    |

| 2 <sup>12</sup>          | 4,096  | 2 <sup>28</sup>            | 268,435,456   | 244                         | 17,592,186,044,416  | 260                     | 1,152,921,504,606,846,976  |

| 2 <sup>13</sup>          | 8,192  | 229                        | 536,870,912   | 245                         | 35,184,372,088,832  | 261                     | 2,305,843,009,213,693,952  |

| 2 <sup>14</sup>          | 16,384 | 2 <sup>30</sup><br>gigabyt | 1,073,741,824 | 246                         | 70,368,744,177,664  | 262                     | 4,611,686,018,427,387,904  |

| 215                      | 32,768 | 231                        | 2,147,483,648 | 247                         | 140,737,488,355,328 | 263                     | 9,223,372,036,854,775,808  |

| 2 <sup>16</sup>          | 65,536 | 232                        | 4,294,967,296 | 248                         | 281,474,976,710,656 | 2 <sup>64</sup><br>bubb | 18,446,744,073,709,551,616 |

# FEEDBACK - 3

- How many bits are required to index the following amounts of memory?

- 1. 1,024 bytes = 1 kilobyte (2^10)

- 2. 1,024 kilobytes = 1 megabyte (2^20)

- 3. 1,024 megabytes = 1 gigabyte (2^30)

- 4. 1,024 gigabytes = 1 terabyte (2^40)

- 5. 1,024 terrabytes = 1 petabyte (2<sup>50</sup>)

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

9

### FEEDBACK - 4

- With paging, we divide an address space in fixed sized pieces (known as the page size)

- Assuming a computer indexes memory using 1 kilobyte memory pages

- How many unique pages are required to manage/index memory?

- 1 kilobyte (2^10) of memory

- 1 page

- 1 megabyte (2^20) of memory

- **1024** pages (2^10)

- 1 gigabyte (2^30) of memory

- **1,048,576 pages (2^20)**

- 1 terabyte (2^40) of memory

- **1**,073,741,824 pages (2^30)

- 1 petabyte (2<sup>50</sup>) of memory

- **1,099,511,627,776 pages (2^40)**

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

10

### **FEEDBACK - 5**

- Assignment 2 Questions:

- In chapter 30, the book mentioned the two broken solutions about using a single condition variable. They recommended using two conditional variable locks in order to fix the problem.

- Yes with the book there is an empty and fill signal for the bounded buffer when working with multiple producers and multiple consumers

- But on Thursday, you mentioned that it is not necessary to add more locks (conditions??) but it's up to us to decide.

- I wonder why it's not necessary and if there's any big difference.

- For each shared bounded buffer in assignment 2, there is only one producer thread and one consumer thread

- Assignment 2 instead has many unique bounded buffer instances

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.11

11

### FEEDBACK - 6

- Is there more information on "pagemon"? I'm still a little bit confused about what it does and why it is useful.

- Pagemon is an interactive tool for browsing memory of a process

- Are there different ways that we can test/identify for deadlock besides looking at the code?

- Try running the program with small bounded buffer sizes

- Try running the program to generate a large number of primes

- Try running the program with minimal to no output to the screen

- Try running the program with no sleep or wait statements

- Try running the program using as many CPU cores as possible on the virtual machine

- The fewer the cores, the fewer the synchronization issues

- 1 core hides deadlock altogether

- 8 cores is better for testing than 4, than 2, etc.

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.12

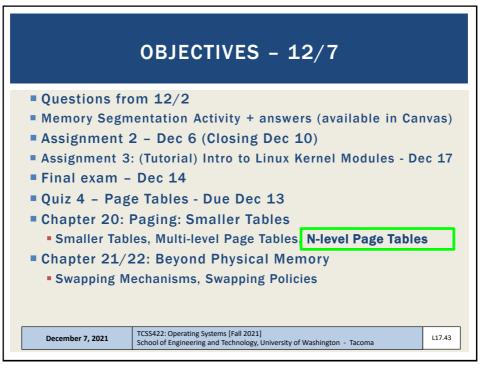

## **OBJECTIVES - 12/7** Questions from 12/2 Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

- Quiz 4 Page Tables Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

13

### **OBJECTIVES - 12/7**

- Questions from 12/2

- Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

- Quiz 4 Page Tables Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.14

- Questions from 12/2

- Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

- Quiz 4 Page Tables Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.15

15

## ASSIGNMENT 3: INTRODUCTION TO LINUX KERNEL MODULES

- Assignment 3 provides an introduction to kernel programming by demonstrating how to create a Linux Kernel Module

- Kernel modules are commonly used to write device drivers and can access protected operating system data structures

- For example: Linux task struct process data structure

- Assignment 3 is scored in the Quizzes / Activities / Tutorials category

- Lowest two grades in this category are dropped

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.16

- Questions from 12/2

- Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

- Quiz 4 Page Tables Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

17

### FINAL EXAM - DEC 14TH

- Tuesday December 14 from 1:30 to 3:30 pm

- Final (100 points)

- SHORT: similar number of questions as the midterm

- 2-hours

- Focus on new content since the midterm (~70% new, 30% before)

- Final Exam Review -

- Complete Memory Segmentation Activity

- Complete Quiz 4

- Practice Final Exam Questions 2<sup>nd</sup> hour of Dec 9<sup>th</sup> class session

- Individual work

- 2 pages of notes (any sized paper), double sided

- Basic calculators allowed

- NO smartphones, laptop, book, Internet, group wowkr

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.18

- Questions from 12/2

- Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

### Quiz 4 - Page Tables - Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, I

School of Engineering and Technology, University of Washington - Tacoma

19

### **OBJECTIVES - 12/7**

- Questions from 12/2

- Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

- Quiz 4 Page Tables Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.20

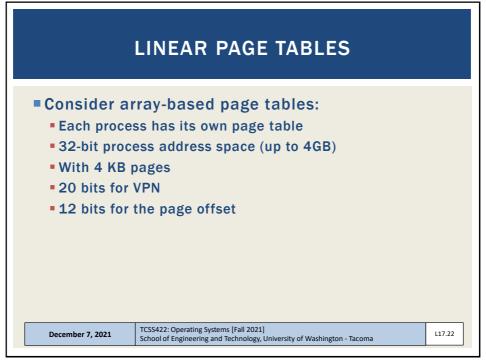

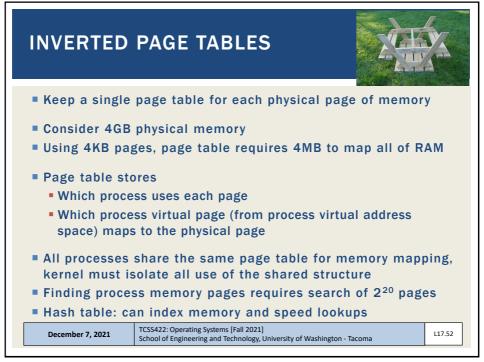

### **LINEAR PAGE TABLES - 2**

- Page tables stored in RAM

- Support potential storage of 2<sup>20</sup> translations = 1,048,576 pages per process @ 4 bytes/page

- Page table size 4MB / process

Page table size =

$$\frac{2^{32}}{2^{12}} * 4Byte = 4MByte$$

- Consider 100+ OS processes

- Requires 400+ MB of RAM to store process information

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

23

### **LINEAR PAGE TABLES - 2**

- Page tables stored in RAM

- Support potential storage of 2<sup>20</sup> translations

- = 1,048,576 pages per process @ 4 bytes/page

- Page table size 4MB / process

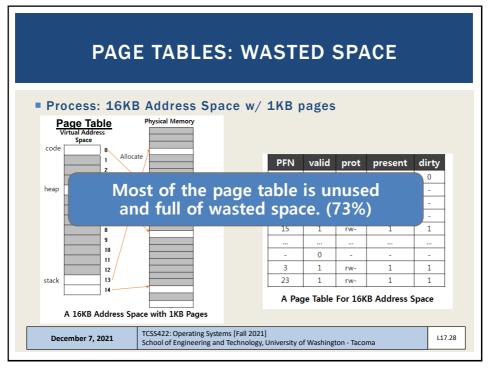

Page tables are too big and consume too much memory.

**Need Solutions ...**

- Consider 100+ OS processes

- Requires 400+ MB of RAM to store process information

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.24

- Questions from 12/2

- Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

- Quiz 4 Page Tables Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, U

School of Engineering and Technology, University of Washington  $\,$  - Tacoma

L17.25

25

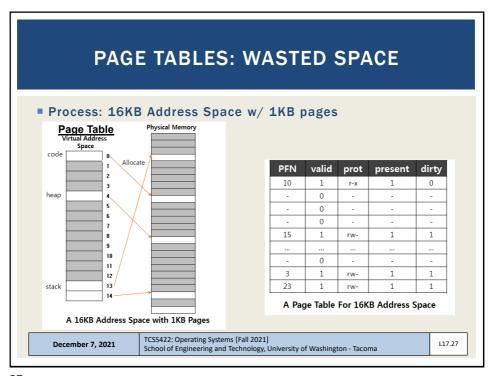

### **PAGING: USE LARGER PAGES**

- Larger pages = 16KB = 2<sup>14</sup>

- 32-bit address space: 2<sup>32</sup>

- $2^{18} = 262,144$  pages

$\frac{2^{32}}{2^{14}} * 4 = 1MB$  per page table

- Memory requirement cut to 1/4

- However pages are huge

- Internal fragmentation results

- 16KB page(s) allocated for small programs with only a few variables

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.26

## **OBJECTIVES - 12/7** Questions from 12/2 Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

- Quiz 4 Page Tables Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

29

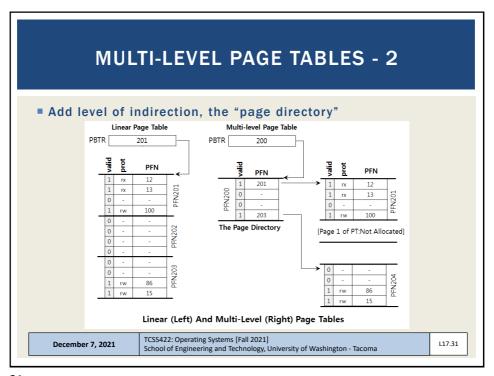

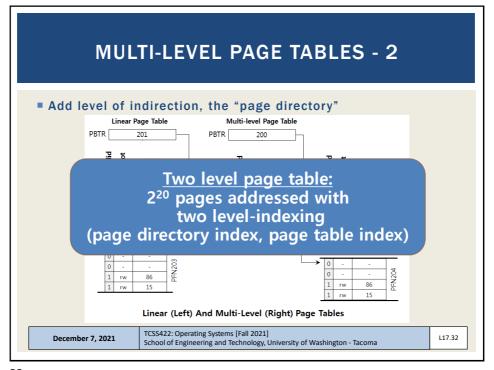

### **MULTI-LEVEL PAGE TABLES**

- Consider a page table:

- 32-bit addressing, 4KB pages

- 2<sup>20</sup> page table entries

- Even if memory is sparsely populated the per process page table requires:

Page table size =

$$\frac{2^{32}}{2^{12}} * 4Byte = 4MByte$$

- Often most of the 4MB per process page table is empty

- Page table must be placed in 4MB contiguous block of RAM

- MUST SAVE MEMORY!

TCSS422: Operating Systems [Fall 2021] December 7, 2021

School of Engineering and Technology, University of Washington - Tacoma

117 30

L17.33

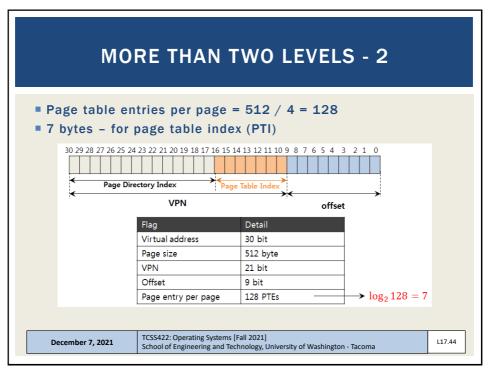

# MULTI-LEVEL PAGE TABLES - 3 Advantages Only allocates page table space in proportion to the address space actually used Can easily grab next free page to expand page table Disadvantages Multi-level page tables are an example of a time-space tradeoff Sacrifice address translation time (now 2-level) for space Complexity: multi-level schemes are more complex

School of Engineering and Technology, University of Washington - Tacoma

TCSS422: Operating Systems [Fall 2021]

33

December 7, 2021

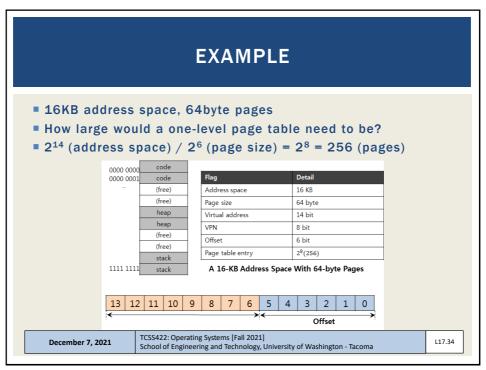

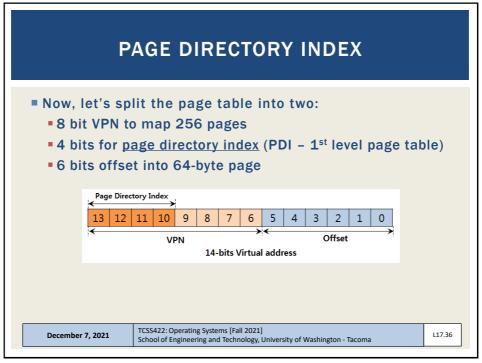

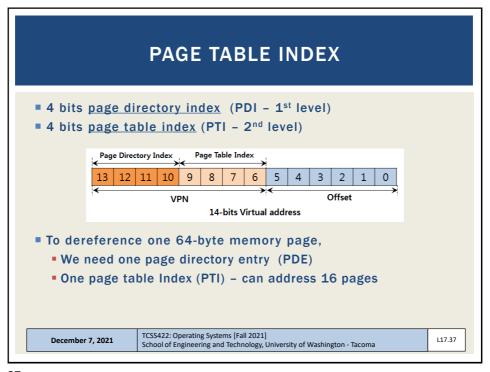

# EXAMPLE - 2 256 total page table entries (64 bytes each) 1,024 bytes page table size, stored using 64-byte pages = (1024/64) = 16 page directory entries (PDEs) Each page directory entry (PDE) can hold 16 page table entries (PTEs) e.g. lookups 16 page directory entries (PDE) x 16 page table entries (PTE) = 256 total PTEs Key idea: the page table is stored using pages too! December 7, 2021 TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

35

Multi-level page table sketch

### **EXAMPLE - 3**

- For this example, how much space is required to store as a <u>single-level</u> page table with any number of PTEs?

- 16KB address space, 64 byte pages

- 256 page frames, 4 byte page size

- 1,024 bytes required (single level)

- How much space is required for a <u>two-level</u> page table with only 4 page table entries (PTEs)?

- Page directory = 16 entries x 4 bytes (1 x 64 byte page)

- Page table = 16 entries (4 used) x 4 bytes (1 x 64 byte page)

- 128 bytes required (2 x 64 byte pages)

- Savings = using just 12.5% the space !!!

December 7, 2021 TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.39

39

For this example, how much space is required to store as a <u>single-level</u> page table with any number of PTEs?

16KB address space, 64 byte pages, 256 page frames, 4 byte page size

Storage requirement:

bytes required (single level)

How much space is required for a <u>two-level</u> page table with only 4 page table entries (PTEs)? (one page each for code segment, stack segment, heap segment, data segment) 16KB address space, 64 byte pages, 256 page frames, 4 byte page size

Page directory = 16 entries x 4 bytes (1 x 64 byte page)

Page table = 16 entries (4 used) x 4 bytes (1 x 64 byte page)

Store requirement = 128 bytes required (2 x 64 byte pages)

Savings =

41

### **32-BIT EXAMPLE**

- Consider: 32-bit address space, 4KB pages, 2<sup>20</sup> pages

- Only 4 mapped pages

- Single level: 4 MB (we've done this before)

- Two level: (old VPN was 20 bits, split in half)

- Page directory = 2<sup>10</sup> entries x 4 bytes = 1 x 4 KB page

- Page table = 4 entries x 4 bytes (mapped to 1 4KB page)

- 8KB (8,192 bytes) required

- Savings = using just .78 % the space !!!

- 100 sparse processes now require < 1MB for page tables

December 7, 2021 TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

```

ADDRESS TRANSLATION CODE

// 5-level Linux page table address lookup

11

// Inputs:

// mm struct - process's memory map struct

// vpage - virtual page address

// Define page struct pointers

pgd t *pgd;

p4d t *p4d;

pud t *pud;

pmd t *pmt;

pte t *pte;

struct page *page;

TCSS422: Operating Systems [Fall 2021]

December 7, 2021

School of Engineering and Technology, University of Washington - Tacoma

```

### **ADDRESS TRANSLATION - 2** pgd\_offset(): pgd = pgd offset(mm, vpage); Takes a vpage address and the mm\_struct if (pgd\_none(\*pgd) || pgd\_bad(\*pgd)) for the process, returns the PGD entry that covers the requested address... return 0; p4d = p4d\_offset(pgd, vpage); p4d/pud/pmd\_offset(): if (p4d none(\*p4d) || p4d bad(\*p4d)) Takes a vpage address and the return 0; pgd/p4d/pud entry and returns the pud = pud\_offset(p4d, vpage); relevant p4d/pud/pmd. if (pud none(\*pud) || pud bad(\*pud)) return 0; pmd = pmd offset(pud, vpage); if (pmd none(\*pmd) || pmd bad(\*pmd)) return 0; if (!(pte = pte offset map(pmd, vpage))) return 0; pte\_unmap() if (!(page = pte\_page(\*pte))) release temporary kernel mapping return 0; for the page table entry physical page addr = page to phys(page) pte\_unmap(pte); return physical\_page\_addr; // param to send back TCSS422: Operating Systems [Fall 2021] December 7, 2021 117 50 School of Engineering and Technology, University of Washington - Tacoma

### **MULTI-LEVEL PAGE TABLE EXAMPLE**

- Consider a 16 MB computer which indexes memory using 4KB pages

- (#1) For a single level page table, how many pages are required to index memory?

- (#2) How many bits are required for the VPN?

- (#3) Assuming each page table entry (PTE) can index any byte on a 4KB page, how many offset bits are required?

- (#4) Assuming there are 8 status bits, how many bytes are required for each page table entry?

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

53

### MULTI LEVEL PAGE TABLE EXAMPLE - 2

- (#5) How many bytes (or KB) are required for a single level page table?

- Let's assume a simple HelloWorld.c program.

- HelloWorld.c requires virtual address translation for 4 pages:

- 1 code page

- 1 stack page

- 1 heap page

- 1 data segment page

- (#6) Assuming a two-level page table scheme, how many bits are required for the Page Directory Index (PDI)?

- (#7) How many bits are required for the Page Table Index (PTI)?

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

117 54

### **MULTI LEVEL PAGE TABLE EXAMPLE - 3**

- Assume each page directory entry (PDE) and page table entry (PTE) requires 4 bytes:

- 6 bits for the Page Directory Index (PDI)

- 6 bits for the Page Table Index (PTI)

- 12 offset bits

- 8 status bits

- (#8) How much total memory is required to index the HelloWorld.c program using a two-level page table when we only need to translate 4 total pages?

- HINT: we need to allocate one Page Directory and one Page Table...

- HINT: how many entries are in the PD and PT

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

55

### **MULTI LEVEL PAGE TABLE EXAMPLE - 4**

- (#9) Using a single page directory entry (PDE) pointing to a single page table (PT), if all of the slots of the page table (PT) are in use, what is the total amount of memory a two-level page table scheme can address?

- (#10) And finally, for this example, as a percentage (%), how much memory does the 2-level page table scheme consume compared to the 1-level scheme?

- <u>HINT</u>: two-level memory use / one-level memory use

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

### ANSWERS **#1** - 4096 pages #2 - 12 bits #3 - 12 bits #4 - 4 bytes ■ #5 - 4096 x 4 = 16,384 bytes (16KB) ■ #6 - 6 bits ■ #7 - 6 bits ■ #8 - 256 bytes for Page Directory (PD) (64 entries x 4 bytes) 256 bytes for Page Table (PT) **TOTAL = 512 bytes** ■ #9 - 64 entries, where each entry maps a 4,096 byte page With 12 offset bits, can address 262,144 bytes (256 KB) ■ #10- 512/16384 = .03125 $\rightarrow$ 3.125% TCSS422: Operating Systems [Fall 2021] December 7, 2021 School of Engineering and Technology, University of Washington - Tacoma

57

# OBJECTIVES - 12/7 Questions from 12/2 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - Dec 6 (Closing Dec 10) Assignment 3: (Tutorial) Intro to Linux Kernel Modules - Dec 17 Final exam - Dec 14 Quiz 4 - Page Tables - Due Dec 13 Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies

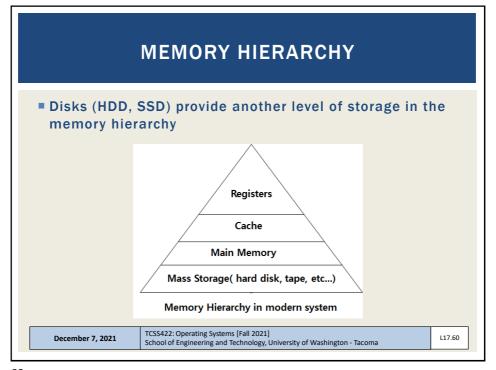

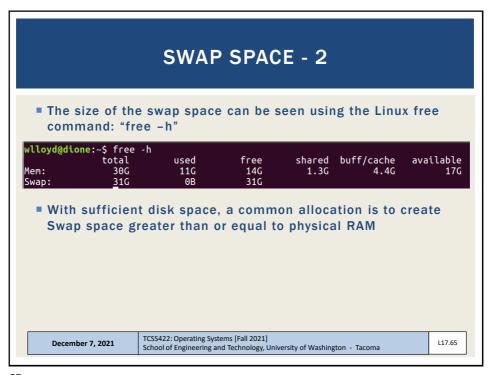

## MOTIVATION FOR EXPANDING THE ADDRESS SPACE

- Provide the illusion of an address space larger than physical RAM

- For a single process

- Convenience

- Ease of use

- For multiple processes

- Large virtual memory space supports running many concurrent processes. . .

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.61

61

### **LATENCY TIMES**

- Design considerations:

- SSDs 4x the time of DRAM

- HDDs 80x the time of DRAM

| Action                             | Latency (ns)  | (μs)      |                              |

|------------------------------------|---------------|-----------|------------------------------|

| L1 cache reference                 | 0.5ns         |           |                              |

| L2 cache reference                 | 7 ns          |           | 14x L1 cache                 |

| Mutex lock/unlock                  | 25 ns         |           |                              |

| Main memory reference              | 100 ns        |           | 20x L2 cache, 200x L1        |

| Read 4K randomly from SSD*         | 150,000 ns    | 150 μs    | ~1GB/sec SSD                 |

| Read 1 MB sequentially from memory | 250,000 ns    | 250 μs    |                              |

| Read 1 MB sequentially from SSD*   | 1,000,000 ns  | 1,000 µs  | 1 ms ~1GB/sec SSD, 4X memory |

| Read 1 MB sequentially from disk   | 20,000,000 ns | 20,000 μs | 20 ms 80x memory, 20X SSD    |

- Latency numbers every programmer should know

- From: https://gist.github.com/jboner/2841832#file-latency-txt

December 7, 2021 TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.62

# OBJECTIVES - 12/7 Questions from 12/2 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - Dec 6 (Closing Dec 10) Assignment 3: (Tutorial) Intro to Linux Kernel Modules - Dec 17 Final exam - Dec 14 Quiz 4 - Page Tables - Due Dec 13 Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables Chapter 21/22: Beyond Physical Memory Swapping Mechanisms Swapping Policies

63

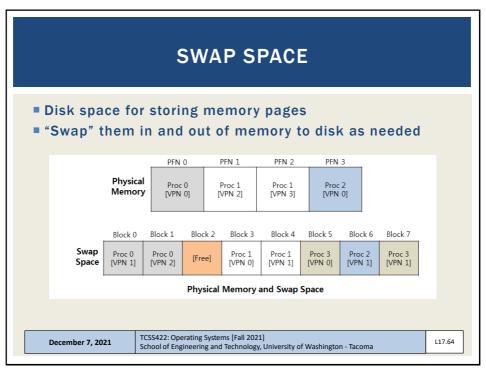

# PAGE LOCATION Memory pages are: Stored in memory Swapped to disk Present bit In the page table entry (PTE) indicates if page is present Page fault Memory page is accessed, but has been swapped to disk TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

67

### **PAGE FAULT** OS steps in to handle the page fault Loading page from disk requires a free memory page Page-Fault Algorithm PFN = FindFreePhysicalPage() 2: if (PFN == -1) // no free page found PFN = EvictPage() // run replacement algorithm DiskRead(PTE.DiskAddr, pfn) 4: // sleep (waiting for I/O) // set PTE bit to present 5: PTE.present = True PTE.PFN = PFN // reference new loaded page 7: RetryInstruction() // retry instruction TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma December 7, 2021 L17.68

### PAGE REPLACEMENTS

- Page daemon

- Background threads which monitors swapped pages

- Low watermark (LW)

- Threshold for when to swap pages to disk

- Daemon checks: free pages < LW</p>

- Begin swapping to disk until reaching the highwater mark

- High watermark (HW)

- Target threshold of free memory pages

- Daemon free until: free pages >= HW

TCSS422: Operating Systems [Fall 2021] December 7, 2021 School of Engineering and Technology, University of Washington - Tacoma

### **OBJECTIVES - 12/7**

- Questions from 12/2

- Memory Segmentation Activity + answers (available in Canvas)

- Assignment 2 Dec 6 (Closing Dec 10)

- Assignment 3: (Tutorial) Intro to Linux Kernel Modules Dec 17

- Final exam Dec 14

- Quiz 4 Page Tables Due Dec 13

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

- Chapter 21/22: Beyond Physical Memory

- Swapping Mechanisms, Swapping Policies

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

L17.70

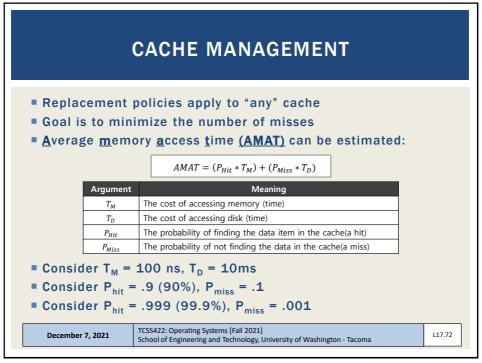

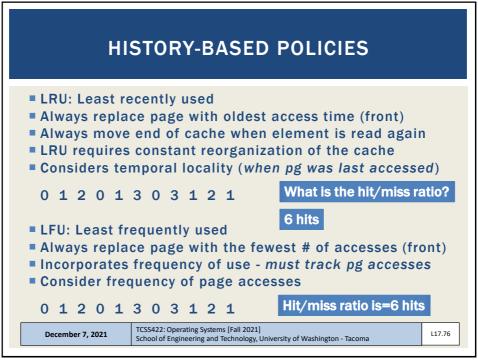

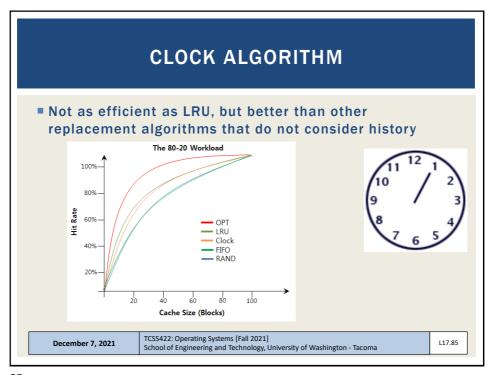

### IMPLEMENTING LRU

- Implementing last recently used (LRU) requires tracking access time for all system memory pages

- Times can be tracked with a list

- For cache eviction, we must scan an entire list

- Consider: 4GB memory system (2<sup>32</sup>), with 4KB pages (212)

- This requires 2<sup>20</sup> comparisons !!!

- Simplification is needed

- Consider how to approximate the oldest page access

December 7, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

83

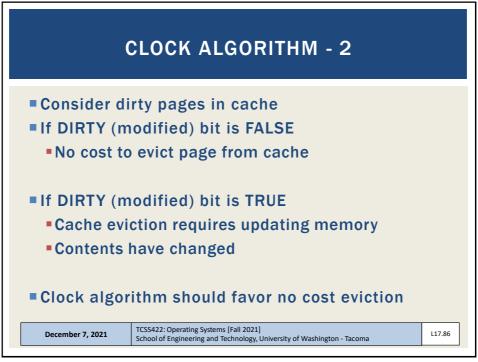

### **IMPLEMENTING LRU - 2**

- Harness the Page Table Entry (PTE) Use Bit

- HW sets to 1 when page is used

- OS sets to 0

- Clock algorithm (approximate LRU)

- Refer to pages in a circular list

- Clock hand points to current page

- Loops around

- IF USE\_BIT=1 set to USE\_BIT = 0

- IF USE\_BIT=0 replace page

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

117 84

L17.83

### WHEN TO LOAD PAGES

- On demand → demand paging

- Prefetching

- Preload pages based on anticipated demand

- Prediction based on locality

- Access page P, suggest page P+1 may be used

- What other techniques might help anticipate required memory pages?

- Prediction models, historical analysis

- In general: accuracy vs. effort tradeoff

- High analysis techniques struggle to respond in real time

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

### OTHER SWAPPING POLICIES

- Page swaps / writes

- Group/cluster pages together

- Collect pending writes, perform as batch

- Grouping disk writes helps amortize latency costs

- Thrashing

- Occurs when system runs many memory intensive processes and is low in memory

- Everything is constantly swapped to-and-from disk

December 7, 2021

TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

# OTHER SWAPPING POLICIES - 2 Working sets Groups of related processes When thrashing: prevent one or more working set(s) from running Temporarily reduces memory burden Allows some processes to run, reduces thrashing Tessage: Tessage:

89