**FEEDBACK** Requesting more time on assignment 2, if possible. This is unrelated, but I was hoping if an extension can be granted for assignment 2 This is unrelated, but I was hoping if an extension can be granted for assignment 2 due to conflicts with assignments from other classes Can we get extensions on the quiz and assignment 2 due to this week? A lot of us have been busy with other classes and could use the time to turn in a sufficient enough product. Thank you! December 2, 2021 TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma L16.6

6

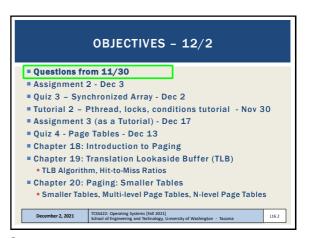

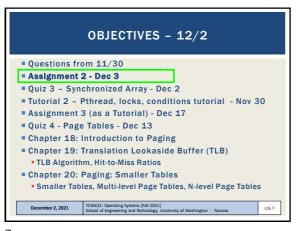

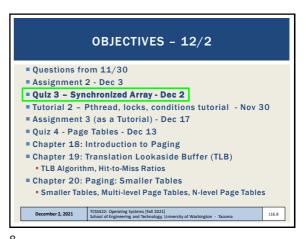

OBJECTIVES - 12/2

Questions from 11/30

Assignment 2 - Dec 3

Quiz 3 - Synchronized Array - Dec 2

Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30

Assignment 3 (as a Tutorial) - Dec 17

Quiz 4 - Page Tables - Dec 13

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

December 2, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

10

9

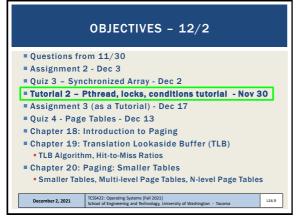

OBJECTIVES - 12/2

Questions from 11/30

Assignment 2 - Dec 3

Quiz 3 - Synchronized Array - Dec 2

Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30

Assignment 3 (as a Tutorial) - Dec 17

Quiz 4 - Page Tables - Dec 13

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

Chapter 20: Paging: Smaller Tables, N-level Page Tables

11 12

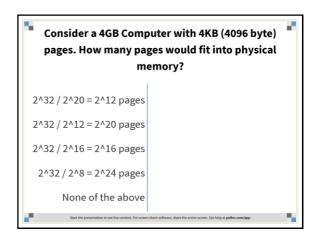

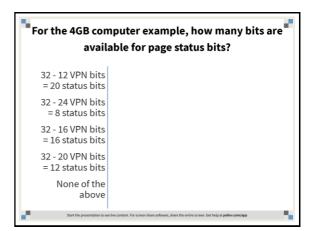

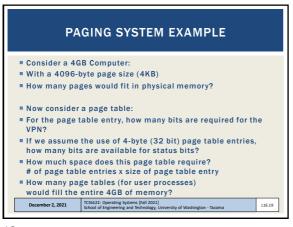

For the 4GB computer example, how many bits are required for the VPN?

24 VPN bits (indexes 2^24 locations)

16 VPN bits (indexes 2^16 locations)

20 VPN bits (indexes 2^20 locations)

12 VPN bits (indexes 2^12 locations)

None of the above

1058422 Operating Systems (Fal 2021)

1058422 Operating Systems (Fal 2021)

116.

16

15

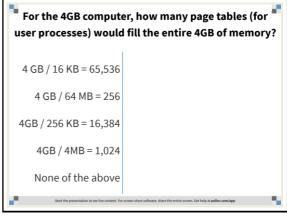

For the 4GB computer, how much space does this page table require? (number of page table entries x size of page table entry)

2^20 entries x 4b = 4 MB

2^12 entries x 4b = 16 KB

2^16 entries x 4b = 256 KB

2^24 entries x 4b = 64 MB

None of the above

17 18

OBJECTIVES - 12/2

Questions from 11/30

Assignment 2 - Dec 3

Quiz 3 - Synchronized Array - Dec 2

Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30

Assignment 3 (as a Tutorial) - Dec 17

Quiz 4 - Page Tables - Dec 13

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

December 2, 2021

TCSS42: Opening Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

20

22

19

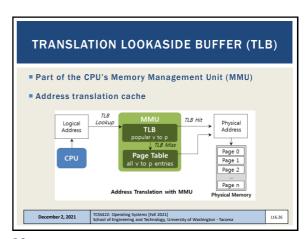

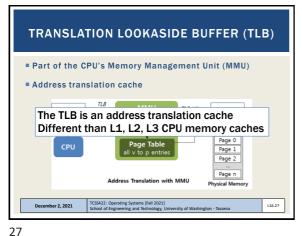

TRANSLATION LOOKASIDE BUFFER

■ Legacy name...

■ Better name, "Address Translation Cache"

■ TLB is an on CPU cache of address translations

■ virtual → physical memory

December 2, 2021 TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

21

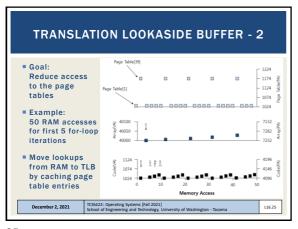

**VISUALIZING MEMORY ACCESSES:** FOR THE FIRST 5 LOOP ITERATIONS Locations: Page table 1174 Array - 1124 • Code 1074 0 0000 0000 0000 0000 000 - 1024 50 accesses for 5 loop 7282 iterations 4146 December 2, 2021 L16.24 rsity of Washington - Tacoma

23 24

OBJECTIVES - 12/2

Questions from 11/30

Assignment 2 - Dec 3

Quiz 3 - Synchronized Array - Dec 2

Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30

Assignment 3 (as a Tutorial) - Dec 17

Quiz 4 - Page Tables - Dec 13

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm

Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

December 2, 2021

TCSS42: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Taxoma

28

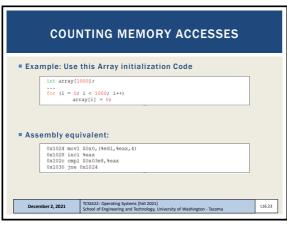

```

TLB BASIC ALGORITHM

For: array based page table

■ Hardware managed TLB

1: VPN = (VirtualAddress & VPN_MASK ) >> SHIFT

2: (Success , TlbEntry) = TLB_Lookup(VPN)

if(Success == True){ // TLB H

if(CanAccess(TlbEntry.ProtectBits) == True){

5:

Offset = VirtualAddress & OFFSET MASK

PhysAddr (TlbEntry.PFN << SHIFT) | Offset

AccessMemory( PhysAddr )

| else RaiseException(PROTECTION_ERROR)

Generate the physical address to access memory

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

December 2, 2021

L16.29

```

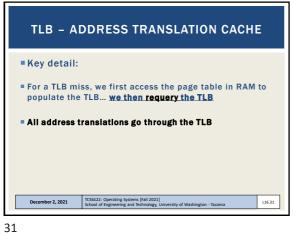

**TLB BASIC ALGORITHM - 2** 11: else{ //TLB Mis: PTEAddr = PTBR + (VPN \* sizeof(PTE)) 12: PTE = AccessMemory(PTEAddr) 13: (...) // Check for, and raise exceptions... TLB\_Insert( VPN , PTE.PFN , PTE.ProtectBits)

RetryInstruction() 16: 17: 18: Retry the instruction... (requery the TLB) December 2, 2021 L16.30 versity of Washington - Tacoma

29 30

**OBJECTIVES - 12/2** Questions from 11/30 Assignment 2 - Dec 3 Quiz 3 - Synchronized Array - Dec 2 Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30 Assignment 3 (as a Tutorial) - Dec 17 Quiz 4 - Page Tables - Dec 13 ■ Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm. Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma

32

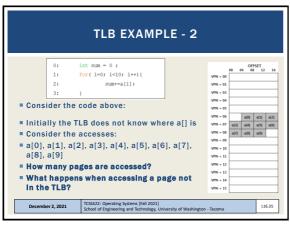

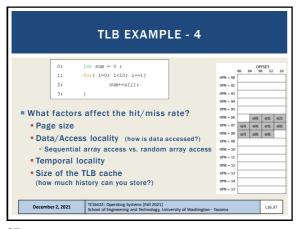

**TLB EXAMPLE** for( i=0; i<10; i++){ VPN = 03 ■ Example: VPN - 05 Program address space: 256-byte VPN = 07 Addressable using 8 total bits (28) 4 bits for the VPN (16 total pages) VPN = 0 ■ Page size: 16 bytes Offset is addressable using 4-bits VPN - 14 Store an array: of (10) 4-byte integers December 2, 2021 L16.34

34

**TLB EXAMPLE - 3** for( i=0; i<10; i++){ VPN = 03 ■ For the accesses: a[0], a[1], a[2], a[3], a[4], a[5], a[6], a[7], a[8], a[9] VPN = 08 VPN = 09 ■ How many are hits? VPN = 1 ■ How many are misses? VPN = 12 What is the hit rate? (%) • 70% (3 misses one for each VP. 7 hits) VPN - 14 TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, Uni December 2, 2021 L16.36 rsity of Washington - Tacoma

35 36

**OBJECTIVES - 12/2** Questions from 11/30 Assignment 2 - Dec 3 Quiz 3 - Synchronized Array - Dec 2 ■ Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30 Assignment 3 (as a Tutorial) - Dec 17 Quiz 4 - Page Tables - Dec 13 ■ Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma December 2, 2021 L16.38

37

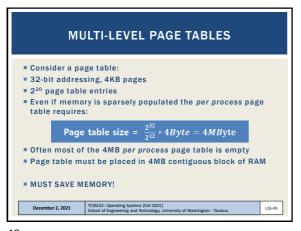

**LINEAR PAGE TABLES** ■ Consider array-based page tables: Each process has its own page table 32-bit process address space (up to 4GB) With 4 KB pages 20 bits for VPN • 12 bits for the page offset December 2, 2021 L16.40

39

**LINEAR PAGE TABLES - 2** ■ Page tables stored in RAM Support potential storage of 2<sup>20</sup> translations = 1,048,576 pages per process @ 4 bytes/page ■ Page table size 4MB / process  $|\frac{2^{32}}{2^{12}}*4Byte|$  = Page table size = 4MByte Consider 100+ OS processes Requires 400+ MB of RAM to store process information TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma December 2, 2021 L16.41 41

**LINEAR PAGE TABLES - 2** ■ Page tables stored in RAM Support potential storage of 2<sup>20</sup> translations = 1,048,576 pages per process @ 4 bytes/page ■ Page table size 4MB / process Page tables are too big and consume too much memory. Need Solutions ... Consider 100+ OS processes Requires 400+ MB of RAM to store process information December 2, 2021 L16.42

42

40

**PAGING: USE LARGER PAGES** ■ <u>Larger pages</u> = 16KB = 2<sup>14</sup> ■ 32-bit address space: 232 ■ 2<sup>18</sup> = 262,144 pages  $\frac{2^{32}}{2^{14}} * 4 = 1MB$  per page table ■ Memory requirement cut to 1/4 However pages are huge ■ Internal fragmentation results ■ 16KB page(s) allocated for small programs with only a few variables December 2, 2021

43 44

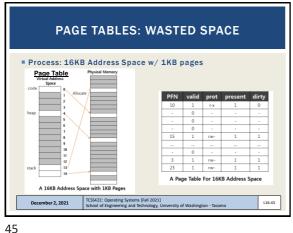

PAGE TABLES: WASTED SPACE ■ Process: 16KB Address Space w/ 1KB pages Page Table PFN valid prot present dirty Most of the page table is unused and full of wasted space. (73%) A Page Table For 16KB Address Space December 2, 2021 L16.46

46

**OBJECTIVES - 12/2** ■ Questions from 11/30 Assignment 2 - Dec 3 Quiz 3 - Synchronized Array - Dec 2 ■ Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30 Assignment 3 (as a Tutorial) - Dec 17 Quiz 4 - Page Tables - Dec 13 Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables Multi-level Page Tables

N-level Page Tables December 2, 2021 L16.48

47 48

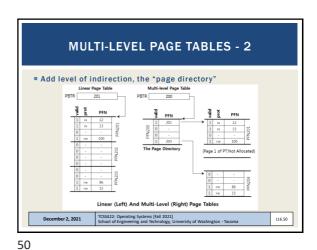

**MULTI-LEVEL PAGE TABLES - 2** Add level of indirection, the "page directory" Two level page table: 220 pages addressed with two level-indexing (page directory index, page table index) Linear (Left) And Multi-Level (Right) Page Table: December 2, 2021 L16.51

**MULTI-LEVEL PAGE TABLES - 3** Advantages Only allocates page table space in proportion to the address space actually used Can easily grab next free page to expand page table Disadvantages Multi-level page tables are an example of a time-space tradeoff Sacrifice address translation time (now 2-level) for space Complexity: multi-level schemes are more complex December 2, 2021 L16.52

51

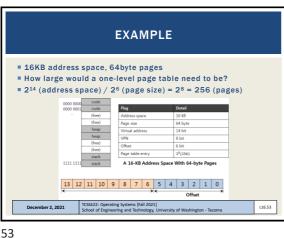

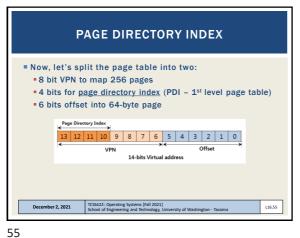

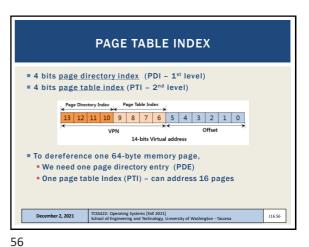

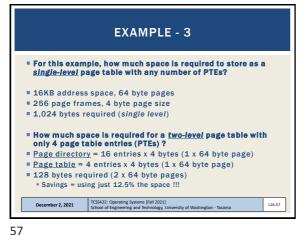

**EXAMPLE - 2** 256 total page table entries (64 bytes each) ■ 1,024 bytes page table size, stored using 64-byte pages = (1024/64) = 16 page directory entries (PDEs) Each page directory entry (PDE) can hold 16 page table entries (PTEs) e.g. lookups ■ 16 page directory entries (PDE) x 16 page table entries (PTE) = 256 total PTEs Key idea: the page table is stored using pages too! TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma December 2, 2021 L16.54

54

**32-BIT EXAMPLE** Consider: 32-bit address space, 4KB pages, 220 pages Only 4 mapped pages • Single level: 4 MB (we've done this before) ■ Two level: (old VPN was 20 bits, split in half) ■ <u>Page directory</u> = 2<sup>10</sup> entries x 4 bytes = 1 x 4 KB page Page table = 4 entries x 4 bytes (mapped to 1 4KB page) ■ 8KB (8,192 bytes) required Savings = using just .78 % the space !!! ■ 100 sparse processes now require < 1MB for page tables December 2, 2021 L16.58

58

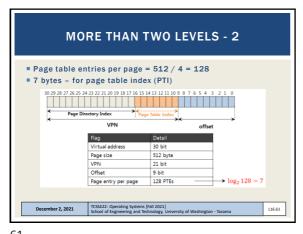

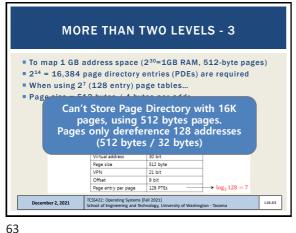

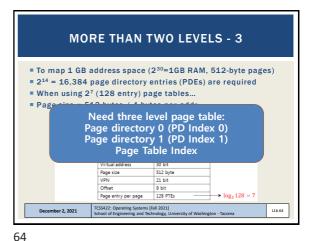

MORE THAN TWO LEVELS ■ Consider: page size is 29 = 512 bytes ■ Page size 512 bytes / Page entry size 4 bytes ■ VPN is 21 bits Virtual address 30 bit Page size 512 byte Offset 9 bit December 2, 2021 L16.60

59 60

```

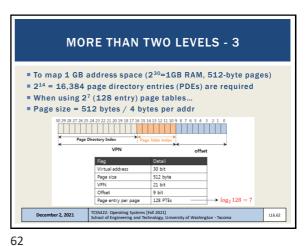

MORE THAN TWO LEVELS - 4

■ We can now address 1GB with "fine grained" 512 byte pages

Using multiple levels of indirection

Page Table Index

Consider the implications for address translation!

How much space is required for a virtual address space with 4

entries on a 512-byte page? (let's say 4 32-bit integers)

PD0 1 page, PD1 1 page, PT 1 page = 1,536 bytes

■ Memory Usage= 1,536 (3-level) / 8,388,608 (1-level) = .0183% !!!

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

December 2, 2021

```

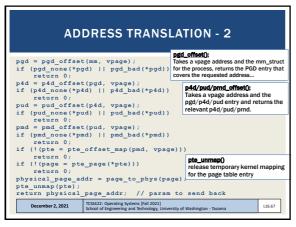

```

ADDRESS TRANSLATION CODE

// 5-level Linux page table address lookup

// Inputs:

// mm_struct - process's memory map struct

// vpage - virtual page address

// Define page struct pointers

pgd_t *pgd;

p4d_t *p4d;

pud t *pud;

pmd_t *pmt;

pte_t *pte;

struct page *page;

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

December 2, 2021

L16.66

```

65 66

| Keep a single page table for each physical page of memory

| Consider 4GB physical memory

| Using 4KB pages, page table requires 4MB to map all of RAM

| Page table stores

| Which process uses each page

| Which process virtual page (from process virtual address space) maps to the physical page

| All processes share the same page table for memory mapping, kernel must isolate all use of the shared structure

| Finding process memory pages requires search of 220 pages

| Hash table: can index memory and speed lookups

| December 2, 2021 | TGSS222 Operating Systems [Flat 2021] | TGSS222 Operating Systems

68

70

67

69

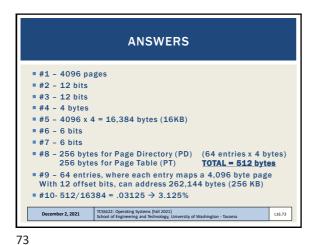

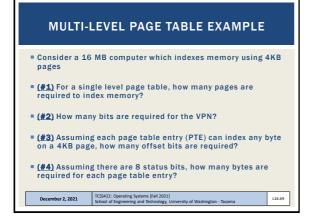

**MULTI LEVEL PAGE TABLE EXAMPLE - 3** Assume each page directory entry (PDE) and page table entry (PTE) requires 4 bytes: • 6 bits for the Page Directory Index (PDI) • 6 bits for the Page Table Index (PTI) • 12 offset bits 8 status bits • (#8) How much total memory is required to index the HelloWorld.c program using a two-level page table when we only need to translate 4 total pages? HINT: we need to allocate one Page Directory and one Page Table.. ■ HINT: how many entries are in the PD and PT TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma December 2, 2021 L16.71 | MULTI LEVEL PAGE TABLE EXAMPLE - 4

| (#9) Using a single page directory entry (PDE) pointing to a single page table (PT), if all of the slots of the page table (PT) are in use, what is the total amount of memory a two-level page table scheme can address?

| (#10) And finally, for this example, as a percentage (%), how much memory does the 2-level page table scheme consume compared to the 1-level scheme?

| HINT: two-level memory use / one-level memory use