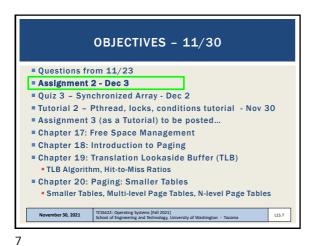

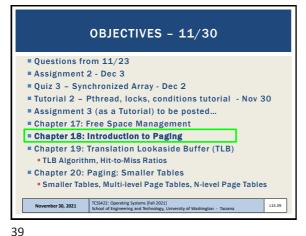

OBJECTIVES - 11/30

Questions from 11/23

Assignment 2 - Dec 3

Quiz 3 - Synchronized Array - Dec 2

Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30

Assignment 3 (as a Tutorial) to be posted...

Chapter 17: Free Space Management

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

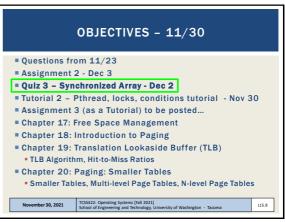

OBJECTIVES - 11/30

Questions from 11/23

Assignment 2 - Dec 3

Quiz 3 - Synchronized Array - Dec 2

Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30

Assignment 3 (as a Tutorial) to be posted...

Chapter 17: Free Space Management

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

OBJECTIVES - 11/30

Questions from 11/23

Assignment 2 - Dec 3

Quiz 3 - Synchronized Array - Dec 2

Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30

Assignment 3 (as a Tutorial) to be posted...

Chapter 17: Free Space Management

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

November 30, 2021

TCSS42: Operating Systems [fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

CHAPTER 17: FREE SPACE MANAGEMENT

TCSS42: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - 1: ona L15.12

Slides by Wes J. Lloyd

11

9

L15.2

10

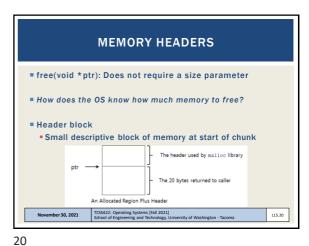

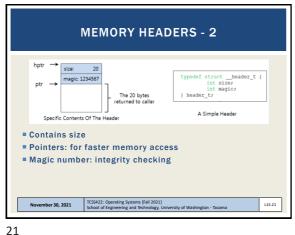

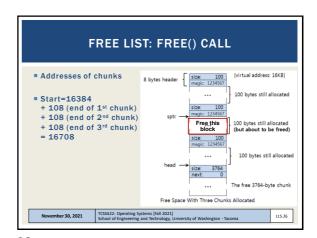

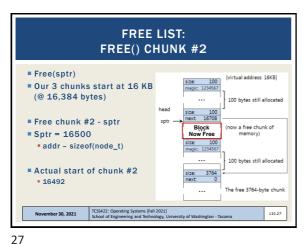

MEMORY HEADERS - 3

Size of memory chunk is:

Header size + user malloc size

N bytes + sizeof(header)

Easy to determine address of header

void free (void \*ptr) {

header\_t \*hptr = (void \*)ptr - sizeof(header\_t);

}

November 30, 2021

TCS5422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington -Taxoma

22

21

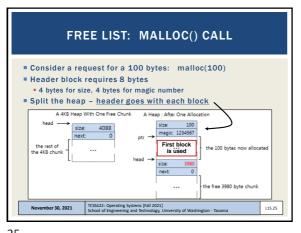

FREE LIST - 2

Create and initialize free-list "heap"

// map() returns a pointer to a chunk of free space node\_t "head = mmap(NULL, 40)6, PROT READ PROT WRITE, head->size = 4096 - sizeof(node\_t);

MAP\_ANON(MAP\_PRIVATE, -1, 0); head->next = NULL;

Heap layout:

(virtual address: 16KB) header: size field header: next field(NULL is 0)

the rest of the 4KB chunk

November 30, 2021

ITSS422: Operating Systems [fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

23 24

I

29 30

34

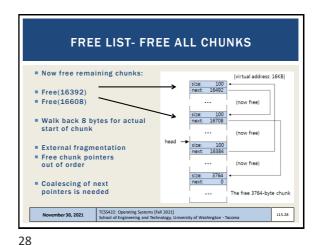

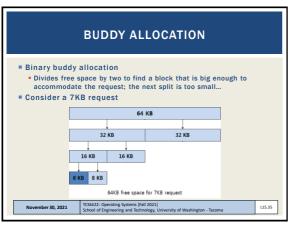

BUDDY ALLOCATION - 2

Buddy allocation: suffers from internal fragmentation

Allocated fragments, typically too large

Coalescing is simple

Two adjacent blocks are promoted up

35 36

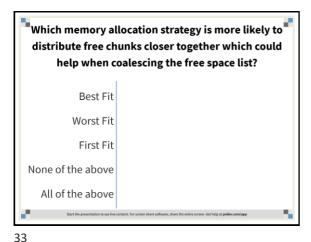

A request is made to store 1 byte. For this scenario, which memory allocation strategy will always locate memory the fastest? Best fit Worst fit Next fit None of the above All of the above

38

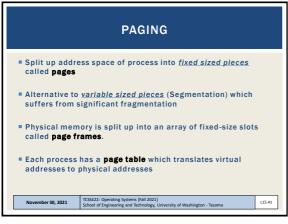

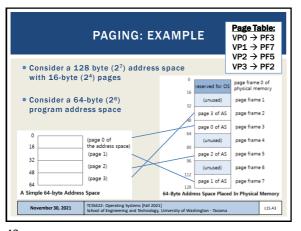

**CHAPTER 18: INTRODUCTION TO PAGING**

40

**ADVANTAGES OF PAGING** ■ Flexibility Abstracts the process address space into pages No need to track direction of HEAP / STACK growth Just add more pages... No need to store unused space As with segments... Simplicity Pages and page frames are the same size Easy to allocate and keep a free list of pages November 30, 2021 L15.42

41 42

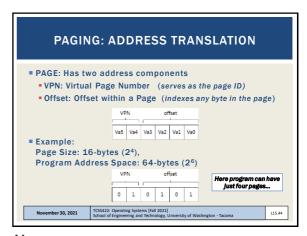

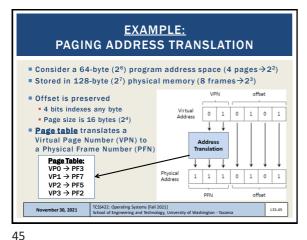

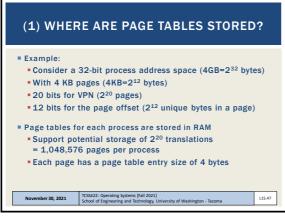

PAGING DESIGN QUESTIONS (1) Where are page tables stored? (2) What are the typical contents of the page table? (3) How big are page tables? (4) Does paging make the system too slow? November 30, 2021 L15.46

46

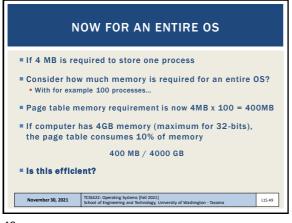

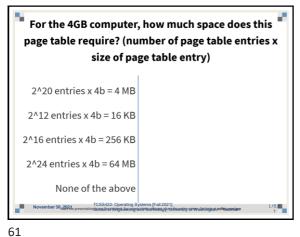

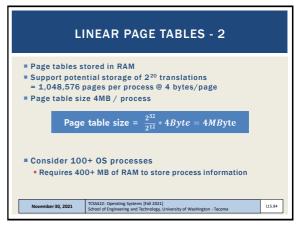

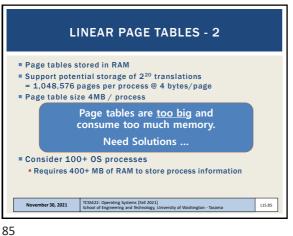

PAGE TABLE EXAMPLE With 2<sup>20</sup> slots in our page table for a single process Each slot (i.e. entry) dereferences a VPN VPN<sub>0</sub> Each entry provides a physical frame number VPN₁  ${\rm VPN_2}$ ■ Each entry requires 4 bytes (32 bits) 20 for the PFN on a 4GB system with 4KB pages 12 for the offset which is preserved (note we have no status bits, so this is VPN<sub>1048576</sub> unrealistically small) How much memory is required to store the page table for 1 process? Hint: # of entries x space per entry 4,194,304 bytes (or 4MB) to index one process TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma November 30, 2021 L15.48

47 48

(2) WHAT'S ACTUALLY IN THE PAGE TABLE ■ Page table is data structure used to map virtual page numbers (VPN) to the physical address (Physical Frame Number PFN) Linear page table → simple array ■ Page-table entry • 32 bits for capturing state 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 An x86 Page Table Entry(PTE) November 30, 2021 L15.50

49

**PAGE TABLE ENTRY** □ P: present □ R/W: read/write bit □ U/S: supervisor ■ A: accessed bit D: dirty bit □ PFN: the page frame number 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 10 PFN An x86 Page Table Entry(PTE) November 30, 2021 L15.51

**PAGE TABLE ENTRY - 2** Common flags: • Valid Bit: Indicating whether the particular translation is valid. Protection Bit: Indicating whether the page could be read from, written to, or executed from Present Bit: Indicating whether this page is in physical memory or on disk(swapped out) ■ <u>Dirty Bit:</u> Indicating whether the page has been modified since it was brought into memory Reference Bit(Accessed Bit): Indicating that a page has been

51

(3) HOW BIG ARE PAGE TABLES? ■ Page tables are too big to store on the CPU ■ Page tables are stored using physical memory ■ Paging supports efficiently storing a sparsely populated address space Reduced memory requirement Compared to base and bounds, and segments November 30, 2021 L15.53

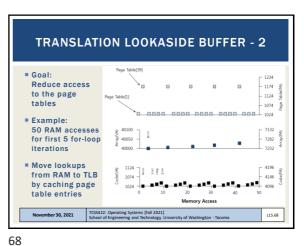

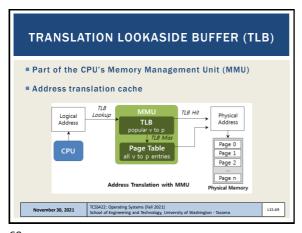

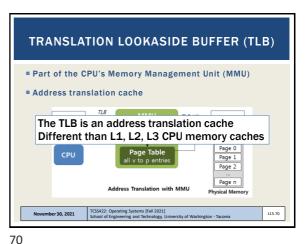

(4) DOES PAGING MAKE THE SYSTEM TOO SLOW? ■ Translation Issue #1: Starting location of the page table is needed Page Table: HW Support: Page-table base register  $VP0 \rightarrow PF3$ stores active process VP1 → PF7 Facilitates translation VP2 → PF5 Stored in RAM → VP3 → PF2 Issue #2: Each memory address translation for paging requires an extra memory reference HW Support: TLBs (Chapter 19) November 30, 2021 L15.54

52

vember 30, 2021

50

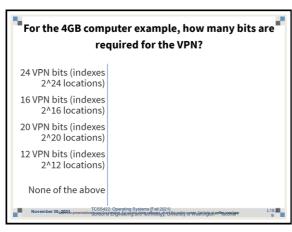

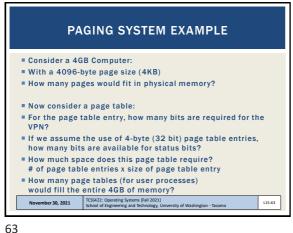

Consider a 4GB Computer with 4KB (4096 byte) pages. How many pages would fit into physical memory?

2^32 / 2^20 = 2^12 pages

2^32 / 2^12 = 2^20 pages

2^32 / 2^16 = 2^16 pages

2^32 / 2^8 = 2^24 pages

None of the above

58

5/

For the 4GB computer example, how many bits are available for page status bits?

32 - 12 VPN bits = 20 status bits

32 - 24 VPN bits = 8 status bits

32 - 16 VPN bits = 16 status bits

32 - 20 VPN bits = 16 status bits

None of the above

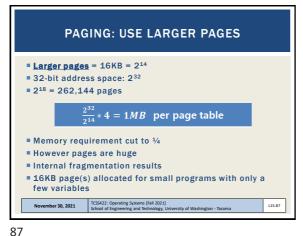

For the 4GB computer, how many page tables (for user processes) would fill the entire 4GB of memory? 4 GB / 16 KB = 65,536 4 GB / 64 MB = 256 4GB / 256 KB = 16,384 4GB / 4MB = 1,024 None of the above

62

64

**OBJECTIVES - 11/30** ■ Questions from 11/23 Assignment 2 - Dec 3 Quiz 3 - Synchronized Array - Dec 2 ■ Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables November 30, 2021

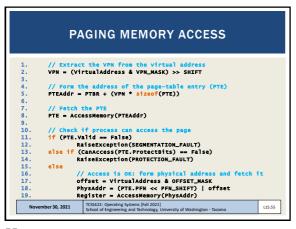

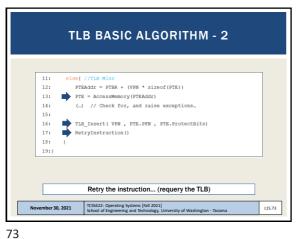

**TLB BASIC ALGORITHM** For: array based page table ■ Hardware managed TLB 1: VPN = (VirtualAddress & VPN\_MASK ) >> SHIFT 2: (Success , TlbEntry) = TLB\_Lookup(VPN) if(Success == True){ // if(CanAccess(TlbEntry.ProtectBits) == True){ 5: Offset = VirtualAddress & OFFSET MASK PhysAddr (TlbEntry.PFN << SHIFT) | Offset AccessMemory( PhysAddr ) else RaiseException(PROTECTION\_ERROR) Generate the physical address to access memory November 30, 2021 L15.72

71 72

**OBJECTIVES - 11/30** Questions from 11/23 Assignment 2 - Dec 3 Quiz 3 - Synchronized Array - Dec 2 Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 17: Free Space Management ■ Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables versity of Washington - Tacoma

86

88

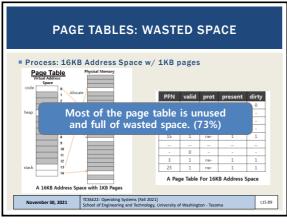

PAGE TABLES: WASTED SPACE ■ Process: 16KB Address Space w/ 1KB pages Page Table A Page Table For 16KB Address Space mber 30, 2021 L15.88

**OBJECTIVES - 11/30** ■ Questions from 11/23 Assignment 2 - Dec 3 Quiz 3 - Synchronized Array - Dec 2 ■ Tutorial 2 - Pthread, locks, conditions tutorial - Nov 30 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables Multi-level Page Tables

N-level Page Tables November 30, 2021 L15.90

89 90

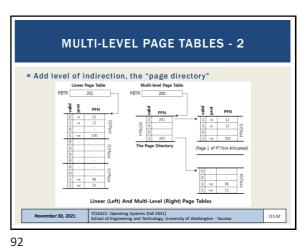

MULTI-LEVEL PAGE TABLES - 3

Advantages

Only allocates page table space in proportion to the address space actually used

Can easily grab next free page to expand page table

Disadvantages

Multi-level page tables are an example of a time-space tradeoff

Sacrifice address translation time (now 2-level) for space

Complexity: multi-level schemes are more complex

| November 30, 2021 | TCSS422: Operating Systems [Fall 2021] | School of Engineering and Technology, University of Washington - Taxoms

| L15.94|

94

93

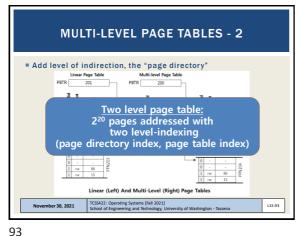

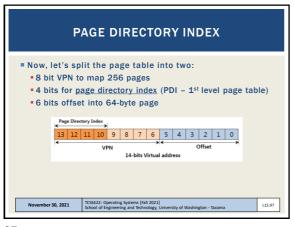

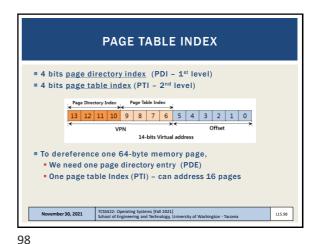

EXAMPLE - 2

256 total page table entries (64 bytes each)

1,024 bytes page table size, stored using 64-byte pages = (1024/64) = 16 page directory entries (PDEs)

Each page directory entry (PDE) can hold 16 page table entries (PTEs) e.g. lookups

16 page directory entries (PDE) x 16 page table entries (PTE) = 256 total PTEs

Key Idea: the page table is stored using pages tool

November 30, 2021 | TCSS422- Operating Systems [Fall 2021] | School of Engineering and Technology, University of Washington - Tacoma | L15.56

95 96

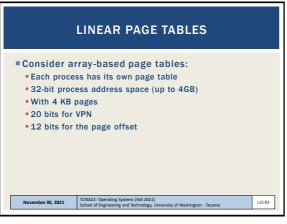

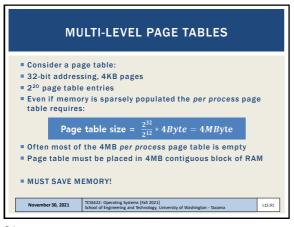

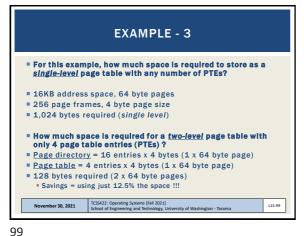

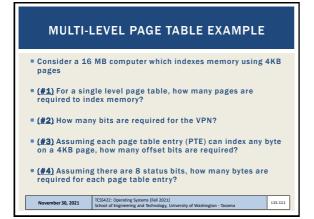

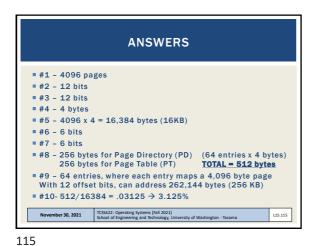

Consider: 32-bit address space, 4KB pages, 2<sup>20</sup> pages

Only 4 mapped pages

Single level: 4 MB (we've done this before)

Two level: (old VPN was 20 bits, split in half)

Page directory = 2<sup>10</sup> entries x 4 bytes = 1 x 4 KB page

Page table = 4 entries x 4 bytes (mapped to 1 4KB page)

KKB (8,192 bytes) required

Savings = using just .78 % the space !!!

100 sparse processes now require < 1MB for page tables

November 30, 2021

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

100

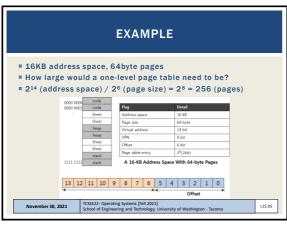

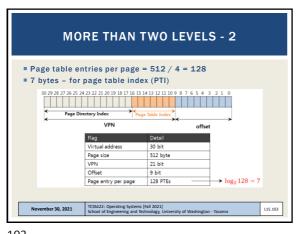

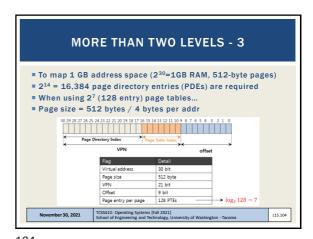

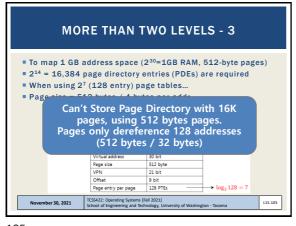

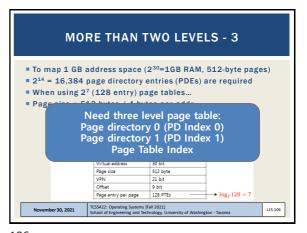

## Consider: page size is 29 = 512 bytes

## Page size 512 bytes / Page entry size 4 bytes

## VPN is 21 bits

## VPN offset

## Detail

## VPN offset

## Detail

## VPN offset

## Detail

## VPN 21 bit

## Detail

## VPN 22 bit

## Detail

## VPN 23 bit

## Detail

## VPN 25 bit

## Detail

## VPN 26 bit

## Detail

## VPN 27 bit

## Detail

## VPN 27 bit

## Detail

## VPN 28 bit

## Detail

## VPN 29 bit

## Detail

## VPN 21 bit

## Detail

## VPN 32 bit

## Detail

## VPN 33 bit

## Detail

## VPN 34 bit

## Detail

## VPN 35 bit

## Detail

## Detail

## VPN 35 bit

## Detail

## Detai

101 102

105 106

```

We can now address 1GB with "fine grained" 512 byte pages

Using multiple levels of indirection

10.29 28 77 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PD Index 0 PD Index 1 Page Table Index

VPN

Consider the implications for address translation!

How much space is required for a virtual address space with 4 entries on a 512-byte page? (let's say 4 32-bit integers)

PD 0 1 page, PD 1 1 page, PT 1 page = 1,536 bytes

Memory Usage= 1,536 (3-level) / 8,388,608 (1-level) = .0183% !!!

November 30, 2021

TCSS422: Operating Systems [fall 2021]

School of Engineering and Technology, University of Washington - Taccoma

```

```

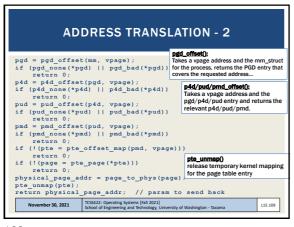

ADDRESS TRANSLATION CODE

// 5-level Linux page table address lookup

11

// Inputs:

// mm_struct - process's memory map struct

// vpage - virtual page address

// Define page struct pointers

pgd_t *pgd;

p4d_t *p4d;

pud t *pud;

pmd_t *pmt;

pte_t *pte;

struct page *page;

TCSS422: Operating Systems [Fall 2021]

School of Engineering and Technology, University of Washington - Tacoma

November 30, 2021

L15.108

```

107 108

| Keep a single page table for each physical page of memory

| Consider 4GB physical memory

| Using 4KB pages, page table requires 4MB to map all of RAM

| Page table stores

| Which process uses each page

| Which process virtual page (from process virtual address space) maps to the physical page

| All processes share the same page table for memory mapping, kernel must isolate all use of the shared structure

| Finding process memory pages requires search of 2 20 pages

| Hash table: can index memory and speed lookups

| November 30, 2021 | TCSSE22; Operating Systems [Fall 2021] | TCSSE22; Operating Systems [

109 110

112

111

**MULTI LEVEL PAGE TABLE EXAMPLE - 3** Assume each page directory entry (PDE) and page table entry (PTE) requires 4 bytes: • 6 bits for the Page Directory Index (PDI) • 6 bits for the Page Table Index (PTI) • 12 offset bits 8 status bits • (#8) How much total memory is required to index the HelloWorld.c program using a two-level page table when we only need to translate 4 total pages? HINT: we need to allocate one Page Directory and one Page Table.. ■ HINT: how many entries are in the PD and PT TCSS422: Operating Systems [Fall 2021] School of Engineering and Technology, University of Washington - Tacoma November 30, 2021 L15.113

.13