### **ARTICLE IN PRESS**

Available online at www.sciencedirect.com

SCIENCE () DIRECT<sup>®</sup>

Microprocessors and Microsystems xx (xxxx) 1-11

MICROPROCESSORS AND MICROSYSTEMS

www.elsevier.com/locate/micpro

## A 5-10 GHz SiGe BiCMOS FPGA with new configurable logic block

### Chao You<sup>\*</sup>, Jong-Ru Guo, Russell P. Kraft, Michael Chu, Peter Curran, Kuan Zhou, Bryan Goda, John F. McDonald

Rensselaer Polytechnic Institute, CII 6126, 110 8th St., 12180, Troy, NY, USA

Received 18 October 2003; revised 13 February 2004; accepted 14 June 2004

#### Abstract

This paper presents a new multiplexer based FPGA, which can operate at a clock frequency of 5–10 GHz. Redundant switches on the original signal paths are removed improving the performance. The configurable logic blocks (CLBs) power is greatly reduced by using a revised multiplexer structure and turning off unused cells dynamically. More routing capabilities are provided with more inputs/outputs in each direction than similar designs. A chip consisting of four FPGA ring oscillators was fabricated. The Spice simulation results and chip measurements are presented.

© 2004 Published by Elsevier B.V.

*Keywords:* Field programmable gate array; Gate-array; High-performance; Low-power-design; SiGe; Programmable logic array; Reconfigurable-system; Current mode logic

### 1. Introduction

The field programmable gate array (FPGA) consists of an array of configurable logic blocks (CLBs). The user programmable feature of an FPGA makes ASIC design easy and decreases time-to-market. Compared to traditional programmable logic devices (PLDs), FPGAs' configurable logic blocks provide many more functions than PLDs. Different kinds of logic blocks of FPGAs have been studied thoroughly [8]. As shown in [8], a multiplexer based FPGA has better performance than LUT, NAND and AND-OR based FPGAs. One multiplexer based FPGA, the Xilinx XC6200 [4,10], has fallen from favor due to its poor routing capability. This paper brightens the future of multiplexer based FPGAs by converting conventional CMOS multiplexers to BiCMOS multiplexers. A new structure is presented greatly increasing the routing capability. The number of switches on the signal paths is reduced to reduce power and increase performance. With the IBM SiGe 7HP BiCMOS

technology, a measured gate delay of 100 ps is presented in this paper.

A power saving method is utilized to overcome the disadvantage of current mode logic circuits. Unused multiplexers will be turned off to save power. Some new schemes for multiplexers are also provided to save power. The proposed power is less than 10 W with heavily pipelined applications for a  $20 \times 20$  gate array.

The layout of this paper is as follows: Section 2 briefly describes the IBM SiGe BiCMOS 7HP technology and Section 3 presents the structure of this new FPGA. It also introduces a new multiplexer structure, which is used in the design, and a power-saving method that dynamically turns off unused circuits. Section 4 presents circuit simulation and experimental results. Section 5 summarizes the present work and discusses relevant future developments.

### 2. IBM SiGe BiCMOS 7HP technology

This FPGA design is implemented using the IBM SiGe BiCMOS 7HP technology. The technology has all features of Si-base transistors, such as polysilicon base contacts, polysilicon emitter contacts, self-alignment and deep-trench isolation. A linearly graded Ge concentration profile in

<sup>52 \*</sup> Corresponding author. Tel.: +1-518-276-2513; fax: +1-518-276-53 8761.

E-mail address: youc@rpi.edu (C. You).

<sup>55 0141-9331/\$ -</sup> see front matter © 2004 Published by Elsevier B.V.

<sup>56</sup> doi:10.1016/j.micpro.2004.06.008

128

129

139

140

141

142

143

145

161

### **ARTICLE IN PRESS**

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

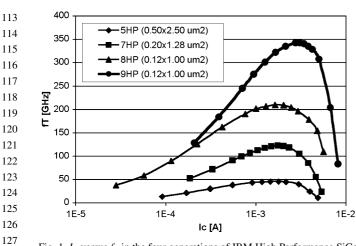

Fig. 1.  $I_{\rm C}$  versus  $f_{\rm T}$  in the four generations of IBM High Performance SiGe BiCMOS process.  $I_{\rm C}$  value for peak  $f_{\rm T}$  is at 0.9 mA.

130 the base region dramatically increases the transistor's 131 performance, such as current gain, early voltage and base 132 transit time [5,6,9]. Fig. 1 shows an  $I_{\rm C}$  and  $f_{\rm T}$  curve in the 133 four generations of IBM High Performance SiGe BiCMOS 134 technology. The peak  $f_{\rm T}$  point of the smallest NPN transistor 135 in 7HP is at 1 mA. Using less current in the collector causes 136 more gate delay in circuits while less power is used. The 137 high-speed 7HP circuits introduced later use 1 mA as the 138 collector current.

### 3. New FPGA structure

#### 144 3.1. New CLB structure

A multiplexer based FPGA has been of interest for a long

time. Several attempts have been made to increase the speed

and routing capability. One gigahertz-FPGA was reported in

Ref. [7]. However, limited routing capability and high

power usage prevent it from being widely used. A better

performing FPGA is highly desirable.

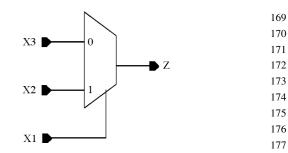

A single 2:1 multiplexer can provide any two-variable

logic function [10]. Table 1 shows sample configurations for

inverter, AND and XOR functions. The corresponding

configurations can be found in Fig. 2.

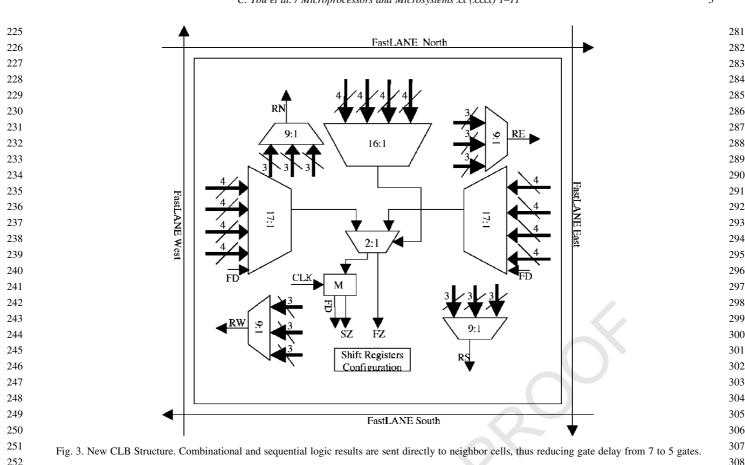

All multiplexer based FPGAs apply this feature of 2:1 multiplexers [7]. Some designs use a 4:1 multiplexer and others use MuxA [10]. Fig. 3 shows a proposed CLB using a 2:1 multiplexer. The 2:1 multiplexer is the core of the function block. It generates combinational logic results

| Function  | X1 | X2         |  |

|-----------|----|------------|--|

| INV       | XX | A0         |  |

| A1 AND B1 | A1 | B1         |  |

| A1 XOR B1 | A1 | <b>B</b> 0 |  |

168 XX, Don't care. '1' is for signal. '0' is for compliment signal.

Fig. 2. 2:1 Multiplexer to implement any two-variable logic function.

(FZ). Sequential logic results (SZ) can be implemented with a master-slave latch (MS-Latch) and a feedback signal (FD) from the MS-Latch back to the input selecting multiplexers. All logic results are sent out to four neighbor cells: north, south, west and east. More routing capabilities are provided by redirecting signals in one direction to another (RW, RE, RS and RN) and a shared bus, FastLANE, which connects four CLBs in the same row or column. The outputs in each direction of a CLB consist of a combinational logic result, a sequential logic result and a redirection signal. The inputs in each direction of a CLB consist of one combinational logic result from a neighbor cell, one sequential logic result from a neighbor cell, one redirection signal and one FastLANE. Three multiplexers select three signals from a total of 16 or 17 inputs and feed them into the core multiplexer. The combinational function of a CLB is determined by the configuration of those input multiplexers (two 17:1 multiplexers and one 16:1 multiplexer).

The inputs of the redirection multiplexers are the inputs 198 of the CLB without FastLANEs and the signal from same 199 direction. For example, the redirection multiplexer facing 200 east does not have the input from east side since getting one 201 signal and routing it back in the same direction wastes 202 routing resources. Comparing this CLB structure with the 203 XC6200 and other multiplexer-based FPGAs [6,10], one 204 can see that the new structure has reduced the gate delay 205 from seven gates to four gates. The new structure does not 206 have CS, PR and 4:1 output multiplexers but still provides 207 more routing capability. For example, one can route the 208 function result to the east neighbor and the south redirection 209 signal to the east simultaneously. 210

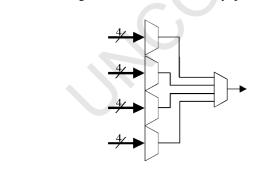

The gate delay of a single level 16:1 multiplexer is larger 211 than a two-level 16:1 multiplexer as shown in Fig. 4 due to 212 high loading. The first level inputs consist of the 16 inputs in 213 four directions. The second level then selects one output 214 from the first level to finish the 16:1 multiplexing function. 215 For the 17:1 multiplexer, the second level multiplexer is 216 implemented with one more input from the feedback signal. 217 The 5:1 multiplexer in the second level will be explained 218 later. 219

### 3.2. New multiplexer design

Besides the new CLB, new multiplexers are used in 223 the design. There are two kinds of traditional multiplexers. 224

220

221 222

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

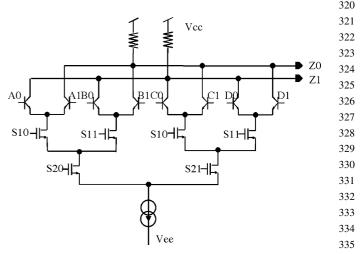

253 One kind of traditional BiCMOS 4:1 multiplexer is shown in 254 Fig. 5. The two-level selection tree of S1, S2 acts as a 255 decoder. Only one BJT pair is selected at a time, permitting 256 the desired signal to pass through. An 8:1 multiplexer can be 257 built with the same style but with a taller current tree. A 258 taller current tree requires a higher voltage supply, which 259 increases total power. Another kind of multiplexer is a 260 bipolar multiplexer similar to the one in the Fig. 5 except the 261 NMOS transistors are replaced by bipolar transistors. The 262 bipolar multiplexer requires a higher voltage supply but has 263 a faster switching speed. In an FPGA design, routing 264 multiplexers only switch during application loading; there-265 fore, the switching speed is not a critical issue. 266

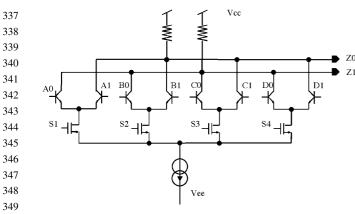

Fig. 6 shows a new 4:1 multiplexer. An additional decoder is needed to select pass-through signals. After configuration, the decoder only permits one select

267

268

269

270

271

272

273

274

275

276

277

278

279

280

Fig. 4. 16:1 Multiplexer utilizing two level multiplexing.

309 bit (S0-S3) to be set. Thus, the corresponding BJT pair is 310 turned on to pass signals through. The decoder can be 311 implemented with CMOS to save power and space. The new 312 multiplexer structure has three advantages: 313

- 1. All multiplexers become single-high multiplexers, which 314 do not require a higher supply voltage. A 16:1 multi-315 plexer uses the same voltage supply as a 2:1 multiplexer. 316

- 2. By resetting all select bits, a multiplexer can be turned 317 off, whereas a traditional multiplexer must always have 318 one current branch on. 319

Fig. 5. Traditional 4:1 multiplexer using a two-level current tree selection. 336

350

351

352

353

354

355

356

357

358

360

# **ARTICLE IN PRESS**

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

Table 2

Fig. 6. New 4:1 multiplexer using single-level current tree selection.

3. In a traditional design, multiplexers have 2-to-*n* inputs since select signals are differential. In the new design, one can implement a multiplexer with any number of inputs, such as 9:1 multiplexers and 17:1 multiplexers as are required in Fig. 3.

### 359 3.3. Multi-mode routing

361 Turning off unused circuits is a common scheme to save 362 power. In this FPGA design, the method is realized 363 dynamically by the loaded user applications. At the chip 364 level, unused CLBs will be turned off to save power. In this 365 design, a Master-Key signal indicates a Mute Mode for the 366 CLB array. An application using one CLB has a 367 configuration pattern to turn off the other 399 CLBs in a  $20 \times 20$  gate array. 368

In a single CLB, there are also unused multiplexers and

output drivers when an application is loaded. Turning off

those circuits saves more power. At the CLB level, the

dynamic routing will be completed as follows: (Output

drivers configuration depends on neighbor cell requirements. It is not listed here.)

- 375 1. Normal mode: when a CLB only uses its combination 376 logic function, the sequential logic circuit (MS-Latch) 377 and all redirection multiplexers may be turned off to save 378 power. Besides sequential logic circuits, more circuits 379 can be turned off in the normal mode. Each CLB needs 380 two signals to generate a logic function. Therefore, at 381 least two output-drivers or two redirection multiplexers 382 in its neighbor cells may be turned off to save power. 383

- 384

385

386

2. Sequential mode: a CLB performs a sequential logic function. The core multiplexer and MS-Latch is turned on. Redirection operation is off.

- 387

38. FastLANE mode: if input signals of a cell are selected

388

389

aneighbor cells may be turned off to save power.

- 390

4. *Redirection mode*: when one cell is configured to redirect

a signal from one neighbor cell to another neighbor cell,

only the redirection multiplexer needs to be turned on.

| Design                   | Core | Latch | Inputs | Redir. | Trees        |

|--------------------------|------|-------|--------|--------|--------------|

| Mute<br>mode             | OFF  | OFF   | OFF    | OFF    | 0            |

| Normal<br>mode           | ON   | ON    | XX     | OFF    | 9            |

| Sequential mode          | ON   | ON    | XX     | OFF    | 11           |

| FastLANE<br>mode         | ON   | XX    | OFF    | OFF    | 3            |

| Redirec-<br>tion<br>mode | OFF  | OFF   | OFF    | ON     | 3/6/<br>9/12 |

| Full mode                | ON   | ON    | ON/XX  | ON/XX  | 21           |

XX, depends on neighbor cell configuration.

Other circuits in the CLB may be turned off to save power.

407

408

409

410

411

412

413

414

415

416

417

418

419

420

421

422

442

443

444

5. *Full mode*: full mode is a very rare situation in an application. When a CLB performs sequential logic and also redirects three signals, the CLB works in Full Mode. All current trees are turned on. (No application can configure all CLBs into Full Mode in a gate array).

With the new features of the multiplexers, decoders of multiplexers may be turned off in order to turn off unused input circuits. Table 2 shows a power estimation of dynamic routing.

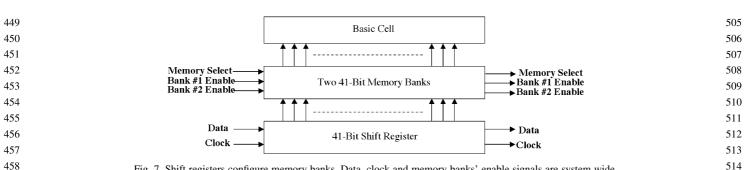

### 3.4. Memory structure

423 A memory configuration structure is used to store user 424 applications and to supply configuration bits to multi-425 plexers. In the previous design, 26 memory bits were used to 426 configure a single cell. A parallel memory configuration 427 structure was used. Memory bits were supplied by a 26-bit 428 wide ribbon cable. In this new design, 41 memory bits are 429 needed to configure a cell. Due to the large number of 430 configuration bits, the parallel configuration is inefficient. 431 Therefore, a shifted register configured memory structure is 432 used to configure memories. 433

Fig. 7 shows a shift register configured memory 434 configuration structure. Two memory banks are utilized in 435 this design to implement the FPGA with two personalities. 436 Each personality might load one application at a time. The 437 two banks' enable signals are used to switch between 438 personalities. One clock signal is used to shift memory data. 439 The memory banks' enable, data and clock signal are system 440 signals routed to every single cell in a gate array. 441

### 3.5. Overall performance

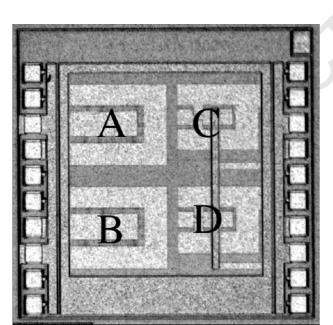

The layout and component list of this newly designed 445 basic cell structure are shown in Table 3 and Fig. 8. A single 446 basic cell layout is approximately 180 by  $200 \,\mu\text{m}^2$  with 447 memory configuration structures. 448

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

Fig. 7. Shift registers configure memory banks. Data, clock and memory banks' enable signals are system wide.

460 The new structure has several advantages over similar designs [2]. Instead of sending only one output to a neighbor 461 cell in one direction, the new structure sends out three 462 outputs to a neighbor cell in one direction. 463

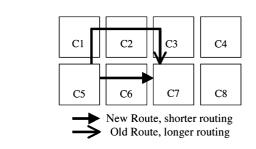

The first advantage is the improved routing capability. 464 One of the examples is shown in Fig. 9. C5's logic 465 function result is required by C7, but C6 also has a logic 466 function result required by C7. In the old CLB, routing is 467 468 forced to go from C1-C2, from C2-C3 and then from C3-469 C7. In the new CLB, routing can be taken through C6 470 since both a logic function result and a redirection function can be routed east. 471

472 The second advantage over the previous design is its better performance. The new structure has only two 473 474 multiplexers on the input paths of the core 2:1 multiplexer. 475 There are no switches or multiplexers on the output paths. 476 Switches on signal paths are minimized to provide the best 477 performance that a multiplexer based FPGA can have. There are only three gate delays through a CLB and there 478 479 are no interconnect switches. This is why multiplexer based 480 FPGAs perform better than other FPGA structures.

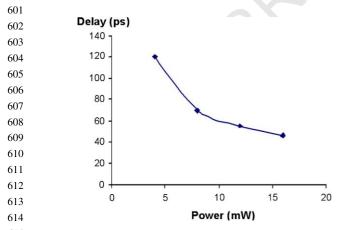

Another advantage of this new design is the reduced 481 482 power consumption. The power usage of the full FPGA chip is reduced. A lower voltage supply is possible due to the use 483 of single high multiplexer CML trees. Unused CLBs and 484 485 circuits are turned off as needed by individual loaded applications. Power can be further reduced by supplying less 486 current in each CML current tree with a trade-off of 487 performance. A power and delay table is presented for 488 comparison with similar designs. Fig. 10 and Table 4 show a 489 power and performance trade-off diagram. 490

#### 492 3.6. Testing plan

491

493

494

495

496

The final goal of this project is to design a  $48 \times 48$  or large gate array with clock frequency from 5 to 20 GHz. The project has the following testing strategy:

- 497 1. Single cell test: one single cell chip was fabricated in 498 2000 to test the functionality, BiCMOS multiplexer 499 design, chip's performance and the memory structure. 500 The testing results are presented in [2]. 501

- 2. Power and performance test: once functionality, the 502 BiCMOS multiplexers and the memory structure were 503 tested, a chip containing more cells will be tested for 504

lower power and higher performance ideas. The chip, 516 including ring-oscillators, is fabricated with the IBM 517 7HP BiCMOS technology. The testing results are 518 detailed in Section 3.7. 519

5

515

520

| Table 3             |  |

|---------------------|--|

| Chip component list |  |

| Chip componer       | nt list                                                                                                                                                                                        |   |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Label               | Component                                                                                                                                                                                      | _ |

| A                   | West redirection multiplexer                                                                                                                                                                   |   |

| B                   | South redirection multiplexer                                                                                                                                                                  |   |

| C                   | 17:1 Multiplexer                                                                                                                                                                               |   |

| D<br>E              | 17:1 Multiplexer                                                                                                                                                                               |   |

| E<br>F              | 16:1 Multiplexer<br>North redirection multiplexer                                                                                                                                              |   |

| г<br>G              | East redirection multiplexer                                                                                                                                                                   |   |

| H                   | 2:1 multiplexer and drivers                                                                                                                                                                    |   |

| I                   | Output drivers                                                                                                                                                                                 |   |

| J                   | Master-Slave latch                                                                                                                                                                             |   |

| K                   | Memory configure system                                                                                                                                                                        |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

|                     | aler lygerti en ann lee i yn lygel tael tae apart i yn lygert i ar fri fan i far 'i lyger lyne yn gyne.<br>A ganne mi'n af an an a an ar an ar an ar an ar |   |

| C Distantia         |                                                                                                                                                                                                |   |

| a subtraction state |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

| C FIRE DATE THE     | and a second                                                                                 |   |

| THE REPORT OF       |                                                                                                                                                                                                |   |

|                     |                                                                                                                                                                                                |   |

559 Fig. 8. Basic cell layout. The size of a single cell is  $178 \times 203 \,\mu\text{m}^2$ . The corresponding list is in Table 3. 560

# **ARTICLE IN PRESS**

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

Fig. 9. Comparison between two routing method. New basic cell structure has obvious advantages over the old cell structure.

Scalable gate array test: when the single cell performances and power consumption met scalable criteria, i.e. low power, high-speed, good routing capability, etc. a larger gate array was implemented. Due to space limitations, only a 20×20 gate array was submitted for fabrication with the IBM 7HP BiCMOS process in July 2003.

The testing plan is simulated with IBM SiGe 7HP 580 models. The models have been updated several times 581 since it's first released. Most parameters of the models 582 agree with measurement with little deviation. As shown 583 in later part of this paper, the maximum difference 584 between simulation and physical measurement is 15%. 585 Therefore, the simulated results can partially be used as 586 evidence of circuits' performance. 587

### 3.7. 20×20 Gate array

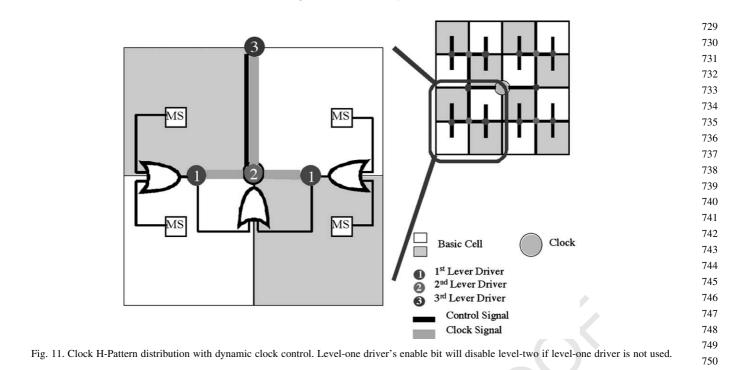

The  $20 \times 20$  gate array is an important milestone in the project. Two important issues in this chip are clock distribution and system wide memory configuration.

Clock tree distribution is implemented by an H-Pattern.

To save power on the clock trees, a multi-mode routing idea

is deployed as shown in Fig. 11. Each high-speed clock

driver has an enable bits to turn it on/off. Since the MSLatch is the only circuit in a cell that needs clock signal,

Fig. 10. FPGA Power-Delay trade-off in the IBM 7HP BiCMOStechnology.

| Design                     | Current (mA) | Power (mW) | Delay (ps) |

|----------------------------|--------------|------------|------------|

| Similar struc-<br>ture [2] | 0.6          | 53         | 80         |

| New structure              | 0.8          | 16         | 46         |

|                            | 0.6          | 12         | 55         |

|                            | 0.4          | 8          | 70         |

|                            | 0.2          | 4          | 120        |

An AND gate is simulated for design comparison. Similar structure does not have the dynamic routing feature.

626

627

657

658

659

660

661

662

663

664

628 the MS-Latch's control bit might be used to turn on/off the 629 clock drivers. The second level clock driver enable bits are 630 controlled by the first level drivers. Upper level clock 631 drivers use the same scheme. If one MS-Latch requires a 632 clock, the cell will turn on all the clock drivers on the path to 633 reach the clock source. Otherwise, the MS-Latch votes to 634 turn off clock drivers to save power. Such a clock 635 distribution scheme guarantees the clock signal reaches 636 each cells without clock skew and delivers the clock signal 637 to the cells needing it. No clock drivers' power and dynamic 638 power is wasted. 639

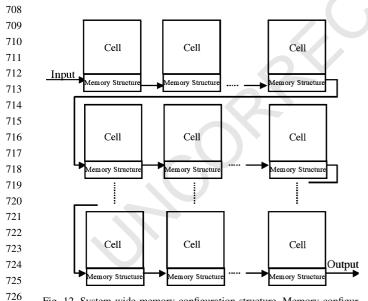

The system wide memory configuration structure is 640 consistent with the single cell memory configuration 641 structure. Fig. 12 shows the system wide structure. As 642 described previously, a cell's memory configuration 643 structure uses the serial input of shift registers to provide 644 parallel inputs to the memories. Each cell's input and 645 output might be connected as follows to provide system 646 wide distribution. 647

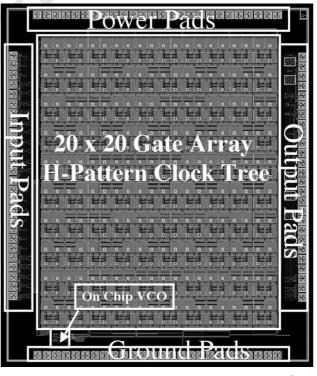

The following Fig. 12 shows a  $5 \times 5 \text{ mm}^2$ ,  $20 \times 20$  gate 648 array layout that has been submitted for fabrication. The 649 input pads include input drivers for memory configuration, 650 external system clock, and external inputs. The output pads 651 include output drivers for memory configuration output for 652 verification purpose, and outputs from the FPGA. System 653 clock is provided by an on-chip VCO and external system 654 clock. A user can specify which clock he wants to use via a 655 high-speed 2:1 multiplexer. 656

In the 7-metal layer IBM 7HP BiCMOS technology, the first three metal layers are used for cell interconnection. Two metal layers are used for clock distribution. Two metal layers are used to supply power.

#### 4. Circuit simulation and chip measurement results

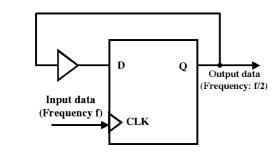

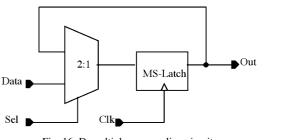

An FGPA can load various applications to prove its functionality and performance. In this paper, a clock divider circuit and a demultiplexer is simulated to test speed and functionality (Fig. 13). 668

A clock divider is a very simple circuit to find the 669 maximum operation frequency of a circuit. A circuit is 670 shown in Fig. 14, a buffer is implemented in the basic cell 671 and supplies data to the Master–Slave Latch. If the input 672

6

561 562

563 564 565

566 567

568 569

570

571

588

589

590

591

592

593

## ARTICLE IN PRESS

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

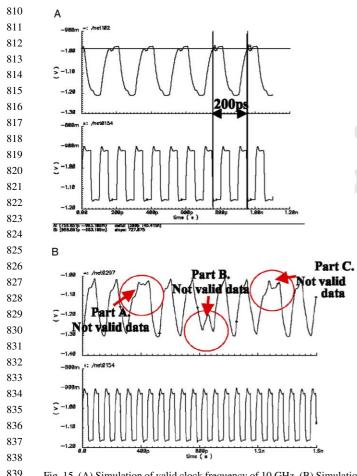

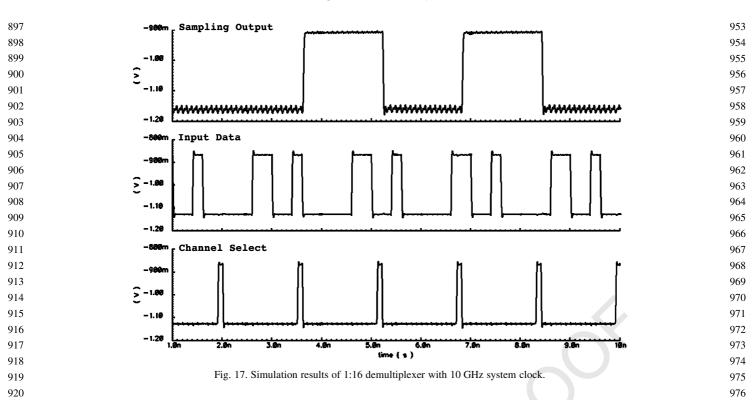

clock is less than the maximum operation frequency, the circuit will operate correctly by outputting half the frequency of the input clock. Otherwise, the output data will be invalid. Fig. 15A and B show a simulation result of the clock divider. In Fig. 15A, the input clock has a frequency of 10 GHz and the output shows a 5 GHz clock signal. In Fig. 15B, the input clock has a frequency of 13.5 GHz and the output shows several invalid voltages, which indicate that the clock frequency has exceeded circuit capability.

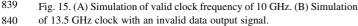

A demultiplexer is used in serial-deserial circuits to decode and distribute a transmission channel to different

Fig. 12. System wide memory configuration structure. Memory configuration inputs are serially connecting to each cell. The simulation memory configuration load-time is 4 ms for  $20 \times 20$  gate array.

channels. Fig. 16 shows a sampling single cell circuit used in the demultiplexer. The DATA is connected to the transmission channel. The SEL is connected to a 4-bit barrel counter, which has half the clock frequency of the system clock. In a 1:16 demultiplexer, 16 sampling cells will be connected in parallel. The barrel counter will enable one SEL at a time and shift to the next sample cell

Fig. 13. Submitted  $20 \times 20$  gate array chip. Chip size  $5 \times 5$  mm<sup>2</sup>.

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

Fig. 14. Clock divider to obtain maximum operation frequency.

after one clock cycle. When the SEL is enabled, 796 the DATA will be latched in the MS-latch. When the SEL is disabled, the DATA will be held at the MSlatch by selecting the feedback. If needed, another pipelined buffer circuit can follow the output and hold 800 the result. Fig. 17 shows a simulation result with a 10 GHz system clock. 802

The new multiplexer based FPGA has shorter gate 803 delays, reduced power usage and more routing capability 804 than similar multiplexer based FPGA designs. To demon-805 806 strate the advantages of the new FPGA structure, a chip was fabricated in June 2002. This test chip utilizes IBM's 808 SiGe BiCMOS 7HP technology. Four hardware configured

Fig. 16. Demultiplexer sampling circuit.

FPGA ring oscillators are built to demonstrate the performance in a  $2 \times 2 \text{ mm}^2$  area. The layout of the chip is shown in Fig. 18.

The two left ring oscillators in Fig. 18 (A and B) are 855 high speed FPGAs with gate delay of 100 ps. The left 856 bottom oscillator has diodes on the current tree to 857 prevent collector-emitter breakdown. The two right ring 858 oscillators (C and D) are low power FPGAs with gate 859 delay of 250 ps. The right bottom oscillator also has 860 diodes on the current trees to prevent collector-emitter 861 breakdown. A waveform of the high-speed ring oscillator 862 is shown in Fig. 19. The measurement is taken at 20 °C. The voltage supply is 2.5 V. The output voltage swing is 400 mV.

### 4.1. Performance measurement discussion

Spice simulations for the high-speed oscillators show a clock period of 680 ps. The frequency of oscillation is defined by Eq. (1).

$$=\frac{1}{2 \cdot N \cdot T}$$

(1) 873

874

where T is the gate delay through the CLB. From our 875 simulation results, each CLB has a gate delay of 85 ps. The 876 measured high-speed oscillator in Fig. 19 shows a clock 877 period of approximately 800 ps, and a CLB gate delay of 878 100 ps. For the similar designs, the estimated gate delay 879 ranges from 120 to 150 ps at a considerable power 880 consumption. The difference between simulation and 881 measurement is due to wire resistance, parasitic capacitance 882 and circuit parasitic capacitance. 883

#### 4.2. Power measurement discussion

The chip contains 12 pad drivers, five divide-by-eight 887 circuits, one divide-by-two circuit, two high-speed FPGA 888 ring oscillators, two low-power FPGA ring oscillators 889 and one regular ring oscillator. Pad drivers, divide 890 circuits and high-speed FPGA ring oscillators utilize a 891 2.5 V power supply. The regular ring oscillator and low-892 power FPGA ring oscillators utilize a 2.0 V power 893 supply. A 2.5 V power supply feeds the west side of 894 the chip and a 2.0 V power supply feeds the east side of 895 the chip. To power up the high-speed FPGA ring 896

8

785

786

787

788

789

790

791

792

793

794

795

797

798

799

801

807

809

850

851

852

853

854

841

842

843

844

845

863 864

865 866

867

868 869 870

871 872

884

885

## **ARTICLE IN PRESS**

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

921 oscillators, the power supply is solely needed on the west

922 side of the chip. To power up the low-power FPGA ring

923 oscillators and CML ring oscillator, a 2.5 V power

924 supply is needed on the west side for all pad drivers and

925 divide circuits and a 2.0 V power supply is needed on

926 the east side. Table 5 shows the designed power

927 consumption of this chip.

For the two high-speed oscillators, the predicted power 977 consumption is 848 mW for a 2.5 V power supply with 978 339 mA total current. The measured power supply voltage is 979 2.5 V when the ring oscillator starts to oscillate. 980

Fig. 18. Microphotograph of the IBM 7HP BiCMOS chip layout. (A) 4-Stage ring oscillator. (B) 4-Stage ring oscillator with diodes on the current trees. (C) 4-Stage low-power ring oscillator. (D) 4-Stage low power ring oscillator with diodes on the current trees. Chip size:  $2 \times 2 \text{ mm}^2$ .

Fig. 19. Chip gate delay measurement screen capture. The high-speed ring1007oscillator proves a gate delay as short as 100 ps.1008

# RTICLE IN PRE

C. You et al. / Microprocessors and Microsystems xx (xxxx) 1-11

Table 5 1009

| 1010 | Current | in each | fabricated | component |

|------|---------|---------|------------|-----------|

|------|---------|---------|------------|-----------|

| Circuit       | Current (mA) | Number | Total (mA) |

|---------------|--------------|--------|------------|

| Pad driver    | 17.00        | 12     | 204.00     |

| Divide-by-2   | 1.23         | 1      | 1.23       |

| Divide-by-8   | 3.69         | 5      | 18.45      |

| High-speed RO | 57.44        | 2      | 114.88     |

| Low-power RO  | 6.476        | 2      | 12.952     |

| CML RO        | 10.53        | 1      | 10         |

RO stands for ring oscillator. 1018

1019

1020

1021 The measured current ranges from 258 to 295 mA. The 1022 reduced current draw is due to the voltage drop over the 1023 power rails and resistive losses on the cable.

1024 1025 1026

1028

#### 1027 5. Conclusion and future work

1029 This paper presents a novel multiplexer based 1030 FPGA. Compared to a similar previous design, this new 1031 design has better performance, lower power usages and 1032 better routing capability. Implemented in IBM's SiGe 1033 BiCMOS 7HP technology, the measured gate delay is 1034 100 ps. Power usage is 10 mW per CLB or less.

1035 A larger  $20 \times 20$  gate array has been shipped 1036 for fabrication. The larger gate array will 1037 target wider applications with a system clock up to 1038 10 GHz. The power usage is less than 20 W for the 1039 entire chip. 1040

Further developments include improving routing capa-1041 bilities and adding more functionality into the CLB. 1042 Routing capabilities can be improved further by routing 1043 the FastLANE with the redirection multiplexer. The 1044 functionality of the CLB can be improved by adding a 1045 high-speed CML adder circuit. The adder function is 1046 widely used in digital signal processing. The extra adder 1047 in the CLB will reduce the number of cells used by such 1048 applications. 1049

1050

1051 1052

#### Acknowledgements 1053

1054

1064

This work was supported by the United States Army and 1055 Nation Science Foundation (NSF) at contract number ECS-1056 9980251 from 1999 to 2002 and Defense Advanced 1057 Research Project Agency (DARPA) at contract number 1058 #N66001-02-1-8919 since August, 2002. The first chip was 1059 fabricated with the financial support of Sierra Monolithics. 1060 1061 The second and third chips were fabricated with the financial support of DARPA. Special thanks are extended 1062 to Robert W. Heikaus. 1063

### References

[1] A. El Gamal, An architecture for electrically configurable gate array, 1067 IEEE J Solid-State Circuits 24 (2) (1989) 394-398. 1068

1065

1066

1072

1073

1085

1086

1087

1088

1089

1090

1091

1092

1093

1094

1095

1096

1097

1098

1099

1100

1101

1102

1103

1104

1105

1106

1107

1108

1109

1110

1111

1112

1113

1114

1115

1116

1117

1118

- [2] B.S. Goda, J.F. McDonald, S.R. Carlough, T.W. Krawczyk Jr., 1069 R.P. Kraft, SiGe HBT BiCMOS FPGAs for fast reconfigurable 1070 computing, IEE Proc. Comput. Digital Techniq. 147 (3) (2000) 189-194 1071

- [3] B.S. Goda. SiGe HBT BiCMOS Field Programmable Gate Arrays for Fast Reconfigurable Computing, Doctoral Thesis, 2001

- [4] Configurable Cellular Array, US Patent, US5491353, 1996.

- 1074 [5] G. Freeman, M. Meghelli, Y. Kwark, S. Zier, A. Rylyakov, 1075 M.A. Sorna, T. Tanji, O.M. Schreiber, K. Walter, R. Jae-Sung, B. Jagannathan, A. Joseph, S. Subbanna, 40 Gbit/s circuits built from 1076 a 120 GHz fT SiGe technology, IEEE J. Solid-State Circuits 37 (9) 1077 (2002) 1106-1114. 1078

- [6] IBM SiGe Designer's manual, IBM Inc., Burlington Vermont. 1079 2001

- 1080 [7] J. Birkner, A Very High-speed Filed Programmable Gate Array Using Metal-to-metal Anti-fuse Programmable Elements, CICC '91 1081 introduction. 1082

- [8] S. Singh, J. Rose, P. Chow, D. Lewis, The effect of logic block 1083 architecture on FPGA performance, IEEE J. Solid-State Circuits 27 1084 (3) (1992) 281-287.

- [9] T.H. Ning, History and future perspective of the modern silicon bipolar transistor, IEEE Trans. Electron Dev. 48 (11) (2001) 2485-2491.

- [10] Xilinx XC6200, User Guide, Xilinx Inc., San Jose, CA, 1997.

Chao You (S'02-presnet) received the B.S. degree in Physics from Nankai University, Tianjin, China, in 1999 and the MS degree in Electrical Engineering from Rensselaer Polytechnic Institute, Troy, New York, in 2003. He is currently a doctoral candidate in Electrical Engineering in Rensselaer Polytechnic Institute. His research interests are concentrated on integrated circuit design of high speed Field Programma-

ble Gate Array (FPGA) and Serializer/Deserializer (SERDES). His research interest also includes high performance analog circuit and mixed-signal circuits.

Jong-Ru Guo received MS degree in electronic Engineering and Electrical Engineering from the National Tsing Hua University, Hsin-Chu, Taiwan, R.O.C. After graduating from NTHU; he served his mandatory military service as 2nd lieutenant of communication center in Taiwanese Department of Defense. He joined TSMC as a process integration engineer after his military obligations. He has worked in communi-

cation circuitry designs in Ben-Q as a circuit designer. He is currently pursuing his PhD degree at Rensselaer Polytechnic Institute, Troy, NY. His research interests include the high-speed circuits and configurable systems.

## **ARTICLE IN PRESS**

1172

1173

1174

1175

1176

**Russell Kraft** received a BSEE degree in 1976, an MSEE degree in 1978, and a PhD in 1983, all from Rensselaer Polytechnic Institute, Troy, New York. His dissertation was on the optimization of phased ultrasonics and radar arrays for steering by nonlinearly adjusting the element gains and phases. In 1986, he joined the Center for Manufacturing Productivity at Rensselaer Polytechnic Institute as a project manager and adjunct

faculty. The research group is now known as the Center for Integrated Electronics & Electronics Manufacturing. His research areas include electronic manufacturing, robotics, metrology, inspection, and fast digital IC design and his teaching responsibilities include control and communication laboratory applications and computer integrated manufacturing systems. In 1983, he was a Sr Controls Engineer at Mechanical Technology Inc., Latham, NY where he developed vision based inspection and gaging systems and real-time imbedded combustion controls for automotive and generator stirling engines. Dr Kraft is a member Eta Kappa Nu, Tau Beta Pi, Sigma Xi and the Machine Vision Association of SME. He is a technical reviewer for the IEEE Transactions on Components, Packaging, and Manufacturing Technology - Part C. He has two patents in the computer-vision area for non-contact gauging and is co-author of several publications in high-speed digital design, vision inspection, phased array design, homomorphic signal processing and control system design.

Michael Chu received the BS degree in electrical and computer systems engineering from Rensselaer Polytechnic Institute, Troy, NY, in 1997. Currently, he is a research assistant with Rensselaer Polytechnic Institute, working toward the PhD degree in electrical engineering. His research interests include high-speed data conversion techniques, as well as mixed signal and Field Programmable Gate Array design.

**Peter F. Curran** was born in Queens, NY, in 1964. He received a BSEE degree in 1993 from Rensselaer Polytechnic Institute, Troy, New York and is pursuing his PhD there as well. His research involves high-speed bipolar circuits for communications and computation. He is a student member of the IEEE and ACM.

Mr Kuan Zhou received the B.S. degree in automatic control from Huazhong University of Science & Technology, P.R. China in 1996 and the MS from Chinese Academy of Sciences respectively. He is now a PhD candidate in Electrical, Computer and Systems Engineering department at Rensselaer Polytechnic Institute, Troy, NY. He is now involved in high-speed VLSI system design. He is the 2003 winner of Rensselaer Founder's

Award for Excellence. His research interests include high performance mixed-signal system design. He and his research partners have designed some GHz FPGAs.

**Bryan S. Goda** is an Associate Professor in the Department of Electrical Engineering and Computer Science. He holds a BSc in both Electrical Engineering and Computer Science from United States Military Academy, a MSc in Electrical Engineering from the University of Colorado, Boulder and a Ph.D. in Electrical Engineering from Rensselaer Polytechnic Institute. He is a US Army Colonel and is on the permanent faculty.

John F. McDonald (M'65-SM'01) was born in 1942 in Narberth, PA. He received the B.S.E.E. degree in 1963 from the Massachusetts Institute of Technology (M.I.T.), Cambridge, and the M.Eng and the PhD degree in engineering and applied science from Yale University, New Haven, CT, in 1965 and 1969, respectively. He served as a Member of the Technical Staff with Bell Labs in 1964. He was an Instructor at Yale in 1969, and Assistant

Professor the following year. In 1974, he joined the faculty at Rensselaer Polytechnic Institute, Troy, NY, in the Department of Electrical, Computer and Systems Engineering, as Associate Professor. He was made Full Professor in 1985. His background includes a wide range of topics including communication theory and DSP, computer hardware design, focused electron and ion beam systems, HF and MCM packaging, GaAs/AlGaAs HBT RISC processor design, HBT technology, and VLSI design and design automation. His current interests are concentrated on SiGe HBT BiCMOS circuit design and VLSI interconnection technology. He has coauthored 220 refereed articles, roughly one third of which are archival journal articles. He has been awarded ten patents. 1177

1178

1179

1180

1181

1182

1183

1184

1185

1186

1187

1188

1189

1190

1191

1192

1193

1194

1195

1196

1197

1198

1199

1200

1201

1202

1203

1204

1205

1206

1207

1208

1209

1210

1211

1212

1213

1214

1215

1216

1217

1218

1219

1220

1221

1222

1223

1224

1225

1226

1227

1228

1229