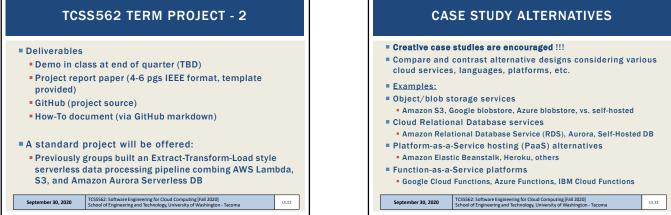

| CA                                                                                                                              | SE STUDY ALTERNATIVES                                         |  |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

| Creative case                                                                                                                   | studies are encouraged !!!                                    |  |

| <ul> <li>Compare and contrast alternative designs considering various<br/>cloud services, languages, platforms, etc.</li> </ul> |                                                               |  |

| Examples:                                                                                                                       |                                                               |  |

| Object/blob s                                                                                                                   | torage services                                               |  |

| Amazon S3, 0                                                                                                                    | Google blobstore, Azure blobstore, vs. self-hosted            |  |

| Cloud Relatio                                                                                                                   | nal Database services                                         |  |

| Amazon Rela                                                                                                                     | tional Database Service (RDS), Aurora, Self-Hosted DB         |  |

| Platform-as-a                                                                                                                   | -Service hosting (PaaS) alternatives                          |  |

| Amazon Elas                                                                                                                     | tic Beanstalk, Heroku, others                                 |  |

| Function-as-a                                                                                                                   | Service platforms                                             |  |

| Google Cloud                                                                                                                    | Functions, Azure Functions, IBM Cloud Functions               |  |

| C                                                                                                                               | TCSS562: Software Engineering for Cloud Computing [Fall 2020] |  |

Slides by Wes J. Lloyd

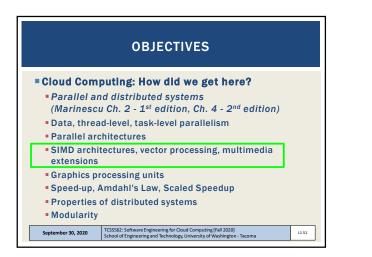

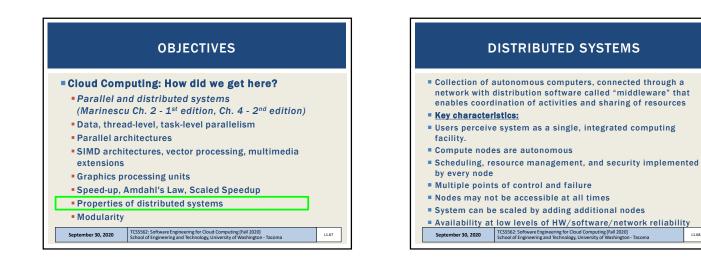

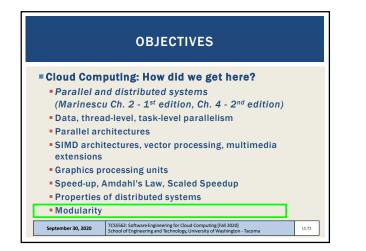

| OBJECTIVES                                                                                                                                                  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

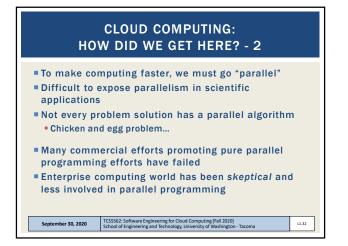

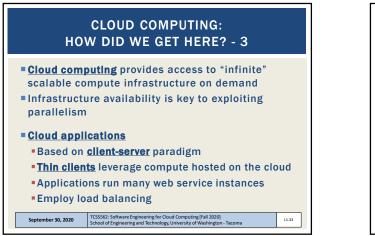

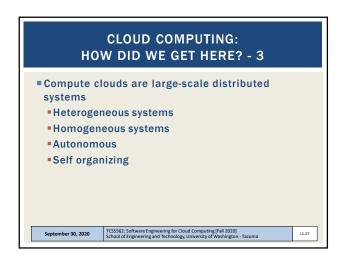

| Cloud Computing: How did we get here?                                                                                                                       |  |

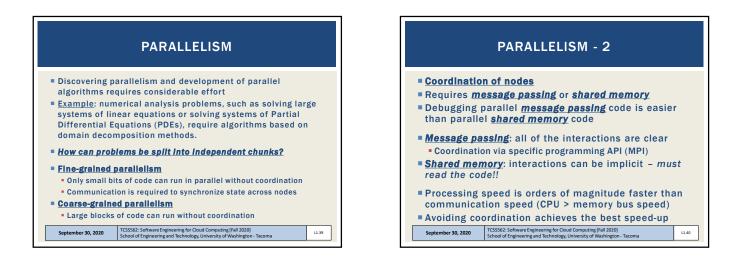

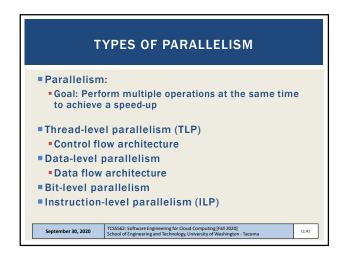

| Parallel and distributed systems                                                                                                                            |  |

| (Marinescu Ch. 2 - 1 <sup>st</sup> edition, Ch. 4 - 2 <sup>nd</sup> edition)                                                                                |  |

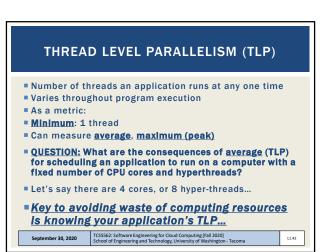

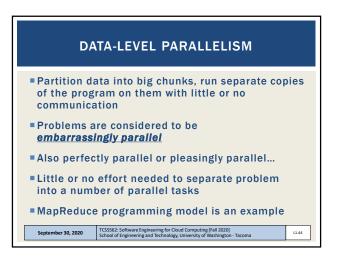

| Data, thread-level, task-level parallelism                                                                                                                  |  |

| Parallel architectures                                                                                                                                      |  |

| <ul> <li>SIMD architectures, vector processing, multimedia<br/>extensions</li> </ul>                                                                        |  |

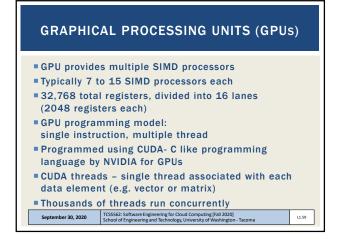

| <ul> <li>Graphics processing units</li> </ul>                                                                                                               |  |

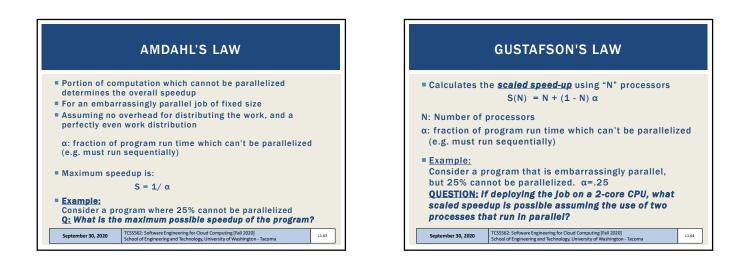

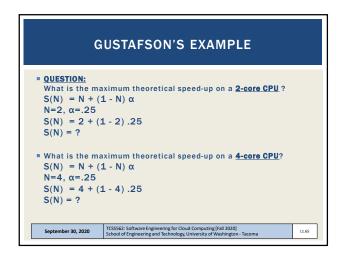

| Speed-up, Amdahl's Law, Scaled Speedup                                                                                                                      |  |

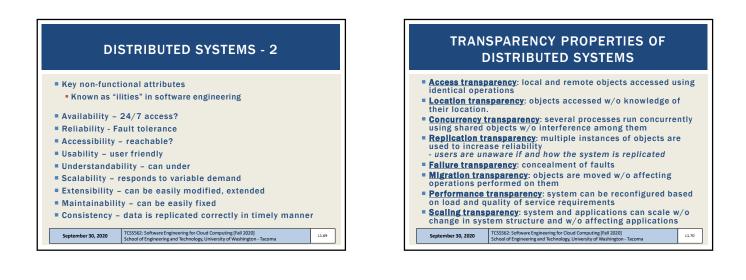

| Properties of distributed systems                                                                                                                           |  |

| <ul> <li>Modularity</li> </ul>                                                                                                                              |  |

| September 30, 2020 TCSS562: Software Engineering for Cloud Computing [Fall 2020]<br>School of Engineering and Technology, University of Washington - Tacoma |  |

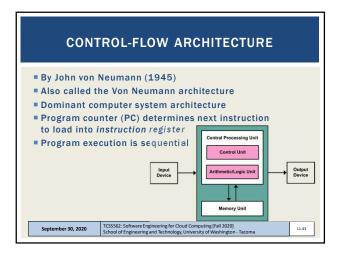

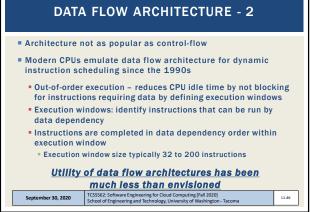

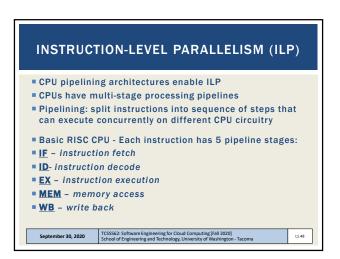

## DATA FLOW ARCHITECTURE Alternate architecture used by network routers, digital signal processors, special purpose systems Operations performed when input (data) becomes available Envisioned to provide much higher parallelism Multiple problems has prevented wide-scale adoption data dependency Efficiently broadcasting data tokens in a massively parallel system execution window Efficiently dispatching instruction tokens in a massively parallel system Building content addressable memory large enough to hold all of the dependencies of a real program TCSS562: Software Engineering for Cloud Computing [Fall 2020] School of Engineering and Technology, University of Washington - Tacoma September 30, 2020 L1.45 September 30, 2020

## **BIT-LEVEL PARALLELISM** Computations on large words (e.g. 64-bit integer) are performed as a single instruction Fewer instructions are required on 64-bit CPUs to process larger operands (A+B) providing dramatic performance improvements Processors have evolved: 4-bit, 8-bit, 16-bit, 32-bit, 64-bit QUESTION: How many instructions are required to add two 64-bit numbers on a 16-bit CPU? (Intel 8088) 64-bit MAX int = 9,223,372,036,854,775,807 (signed) 16-bit MAX int = 32,767 (signed) Intel 8088 - limited to 16-bit registers TCSS562: Software Engineering for Cloud Computing [Fall 2020] School of Engineering and Technology, University of Washington - Tacoma L1.47 September 30, 2020

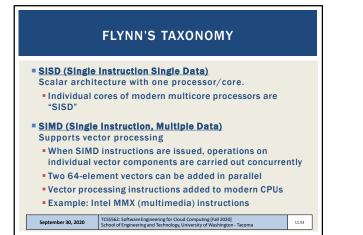

## (SIMD): VECTOR PROCESSING ADVANTAGES

- Vectors architecture provide vector registers that can store entire matrices into a CPU register

- SIMD CPU extension (e.g. MMX) add support for vector operations on traditional CPUs

- Vector operations reduce total number of instructions for large vector operations

- Provides higher potential speedup vs. MIMD architecture

- Developers can think sequentially; not worry about parallelism

September 30, 2020 TCSS562: Software Engineering for Cloud Computing [Fall 2020] School of Engineering and Technology, University of Washington - Tacom

L1.54

|                                                      | OBJECTIVES                                                                                                                               |       |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Cloud Com                                            | puting: How did we get here?                                                                                                             |       |

| Parallel an                                          | nd distributed systems                                                                                                                   |       |

|                                                      | u Ch. 2 - 1 <sup>st</sup> edition, Ch. 4 - 2 <sup>nd</sup> edition)                                                                      |       |

| Data, threa                                          | d-level, task-level parallelism                                                                                                          |       |

| Parallel arc                                         | chitectures                                                                                                                              |       |

| <ul> <li>SIMD archite</li> <li>extensions</li> </ul> | tectures, vector processing, multimedia                                                                                                  |       |

| Graphics pr                                          | rocessing units                                                                                                                          |       |

| Speed-up, A                                          | Amdahl's Law, Scaled Speedup                                                                                                             |       |

| Properties                                           | of distributed systems                                                                                                                   |       |

| Modularity                                           |                                                                                                                                          |       |

| September 30, 2020                                   | TCSS562: Software Engineering for Cloud Computing [Fall 2020]<br>School of Engineering and Technology, University of Washington - Tacoma | L1.60 |

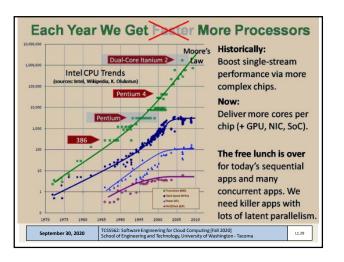

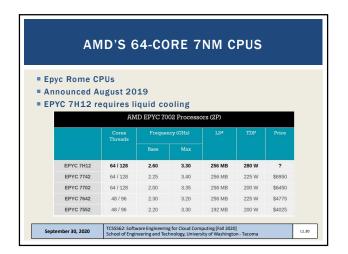

|                                                                           | MOORE'S LAW                                                                                                                                                                                 |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>CPUs now hav</li> <li>Power dissipative removal chall</li> </ul> | n a chip doubles approximately every 1.5 years<br>re billions of transistors<br>tion issues at faster clock rates leads to heat<br>enges<br>m: increasing clock rates → to adding CPU cores |

| same comput                                                               | <b>re processor</b> – multi-core CPU, all cores have the<br>ational resources and speed<br><u>ore processor</u> – on a multi-core CPU, some cores<br>sources and speed                      |

| be dynamical                                                              | processor – processing resources and speed can<br>ly configured among cores<br>asymmetric processors offer a higher speedup                                                                 |

| September 30, 2020                                                        | TCSS562: Software Engineering for Cloud Computing [Fall 2020]<br>School of Engineering and Technology, University of Washington - Tacoma                                                    |

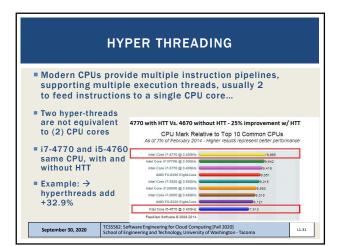

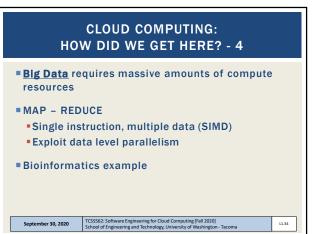

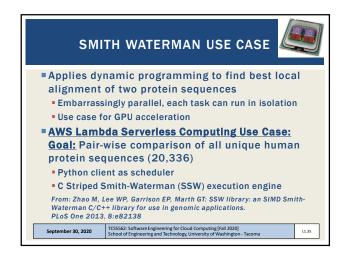

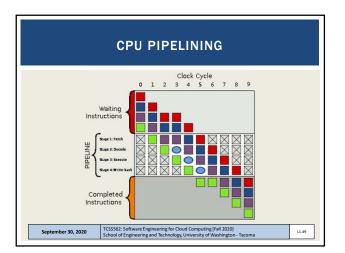

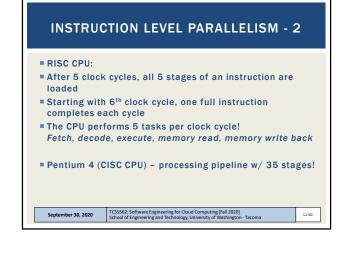

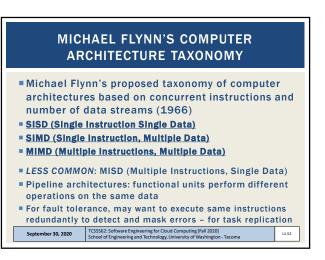

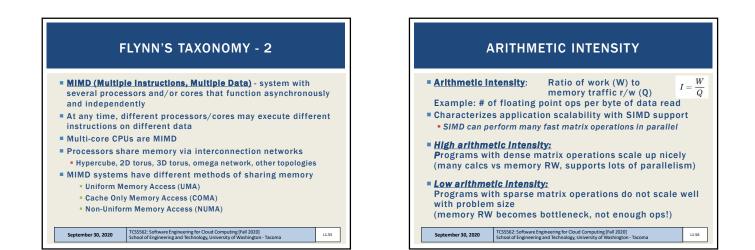

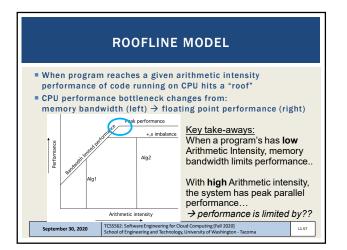

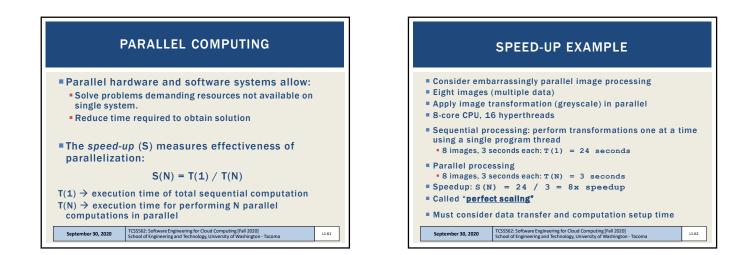

## CLOUD COMPUTING - HOW DID WE GET HERE? CLOUD COMPUTING - HOW DID WE GET HERE? SUMMARY OF KEY POINTS **SUMMARY OF KEY POINTS - 2** Multi-core CPU technology and hyper-threading Bit-level parallelism What is a Instruction-level parallelism (CPU pipelining) Heterogeneous system? Flynn's taxonomy: computer system architecture classification • SISD - Single Instruction, Single Data (modern core of a CPU) Homogeneous system? • SIMD - Single Instruction, Multiple Data (Data parallelism) Autonomous or self-organizing system? • MIMD - Multiple Instruction, Multiple Data Fine grained vs. coarse grained parallelism • MISD is RARE; application for fault tolerance... Parallel message passing code is easier to debug than shared memory (e.g. p-threads) Roofline model: Know your application's max/avg Thread Level Memory bottleneck with low arithmetic intensity Parallelism (TLP) Data-level parallelism: Map-Reduce, (SIMD) Single

Instruction Multiple Data, Vector processing & GPUs

September 30, 2020

TCSSS62: Software Engineering for Cloud Computing (Tall 2020)

School of Engineering and Technology, University of Washington - Tacoma