**OBJECTIVES - 10/5** Questions from 10/3 Tutorial 0, Tutorial 1, Tutorial 2 Cloud Computing - How did we get here? (Marinescu Ch. 2 - 1st edition, Ch. 4 - 2nd edition) ■ Class Activity 1 - Implicit vs Explicit Parallelism SIMD architectures, vector processing, multimedia Graphics processing units Speed-up, Amdahl's Law, Scaled Speedup ■ Properties of distributed systems Modularity October 5, 2023 L3.2

1

FEEDBACK FROM 10/3 Parallelism and parallel algorithms Example: Merge sort divides an unsorted list into the smallest possible sub-lists, compares them with the adjacent lists, and merges in a sorted order As the data is divided, operations can be made in parallel because they are independent The execution starts sequential, becomes increasingly parallel, and finishes as sequential Finding parallel algorithms often requires a "trick" or symmetry to enable parallelism October 5, 2023 L3.4

5

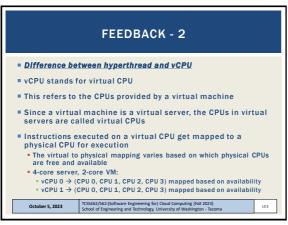

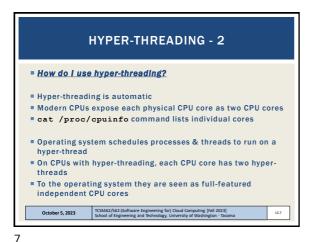

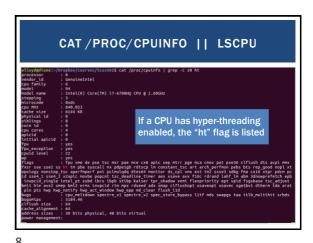

**HYPER-THREADING**  Modern CPUs provide multiple instruction pipelines, supporting multiple execution threads, usually 2 to feed instructions to a single CPU core... Two hyper-threads are not equivalent 4770 with HTT Vs. 4670 without HTT - 25% improvement w/ HTT to (2) CPU cores CPU Mark Relative to Top 10 Common CPUs As of 7th of February 2014 - Higher results represent better perfor ■ i7-4770 and i5-4760 same CPU, with and without HTT ■ Example: → hyperthreads add +32.9% oftware Engineering for) Cloud Computing [Fall 2023] eering and Technology, University of Washington - Taco October 5, 2023 L3.6

Slides by Wes J. Lloyd L3.1

**HYPER-THREADING - 3**

For personal computing, hyper-threading helps improve system performance when many programs use only short bursts of CPU time

Databases, HPC (science) applications, and others may benefit from disabling hyper-threading. Testing will help quantify

Disabling hyper-threading (HW setting), cuts the number of CPU cores available to operating system in half

Can be disabled in the System BIOS or UEFI (uniform extensible firmware interface) software

BIOS / UEFI is a small resident program that can be accessed by pressing a function-key when rebooting the computer

When should we use hyper-threading, and when

Hyper-Threading (HT) **Technology** Provides more satisfactory solution · Single physical processor is shared as

- two logical processors

- Each logical processor has its own architecture state Single set of execution units are shared

- between logical processors

- N-logical PUs are supported

- Have the same gain % with only 5% diesize penalty.

- HT allows single processor to fetch and execute two separate code streams simultaneously.

BIOS / UEFI is used to configure hardware options Making changes requires rebooting the computer October 5, 2023

10

should not?

performance.

9

11

FEEDBACK - 3 The topic of SMD architectures and vector processing was new and a little unclear SISD, SIMD, MIMD October 5, 2023 L3.11

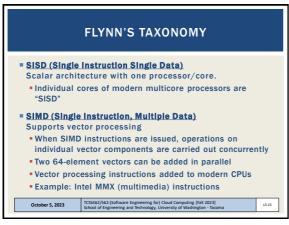

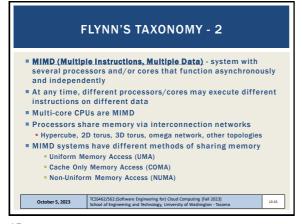

## MICHAEL FLYNN'S COMPUTER ARCHITECTURE TAXONOMY

- Michael Flynn's proposed taxonomy of computer architectures based on concurrent instructions and number of data streams (1966)

- SISD (Single Instruction Single Data)

- SIMD (Single Instruction, Multiple Data)

- MIMD (Multiple Instructions, Multiple Data)

- LESS COMMON: MISD (Multiple Instructions, Single Data)

- Pipeline architectures: functional units perform different operations on the same data

- For fault tolerance, may want to execute same instructions redundantly to detect and mask errors - for task replication

TCSS462/562:(Software Engineering for) Cloud Computing [Fall 2023] School of Engineering and Technology, University of Washington - Taco

Slides by Wes J. Lloyd L3.2

(SIMD): VECTOR PROCESSING ADVANTAGES

Exploit data-parallelism: vector operations enable speedups

Vectors architecture provide vector registers that can store entire matrices into a CPU register

SIMD CPU extension (e.g. MMX) add support for vector operations on traditional CPUs

Vector operations reduce total number of instructions for large vector operations

Provides higher potential speedup vs. MIMD architecture

Developers can think sequentially; not worry about parallelism

October 5, 2023

CCSG42/562/Software Engineering for/ Cloud Computing [fail 2023]

School of Engineering and Technology, University of Wistington - Tacoma

13

DEMOGRAPHICS SURVEY

Please complete the ONLINE demographics survey:

We have received 54 of 69 responses so far.

We are waiting on 15 responses.

https://forms.gle/QLiWGnHqbXDeNdYq7

Linked from course webpage in Canvas:

http://faculty.washington.edu/wlloyd/courses/tcss562/announcements.html

October 5, 2023

| ISSAG2/552: Editure Engineering (n) Cloud Competing [ral 2022] | School of Engineering and Technology, University of Wedneyton - Tacoma

15

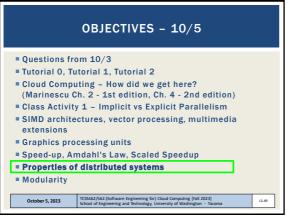

OBJECTIVES - 10/5

Questions from 10/3

Tutorial 0 Tutorial 1, Tutorial 2

Cloud Computing - How did we get here?

(Marinescu Ch. 2 - 1st edition, Ch. 4 - 2nd edition)

Class Activity 1 - Implicit vs Explicit Parallelism

SIMD architectures, vector processing, multimedia extensions

Graphics processing units

Speed-up, Amdahl's Law, Scaled Speedup

Properties of distributed systems

Modularity

October 5, 2023

CCSS462/562/56/tware Engineering for Cloud Computing (Fall 2023)

School of Engineering and Technology, University of Washington - Tacoma

17 18

Slides by Wes J. Lloyd L3.3

14

19

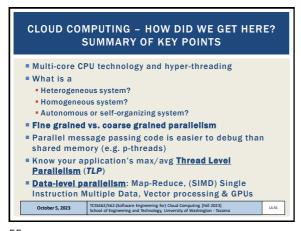

CLOUD COMPUTING:

HOW DID WE GET HERE? - 5

Compute clouds are large-scale distributed systems

Heterogeneous systems

Many services/platforms w/ diverse hw + capabilities

Homogeneous systems

Within a platform - illusion of identical hardware

Autonomous

Automatic management and maintenance- largely with little human intervention

Self organizing

User requested resources organize themselves to satisfy requests on-demand

Cotober 5, 2023

Cotober 5, 2023

Cotober 5, 2023

Cotober 5, 2023

Cotober 6, 2023

Cotober 6,

21

HARDWARE HETEROGENEITY If providing laaS, what are advantages/ disadvantages of using homogeneous hardware? Easier to provide same quality of service to end users Less performance variance Components with variable performance: CPUs, memory (speed differences), disks (SSDs, HDDs), network interfaces (caches?) Homogeneous hardware (servers): components are interchangeable As components fail, identical backups are immediately available Example: blade servers As clouds grow, why is HW homogeneity difficult to maintain? What are some advantages of using heterogeneous HW? TCSS462/562:(Software Engineering for) Cloud Computing [Fall 2023] School of Engineering and Technology, University of Washington - Taco

23 24

Slides by Wes J. Lloyd L3.4

20

**CLASS ACTIVITY 1** ■ Form groups of ~3 - in class or with Zoom breakout rooms ■ Each group will complete a MSWORD DOCX worksheet Be sure to add names at top of document as they appear in Activity can be completed in class or after class ■ The activity can also be completed individually When completed, one person should submit a PDF of the documet to Canvas Instructor will score all group members based on the uploaded To get started: Follow the link: (link also available in Canvas) https://faculty.washington.edu/wlloyd/courses/tcss562/ assignments/tcss462\_562\_f2023\_tps1.docx L3.26

**IMPLICIT PARALLELISM** Applies to: Advantages: Disadvantages: October 5, 2023 L3.28

27

PARALLELISM QUESTIONS ■ 7. For bit-level parallelism, should a developer be concerned with the available number of virtual CPU processing cores when choosing a cloud-based virtual machine if wanting to obtain the best possible speed-up? ■ 8. For instruction-level parallelism, should a developer be concerned with the physical CPU's architecture used to host a cloud-based virtual machine if wanting to obtain the best possible speed-up? (Yes / No) October 5, 2023

29 30

Slides by Wes J. Lloyd L3.5

26

OBJECTIVES - 10/5

Questions from 10/3

Tutorial 0, Tutorial 1, Tutorial 2

Cloud Computing - How did we get here?

(Marinescu Ch. 2 - 1st edition, Ch. 4 - 2nd edition)

Class Activity 1 - Implicit vs Explicit Parallelism

SIMD architectures, vector processing, multimedia extensions

Graphics processing units

Speed-up, Amdahl's Law, Scaled Speedup

Properties of distributed systems

Modularity

October 5, 2023

TCSS462/562/\$cfs/twave Engineering for/ Cloud Computing (Fall 2023)

School of Engineering and Technology, University of Washington - Tacoma

31 32

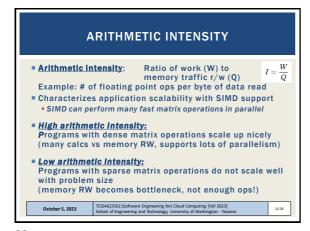

ROOFLINE MODEL

When program reaches a given arithmetic intensity performance of code running on CPU hits a "roof"

CPU performance bottleneck changes from: memory bandwidth (left) → floating point performance (right)

Key take-aways:

When a program's has low Arithmetic Intensity, memory bandwidth limits performance...

With high Arithmetic intensity, the system has peak parallel performance...

Arithmetic Intensity performance is limited by??

October 5, 2023

CCC5462/562/561/Software Engineering for Cloud Computing [Fail 2023]

School of Engineering and Technology, University of Washington - Tacoma

33

OBJECTIVES - 10/5

Questions from 10/3

Tutorial 0, Tutorial 1, Tutorial 2

Cloud Computing - How did we get here?

(Marinescu Ch. 2 - 1st edition, Ch. 4 - 2nd edition)

Class Activity 1 - Implicit vs Explicit Parallelism

SIMD architectures, vector processing, multimedia extensions

Graphics processing units

Speed-up, Amdahl's Law, Scaled Speedup

Properties of distributed systems

Modularity

October 5, 2023

ICSS462/S62/Softwave Engineering for Cloud Computing [Fall 2023]

School of Engineering and Technology, University of Washington - Tacoma

GRAPHICAL PROCESSING UNITS (GPUs)

GPU provides multiple SIMD processors

Typically 7 to 15 SIMD processors each

32,768 total registers, divided into 16 lanes

(2048 registers each)

GPU programming model:

single instruction, multiple thread

Programmed using CUDA- C like programming

language by NVIDIA for GPUs

CUDA threads – single thread associated with each

data element (e.g. vector or matrix)

Thousands of threads run concurrently

CICSSE2/GRAIS (Stote of Engineering for Josef Computing [felt 2023]

Stote of Engineering and Technology, University of Washington - Tacoms

35 36

Slides by Wes J. Lloyd L3.6

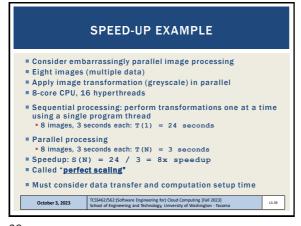

PARALLEL COMPUTING

■ Parallel hardware and software systems allow:

■ Solving problems needing resources not available on a single system.

■ Reduced time required to obtain solution

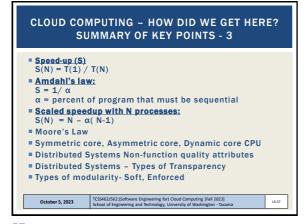

■ The speed-up (S) measures effectiveness of parallelization:

S(N) = T(1) / T(N)

T(1) → execution time of total sequential computation T(N) → execution time for performing N parallel computations in parallel computations in parallel should be separated by the sequence of the

37 38

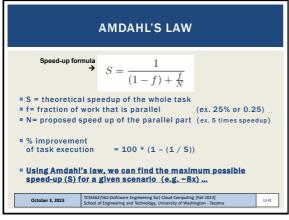

AMDAHL'S LAW

Amdahl's law is used to estimate the speed-up of a job using parallel computing

Divide job into two parts

Part A that will still be sequential

Part B that will be sped-up with parallel computing

Portion of computation which cannot be parallelized will determine (i.e. limit) the overall speedup

Amdahl's law assumes jobs are of a fixed size

Also, Amdahl's assumes no overhead for distributing the work, and a perfectly even work distribution

39

AMDAHL'S LAW EXAMPLE Program with two independent parts Part A is 75% of the execution time Part B is 25% of the execution time ■ Part B is made 5 times faster with parallel computing Estimate the percent improvement of task execution Original Part A is 3 seconds, Part B is 1 second ■ N=5 (speedup of part B) ■ f=.25 (only 25% of the whole job (A+B) will be sped-up) ■ S=1 / ((1-f) + f/S) ■ S=1 / ((.75) + .25/5) ■ S=1.25 (speed up is 1.25x faster) % improvement = 100 \* (1 - 1/1.25) = 20% TCSS462/562:(Software Engineering for) Cloud Computing [Fall 2023] School of Engineering and Technology, University of Washington - Tacoma October 3, 2023

41 42

Slides by Wes J. Lloyd L3.7

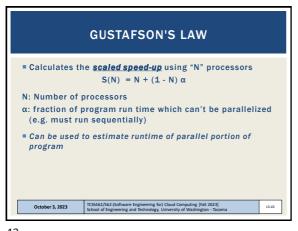

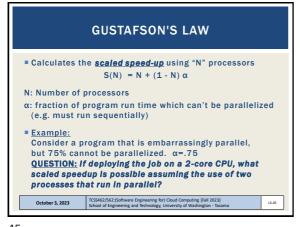

GUSTAFSON'S LAW

Calculates the scaled speed-up using "N" processors  $S(N) = N + (1 - N) \alpha$ N: Number of processors  $\alpha$ : fraction of program run time which can't be parallelized (e.g. must run sequentially)

Can be used to estimate runtime of parallel portion of program

Where  $\alpha = \sigma / (\pi + \sigma)$ Where  $\sigma$ = sequential time,  $\pi$  = parallel time

Our Amdahl's example:  $\sigma$ = 3s,  $\pi$ =1s,  $\alpha$ =.75

43 44

$\begin{array}{c} \text{GUSTAFSON'S EXAMPLE} \\ \\ \text{■ QUESTION:} \\ \text{What is the maximum theoretical speed-up on a $\frac{2\text{-core CPU}}{2}$?} \\ S(N) &= N + (1 - N) \ \alpha \\ N = 2, \ \alpha = .75 \\ S(N) &= 2 + (1 - 2) .75 \\ S(N) &= ? \\ \\ \text{■ What is the maximum theoretical speed-up on a $16\text{-core CPU}$?} \\ S(N) &= N + (1 - N) \ \alpha \\ N = 16, \ \alpha = .75 \\ S(N) &= 16 + (1 - 16) .75 \\ S(N) &= ? \\ \\ \text{October 3, 2023} \\ \\ \text{TCSS62/SG2/Sof-Mare Engineering for) Coud Computing [Fail 2023]} \\ \text{School of Engineering and Technology, University of Washington - Tacoma} \\ \end{array}$

45

```

GUSTAFSON'S EXAMPLE

OUESTION:

What is the maximum theoretical speed-up on a 2-core CPU?

S(N) = N + (1 - N) \alpha

N=2, α=

For 2 CPUs, speed up is 1.25x

S(N) =

S(N) = ?

For 16 CPUs, speed up is 4.75x

What is the maximum theoretical speed-up on a 16-core CPU?

S(N) = N + (1 - N) \alpha

N=16, \alpha=.75

S(N) = 16 + (1 - 16).75

S(N) = ?

October 3, 2023

L3.47

```

**MOORE'S LAW** ■ Transistors on a chip doubles approximately every 1.5 years ■ CPUs nov ■ Power di What kind of processor are modern to heat removal Intel CPUs? **Symmetric core processor** - multi-core CPU, all cores have the same computational resources and speed Asymmetric core processor – on a multi-core CPU, some cores have more resources and speed Dynamic core processor - processing resources and speed can be dynamically configured among cores Observation: asymmetric processors offer a higher speedup TCSS462/562:(Software Engineering for) Cloud Computing [Fall 2023] School of Engineering and Technology, University of Washington - Tacoma October 3, 2023

47 48

Slides by Wes J. Lloyd L3.8

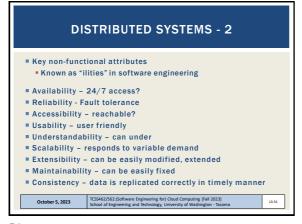

Collection of autonomous computers, connected through a network with distribution software called "middleware" that enables coordination of activities and sharing of resources

Key characteristics:

Users perceive system as a single, integrated computing facility.

Compute nodes are autonomous

Scheduling, resource management, and security implemented by every node

Multiple points of control and failure

Nodes may not be accessible at all times

System can be scaled by adding additional nodes

Availability at low levels of HW/software/network reliability

October 5, 2023

Cotober 5, 2023

Coto

49 50

TRANSPARENCY PROPERTIES OF DISTRIBUTED SYSTEMS

Access transparency: local and remote objects accessed using identical operations

Location transparency: objects accessed w/o knowledge of their location.

Concurrency transparency: several processes run concurrently using shared objects w/o interference among them

Replication transparency: multiple instances of objects are used to increase reliability

- users are unaware if and how the system is replicated

Fallure transparency: concealment of faults

Migration transparency: objects are moved w/o affecting operations performed on them

Performance transparency: system can be reconfigured based on load and quality of service requirements

Scaling transparency: system and applications can scale w/o change in system structure and w/o affecting applications

October 5, 2023

COCODER 5, 20

51

OBJECTIVES - 10/5

Questions from 10/3

Tutorial 0, Tutorial 1, Tutorial 2

Cloud Computing - How did we get here?

(Marinescu Ch. 2 - 1st edition, Ch. 4 - 2nd edition)

Class Activity 1 - Implicit vs Explicit Parallelism

SIMD architectures, vector processing, multimedia extensions

Graphics processing units

Speed-up, Amdahl's Law, Scaled Speedup

Properties of distributed systems

Modularity

October 5, 2023

INSSEE 2/1/562-1/565-tuture Engineering for) Good Computing (Fall 2023)

School of Engineering and Technology, University of Washington - Tacoms

TYPES OF MODULARITY

Soft modularity: TRADITIONAL

Divide a program into modules (classes) that call each other and communicate with shared-memory

A procedure calling convention is used (or method invocation)

Enforced modularity: CLOUD COMPUTING

Program is divided into modules that communicate only through message passing

The ubiquitous client-server paradigm

Clients and servers are independent decoupled modules

System is more robust if servers are stateless

May be scaled and deployed separately

May also FAIL separately!

Totober's, 2023

53 54

Slides by Wes J. Lloyd L3.9

CLOUD COMPUTING - HOW DID WE GET HERE?

SUMMARY OF KEY POINTS - 2

Bit-level parallelism

Instruction-level parallelism (CPU pipelining)

Flynn's taxonomy: computer system architecture classification

SISD - Single Instruction, Single Data (modern core of a CPU)

SIMD - Single Instruction, Multiple Data (Data parallelism)

MIMD - Multiple Instruction, Multiple Data

MISD is RARE; application for fault tolerance...

Arithmetic Intensity: ratio of calculations vs memory RW

Roofline model:

Memory bottleneck with low arithmetic intensity

GPUs: ideal for programs with high arithmetic intensity

SIMD and Vector processing supported by many large registers

October 5, 2023

TCSS62/SG2:(Software Engineering for) Cloud Computing [Fail 2023]

School of Engineering and Technology, University of Washington - Taxoma

55 56

57 58

Slides by Wes J. Lloyd L3.10