# Serverless? RISC more!

### TCSS562

1

Group Members: Aaron Chen , Mingzhi Ma, Derry Cheng

### **BE BOUNDLESS**

# **Proposed Methodology**

### **RISC-V Platform Advantages:**

- Open-source and parameterizable architecture.

- Supports full-system stacks for accurate workload simulations.

### **Benchmark Approach:**

Combination of microbenchmarks (e.g., matrix operations) and workflows (e.g., image and text processing).

### Table 2: Benchmarks Evaluated

| Benchmark        | Туре     | Language          |  |  |

|------------------|----------|-------------------|--|--|

| matmul           | Micro    | Python (numpy)    |  |  |

| floater          | Micro    | Python            |  |  |

| linpack          | Micro    | Python (numpy)    |  |  |

| image processing | Workflow | Python (OpenCV)   |  |  |

| text processing  | Workflow | Python            |  |  |

| compilation      | Workflow | Python, GCC, Make |  |  |

9

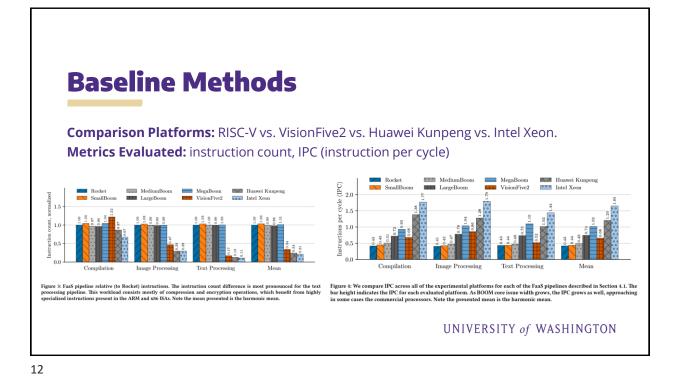

## **RISC-V Configurations and Comparative Platforms**

### **Table 1: Per-Core Configurations**

| Name                       | Core         | ISA     | 000 | Issue | L1 Size (I/D) | L2 Size | CoreMark/Mhz |

|----------------------------|--------------|---------|-----|-------|---------------|---------|--------------|

| Rocket                     | Rocket       | riscv64 | ×   | 1     | 16/16 KiB     | 512 KiB | 2.14         |

| SmallBoom                  | BOOM         | riscv64 | 1   | 3     | 16/16 KiB     | 512 KiB | 2.27         |

| MediumBoom                 | BOOM         | riscv64 | 1   | 4     | 16/16 KiB     | 512 KiB | 3.76         |

| LargeBoom                  | BOOM         | riscv64 | ✓   | 5     | 32/32 KiB     | 512 KiB | 4.88         |

| MegaBoom                   | BOOM         | riscv64 | 1   | 8     | 32/32 KiB     | 512 KiB | 5.31         |

| StarFive VisionFive2 [71]  | JH7110       | riscv64 | ×   | 2     | 32/32 KiB     | 2 MiB   | 3.30         |

| Huawei Kunpeng 920 [82]    | ARMv8.2      | aarch64 | 1   | 4     | 64/64 KiB     | 512 KiB | 7.20         |

| Intel Xeon Gold 6238T [37] | Cascade Lake | x86-64  | 1   | 8     | 32/32 KiB     | 1 MiB   | 7.54         |

UNIVERSITY of WASHINGTON

# Key contributions First study leveraging RISC-V for serverless workload exploration with realistic system software. Demonstrates the potential of RISC-V cores in achieving comparable instructions-percycle (IPC) to ARM. Opens new avenues for evaluating microarchitectural features tailored for cloud-native workloads. Mbat's New? Comprehensive exploration of specialized CPU designs for serverless scenarios. Identification of bottlenecks in current CPU designs for short-lived, bursty workloads.

11

# **Critique:Weakness**

- > An open-source could be **unstable** and industries might not upload their new architectures.

- **Stability is stepstone for cloud computing**, this paper should add some more statements to support it.

- > The paper says "RISC more!" but in the end they <u>haven't surpassed</u> mainstream products.

UNIVERSITY of WASHINGTON