| МО                                                       | RE THAN 1                                                  | IWO LEVE                                        | LS - 2                       |

|----------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------|------------------------------|

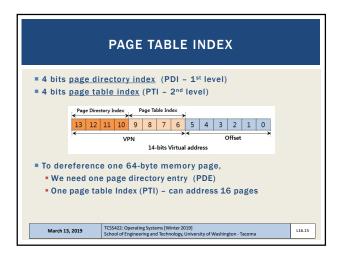

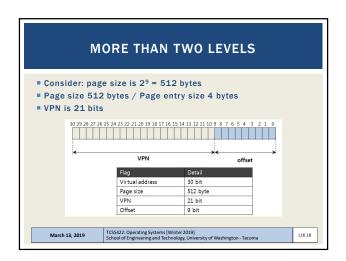

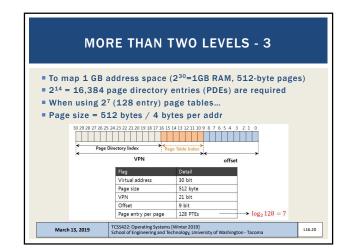

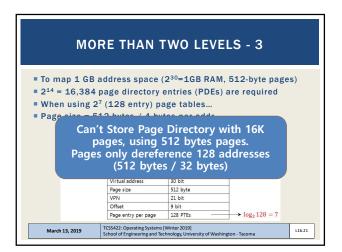

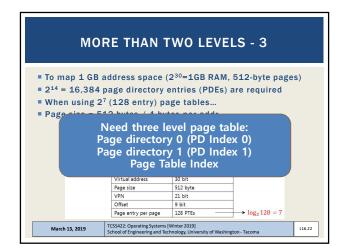

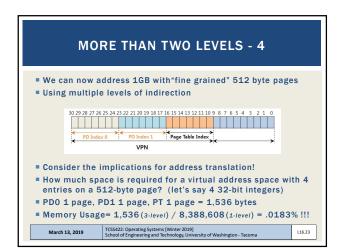

| <ul> <li>Page table en</li> <li>7 bytes - for</li> </ul> | itries per page<br>page table inde                         |                                                 | 8                            |

| 30 29 28 27 26 25 2<br>Page Dir                          |                                                            | 14 13 12 11 10 9 8 7 6 5                        | 4 3 2 1 0                    |

|                                                          | Flag                                                       | Detail                                          |                              |

|                                                          | Virtual address                                            | 30 bit                                          |                              |

|                                                          | Page size                                                  | 512 byte                                        |                              |

|                                                          | VPN                                                        | 21 bit                                          |                              |

|                                                          | Offset                                                     | 9 bit                                           |                              |

|                                                          | Page entry per page                                        | 128 PTEs                                        | $\rightarrow \log_2 128 = 7$ |

|                                                          |                                                            |                                                 |                              |

| March 13, 2019                                           | TCSS422: Operating Systems<br>School of Engineering and Te | [Winter 2019]<br>chnology, University of Washin | gton - Tacoma                |

| ADDI                                                                                                                    | RESS TRANSLATION CODE                                                                                               |        |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|

| //<br>// Inputs:<br>// mm_struct                                                                                        | .inux page table address lookup<br>process's memory map struct<br>virtual page address                              |        |

| <pre>// Define pa<br/>pgd_t *pgd;<br/>p4d_t *p4d;<br/>pud_t *pud;<br/>pmd_t *put;<br/>pte_t *pte;<br/>struct page</pre> | nge struct pointers                                                                                                 |        |

| March 13, 2019                                                                                                          | TCSS422: Operating Systems [Winter 2019]<br>School of Engineering and Technology, University of Washington - Tacoma | L16.24 |

| ADDRE                                                                                                                                      | SS TRANSL                                                             |                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| <pre>pgd = pgd_offset(mm,<br/>if (pgd_none(*pgd)   <br/>return 0;</pre>                                                                    | pgd_bad(*pgd))                                                        | pgd_offset():<br>Takes a vpage address and the mm_struct<br>for the process, returns the PGD entry that<br>covers the requested address |

| <pre>p4d = p4d_offset(pgd,<br/>if (p4d_none(*p4d)   <br/>return 0;<br/>pud = pud_offset(p4d,<br/>if (pud_none(*pud)   <br/>return 0;</pre> | <pre>p4d_bad(*p4d)) vpage);</pre>                                     | <b>p4d/pud/pmd_offset():</b><br>Takes a vpage address and the<br>pgd/p4d/pud entry and returns the<br>relevant p4d/pud/pmd.             |

| <pre>pmd = pmd_offset(pud,<br/>if (pmd_none(*pmd)   <br/>return 0;<br/>if (!(pte = pte_offse</pre>                                         | <pre>pmd_bad(*pmd))</pre>                                             | a)))                                                                                                                                    |

| <pre>return 0;<br/>if (!(page = pte_page<br/>return 0;<br/>physical page addr =</pre>                                                      | -                                                                     | pte_unmap()<br>release temporary kernel mapping<br>for the page table entry                                                             |

| <pre>pte_unmap(pte); return physical_page_</pre>                                                                                           |                                                                       |                                                                                                                                         |

|                                                                                                                                            | Dperating Systems [Winter 2019]<br>Engineering and Technology, Univer | rsity of Washington - Tacoma                                                                                                            |

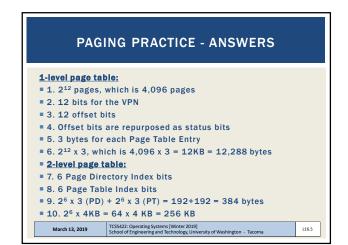

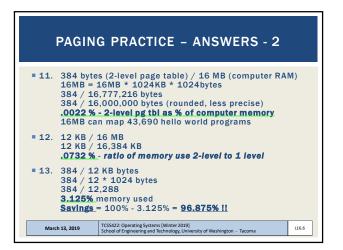

|                      | ANSWERS                                                 |                                       |         |

|----------------------|---------------------------------------------------------|---------------------------------------|---------|

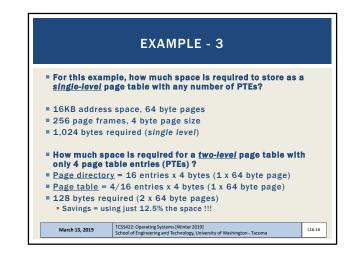

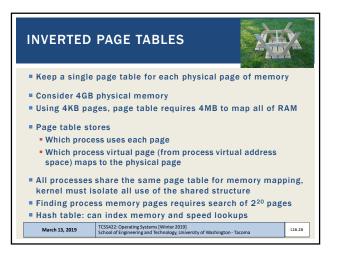

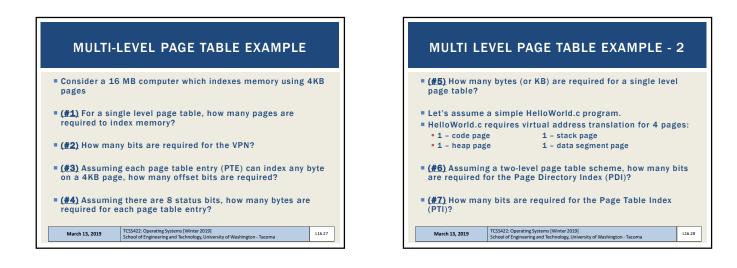

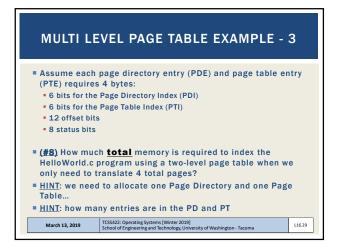

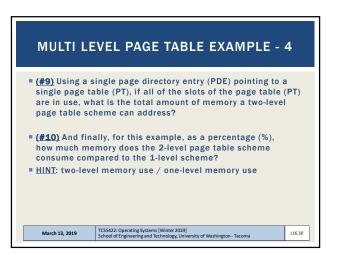

| ■ #1 - 4096 pa       | ges                                                     |                                       |         |

| #2 - 12 bits         |                                                         |                                       |         |

| #3 - 12 bits         |                                                         |                                       |         |

| ■ #4 - 4 bytes       |                                                         |                                       |         |

| <b>#5 - 4096 x 4</b> | = 16,384 bytes (16KB)                                   |                                       |         |

| ■ #6 - 6 bits        |                                                         |                                       |         |

| ■ #7 - 6 bits        |                                                         |                                       |         |

|                      | s for Page Directory (PD)<br>s for Page Table (PT)      | · · · · · · · · · · · · · · · · · · · | · · · · |

|                      | es, where each entry maps<br>t bits, can address 262,14 | , , , ,                               |         |

| <b>#10-512/163</b>   | 384 = .03125 → 3.125%                                   |                                       |         |

|                      | TCSS422: Operating Systems [Winter 2019]                |                                       |         |

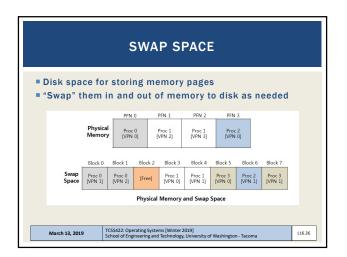

| Design cons                                       |          |                      |                  |                                       |

|---------------------------------------------------|----------|----------------------|------------------|---------------------------------------|

| SSDs 4x the                                       |          |                      |                  |                                       |

| HDDs 80x t                                        | he time  | of DRAM              |                  |                                       |

| Action                                            |          | Latency (ns)         | (µs)             |                                       |

| L1 cache reference                                |          | 0.5ns                |                  |                                       |

| L2 cache reference                                |          | 7 ns                 |                  | 14x L1 cache                          |

|                                                   |          |                      |                  |                                       |

| Mutex lock/unlock                                 |          | 25 ns                |                  |                                       |

| Mutex lock/unlock<br>Main memory reference        |          | 25 ns<br>100 ns      |                  | 20x L2 cache, 200x L1                 |

|                                                   | iD*      |                      | 150 µs           | 20x L2 cache, 200x L1<br>~1GB/sec SSD |

| Main memory reference                             |          | 100 ns               | 150 μs<br>250 μs |                                       |

| Main memory reference<br>Read 4K randomly from SS | ommemory | 100 ns<br>150,000 ns |                  |                                       |

L16.50

March 13, 2019

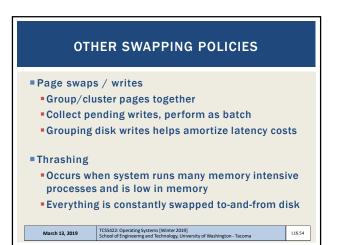

## OTHER SWAPPING POLICIES - 2 Working sets Groups of related processes When thrashing: prevent one or more working set(s) from running Temporarily reduces memory burden

Allows some processes to run, reduces thrashing

TCSS422: Operating Systems [Winter 2019] School of Engineering and Technology, University of Washington - Tacoma L16.55