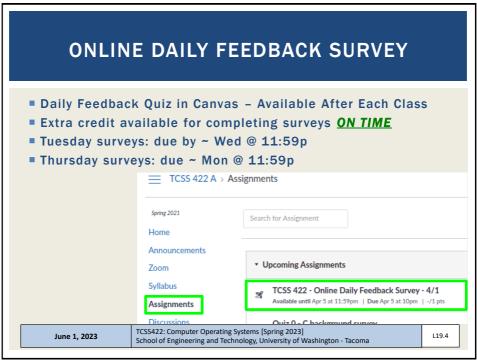

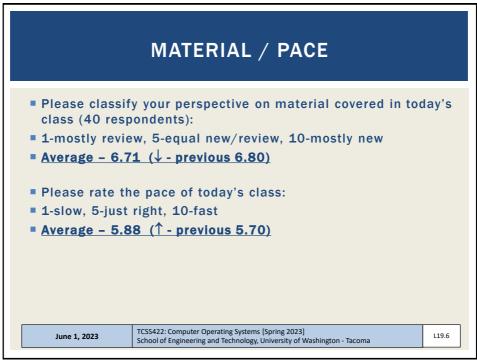

| т            | CSS   | 422 -                   | Onli     | ine D    | Daily   | Feedb          | back S   | Surve   | y - 4/   | 1       |                           |      |  |       |

|--------------|-------|-------------------------|----------|----------|---------|----------------|----------|---------|----------|---------|---------------------------|------|--|-------|

| Q            | uiz l | nstru                   | ctior    | าร       |         |                |          |         |          |         |                           |      |  |       |

| C            |       | Questior                | 11       |          |         |                |          |         |          |         | 0.5 pts                   |      |  |       |

|              |       | On a scal<br>:lass:     | e of 1 t | to 10, p | lease c | lassify yo     | our pers | pective | on mater | ial cov | ered in today's           |      |  |       |

|              |       | 1<br>Mostly<br>Review T | 2        | 3        |         | 5<br>Equal     | 6        | 7       | 8        | 9       | 10<br>Mostly<br>New to Me |      |  |       |

|              |       | KOVICW I                |          |          |         |                | 104      |         |          |         | New CO He                 |      |  |       |

|              |       |                         |          |          |         |                |          |         |          |         |                           |      |  |       |

| c            |       | Questior                | 12       |          |         |                |          |         |          |         | 0.5 pts                   |      |  |       |

|              | F     | Please rat              | te the p | ace of   | today's | class:         |          |         |          |         |                           |      |  |       |

|              |       | 1<br>Slow               | 2        | 3        | 4       | 5<br>ust Right | 6        | 7       | 8        | 9       | 10<br>Fast                |      |  |       |

|              |       |                         |          |          |         |                |          |         |          |         |                           |      |  |       |

| June 1, 2023 |       |                         | TCSS     | 422: C   | omput   | er Opera       | ating Sy | stems [ | Spring 2 | 023]    | shington - Tacor          | ma   |  | _19.5 |

| E            |       |                         | 50100    | I OI EII | gineer  | ing and        | IECIII0  | ogy, Un | iversity |         | snington - Tacor          | IIId |  | 2.0.0 |

| CAN                                                                                                | CANONICAL DEVICE                                                         |                    |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|--|--|--|--|--|--|

| Consider an arbitra                                                                                | Consider an arbitrary canonical "standard/generic" device                |                    |  |  |  |  |  |  |

| Registers: Status                                                                                  | Command Data                                                             | interface          |  |  |  |  |  |  |

| Micro-controller(CPU)<br>Memory (DRAM or SRAM o<br>Other Hardware-specific Chi                     |                                                                          | internals          |  |  |  |  |  |  |

| Canonical Device                                                                                   |                                                                          |                    |  |  |  |  |  |  |

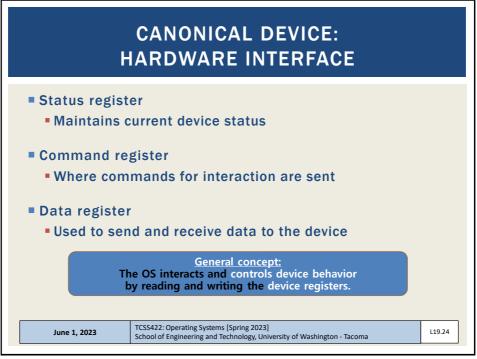

| Two primary compo                                                                                  | Two primary components                                                   |                    |  |  |  |  |  |  |

| Interface (registers)                                                                              | Interface (registers for communication)                                  |                    |  |  |  |  |  |  |

| <ul> <li>Internals: Local CPU, memory, specific chips, firmware<br/>(embedded software)</li> </ul> |                                                                          |                    |  |  |  |  |  |  |

|                                                                                                    | rating Systems [Spring 2023]<br>ineering and Technology, University of W | ashington - Tacoma |  |  |  |  |  |  |

|                                                                                                    |                                                                          |                    |  |  |  |  |  |  |

| 0              | OS DEVICE INTERACTION                                                                                               |       |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|

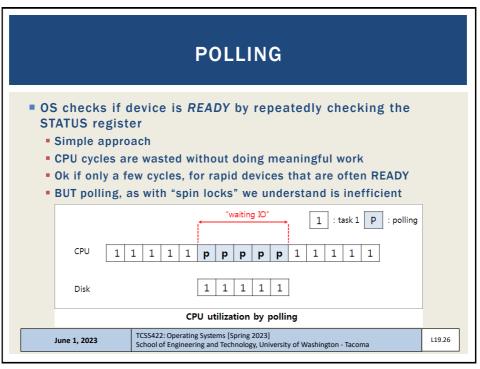

| Common example | Common example of device interaction                                                                                |       |  |  |  |  |

| while ( STATU  | US == BUSY)                                                                                                         |       |  |  |  |  |

|                | o data register Command parameterization                                                                            |       |  |  |  |  |

|                | d to command register <b>( Send command</b><br>starts the device and executes the command                           |       |  |  |  |  |

| while ( STATU  | US == BUSY) <b>Poll - Is device done?</b><br>until device is done with your request                                 |       |  |  |  |  |

|                |                                                                                                                     | ļ     |  |  |  |  |

|                |                                                                                                                     |       |  |  |  |  |

|                |                                                                                                                     |       |  |  |  |  |

| June 1, 2023   | TCSS422: Operating Systems [Spring 2023]<br>School of Engineering and Technology, University of Washington - Tacoma | L19.3 |  |  |  |  |

| Mode +          | # ♦                      | Maximum transfer rate<br>(MB/s) | cycle time \$ |  |  |  |  |

|-----------------|--------------------------|---------------------------------|---------------|--|--|--|--|

|                 | 0                        | 3.3                             | 600 ns        |  |  |  |  |

|                 | 1                        | 5.2                             | 383 ns        |  |  |  |  |

| PIO             | 2                        | 8.3                             | 240 ns        |  |  |  |  |

|                 | 3                        | 11.1                            | 180 ns        |  |  |  |  |

|                 | 4                        | 16.7                            | 120 ns        |  |  |  |  |

|                 | 0                        | 2.1                             | 960 ns        |  |  |  |  |

| Single-word DMA | 1                        | 4.2                             | 480 ns        |  |  |  |  |

|                 | 2                        | 8.3                             | 240 ns        |  |  |  |  |

|                 | 0                        | 4.2                             | 480 ns        |  |  |  |  |

|                 | 1                        | 13.3                            | 150 ns        |  |  |  |  |

| Multi-word DMA  | 2                        | 16.7                            | 120 ns        |  |  |  |  |

|                 | 3 <sup>[34]</sup>        | 20                              | 100 ns        |  |  |  |  |

|                 | <b>4</b> <sup>[34]</sup> | 25                              | 80 ns         |  |  |  |  |

|                 | 0                        | 16.7                            | 240 ns ÷ 2    |  |  |  |  |

|                 | 1                        | 25.0                            | 160 ns ÷ 2    |  |  |  |  |

|                 | 2 (Ultra ATA/33)         | 33.3                            | 120 ns ÷ 2    |  |  |  |  |

| Ultra DMA       | 3                        | 44.4                            | 90 ns ÷ 2     |  |  |  |  |

| Oltra DiviA     | 4 (Ultra ATA/66)         | 66.7                            | 60 ns ÷ 2     |  |  |  |  |

|                 | 5 (Ultra ATA/100)        | 100                             | 40 ns ÷ 2     |  |  |  |  |

|                 | 6 (Ultra ATA/133)        | 133                             | 30 ns ÷ 2     |  |  |  |  |

|                 | 7 (Ultra ATA/167)[35]    | 167                             | 24 ns ÷ 2     |  |  |  |  |

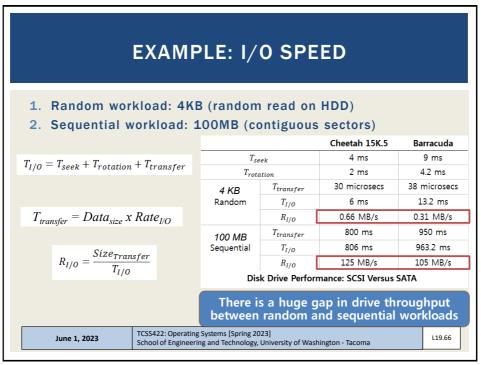

|                    | EXAN                                                                                                                                                                                                                                                                  | IPLE: I/O S                                                         | PEED                   |        |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------|--------|--|--|--|--|

| 1. Rand<br>2. Sequ | <ul> <li>Compare two disks:</li> <li>1. Random workload: 4KB (random read on HDD)</li> <li>2. Sequential workload: 100MB (contiguous sectors)         <ul> <li>&gt; Calculate T<sub>rotation</sub> from rpm (rpm→rps, time for 1 rotation / 2)</li> </ul> </li> </ul> |                                                                     |                        |        |  |  |  |  |

|                    | Cheetah 15K.5 Barracuda                                                                                                                                                                                                                                               |                                                                     |                        |        |  |  |  |  |

|                    | Capacity 300 GB 1 TB                                                                                                                                                                                                                                                  |                                                                     |                        |        |  |  |  |  |

|                    | RPM                                                                                                                                                                                                                                                                   | 15,000                                                              | 7,200                  |        |  |  |  |  |

|                    | Average Seek                                                                                                                                                                                                                                                          | 4 ms                                                                | 9 ms                   |        |  |  |  |  |

|                    | Max Transfer                                                                                                                                                                                                                                                          | 125 MB/s                                                            | 105 MB/s               |        |  |  |  |  |

|                    | Platters                                                                                                                                                                                                                                                              | 4                                                                   | 4                      |        |  |  |  |  |

|                    | Cache                                                                                                                                                                                                                                                                 | 16 MB                                                               | 16/32 MB               |        |  |  |  |  |

|                    | Connects Via                                                                                                                                                                                                                                                          | SCSI                                                                | SATA                   |        |  |  |  |  |

|                    | Disk Drive Specs: SCSI Versus SATA                                                                                                                                                                                                                                    |                                                                     |                        |        |  |  |  |  |

| June 1, 2          |                                                                                                                                                                                                                                                                       | rating Systems [Spring 2023]<br>ineering and Technology, University | of Washington - Tacoma | L19.65 |  |  |  |  |

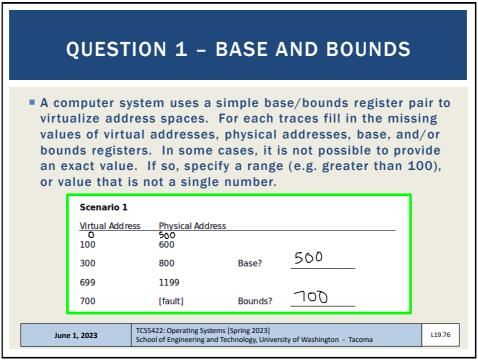

|                                                                                                                                                 | Q1 - 2                                      |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|

| Scenario 2                                                                                                                                      | Diversional Addresses                       |  |  |  |  |

| <u>Virtual Address</u><br>300                                                                                                                   | Physical Address<br>1500 Base? 1200         |  |  |  |  |

| 1600<br>1801<br>2801                                                                                                                            | 2800<br>3001 ? Bounds? 72801<br>4001        |  |  |  |  |

| Scenario 3<br>Virtual Address                                                                                                                   | Physical Address                            |  |  |  |  |

| 0                                                                                                                                               | 1000 Base? <u>1000</u>                      |  |  |  |  |

| 100<br>1999<br>2000                                                                                                                             | 1100<br>2999 Bounds? <u>2000</u><br>[fault] |  |  |  |  |

| June 1, 2023     TCSS422: Operating Systems [Spring 2023]<br>School of Engineering and Technology, University of Washington - Tacoma     L19.77 |                                             |  |  |  |  |

| QUESTION 4 – CACHE TRACING                                                                                                                                                                                  |                                                                              |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| <ul> <li>Consider a 3-element cache with the cache arrival sequences below.</li> <li>Determine the number of cache hits and cache misses using each of the following cache replacement policies:</li> </ul> |                                                                              |  |  |  |  |  |

| A. Optimal policy         Arrival sequence:         5 3 7 5 3 1 0 7 1 6 4 3 2 1 3         m m m H H M M H M M M M H H         # Hits: <u>6</u> # Misses: <u>9</u>                                           | Working Cache<br>Cache 1: ≸ /<br>Cache 2: \$ \$ \$ \$<br>Cache 3: \$ \$ \$ 3 |  |  |  |  |  |

| June 1, 2023 TCSS422: Operating Systems [Spring<br>School of Engineering and Technolog                                                                                                                      | 2023]<br>y, University of Washington - Tacoma                                |  |  |  |  |  |

| Q4 - 2                                                                                               |                                                     |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| P. EIEO policy                                                                                       |                                                     |

| B. FIFO policy<br>Arrival sequence:                                                                  | <u>Working Cache</u><br>Cache 1: इ <sub>२</sub> ५ ४ |

| 537531071643243<br>๛๛๛๚ฃ๛๛๚ฃ๛๛๛๛๛๛                                                                   | Cache 2:३ & <sup>3</sup><br>Cache 3:文및 스            |

| # Hits: <u>5</u><br># Misses: <u>10</u>                                                              |                                                     |

| June 1, 2023 TCSS422: Operating Systems [Spring 2023]<br>School of Engineering and Technology, Unive | ersity of Washington - Tacoma                       |

| Q4 - 3                                                                                                                                             |                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|                                                                                                                                                    |                                        |

| C. LRU policy<br>Arrival sequence:                                                                                                                 | Working Cache<br>Cache 1:5375310716    |

| 537531071643213<br>mm <sup>m</sup> <u>H</u> <u>H</u> mm m <u>H</u> mm <sup>m</sup> <u>m</u> <u>H</u> <u>H</u> m m m <u>H</u> <u>m</u> m m <u>H</u> | Cache 2:-53753/071<br>Cache 3:53753107 |

| # Hits:<br># Misses:                                                                                                                               | 4 3 2 1 3<br>6 4 3 2 1<br>1 6 4 3 2    |

| June 1, 2023 TCSS422: Operating Systems [Spring 2023]<br>School of Engineering and Technology, Univers                                             | sity of Washington - Tacoma            |