**ZOOM RECORDING ANALYTICS** Spring Fever? Stay tuned, many new concepts post-midterm Cummulative Views of TCSS 422 Zoom Recordings May 18, 2023 L15.4

3

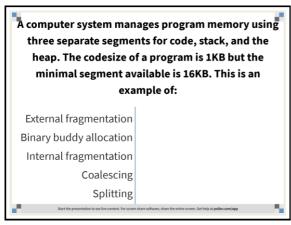

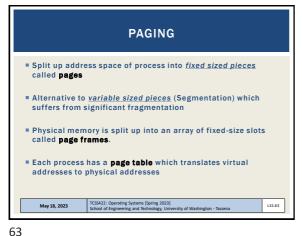

FEEDBACK - 2 What if the amount of memory needed is really large or really small? A modern system will manage memory using paging which enables code, heap, and stack storage to exceed a single segment through the use of memory paging Chapter 18 May 18, 2023 L15.10

10

12

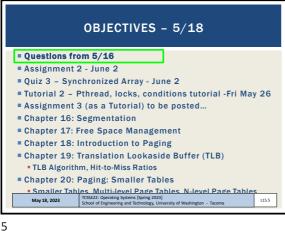

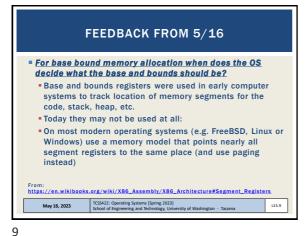

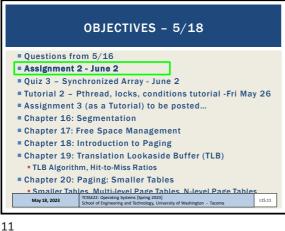

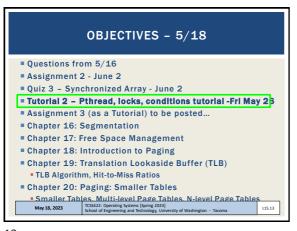

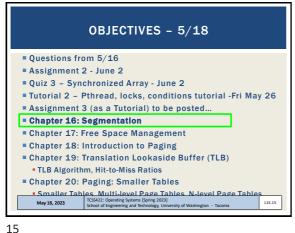

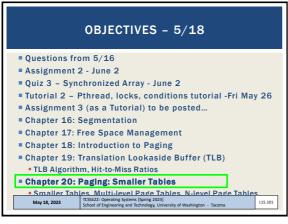

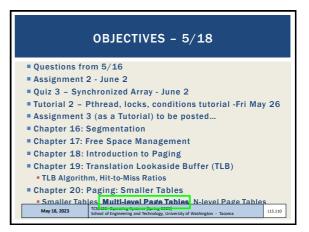

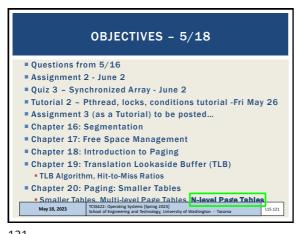

**OBJECTIVES - 5/18** ■ Questions from 5/16 Assignment 2 - June 2 Quiz 3 – Synchronized Array - June 2 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 26 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 16: Segmentation ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tahles Multi-level Page Tahles N-level Page Tahle May 18, 2023 TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma L15.12

Slides by Wes J. Lloyd

L15.2

**OBJECTIVES - 5/18** Questions from 5/16 Assignment 2 - June 2 Quiz 3 - Synchronized Array - June 2 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 26 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 16: Segmentation ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables May 18, 2023 TCSS422: Operating Systems (Spring 2023) School of Engineering and Technology, Uni versity of Washington - Tacoma

13 14

17 18

```

SEGMENT REGISTERS

Used to dereference memory during translation

13 12 11 10 9 8 7 6 5 4 3 2

First two bits identify segment type

Remaining bits identify memory offset

Example: virtual heap address 4200 (01000001101000)

bits

Code

Heap

01

TCSS422: Operating Systems [Spring 2023]

School of Engineering and Technology, University of Washington - Tacoma

May 18, 2023

L15.23

```

**SEGMENTATION DEREFERENCE** // get top 2 bits of 14-bit VA

Segment = (VirtualAddress & SEG\_MASK) >> SEG\_SHIFT // now get offset

Offset = VirtualAddress & OFFSET\_MASK

if (Offset >= Bounds[Segment])

RaiseException(PROTECTION\_FAULT) PhysAddr = Base[Segment] + Offset Register = AccessMemory(PhysAddr) **VIRTUAL ADDRESS = 01000001101000** (on heap) SEG\_MASK = 0x3000 (1100000000000) ■ SEG\_SHIFT = 01 → heap (mask gives us segment code) = OFFSET\_MASK = 0xFFF (00111111111111) • OFFSET = 000001101000 = 104 (isolates segment offset) ■ OFFSET < BOUNDS: 104 < 2048 TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma May 18, 2023 L15.24

23 24

Consider a program with 2KB of code, a 1 KB stack, and a 2 KB heap. This program runs on a 64 KB computer that manages memory with 4 kb segments. If the computer is empty and segments were allocated as: code, stack, heap, how large can the heap grow to? 32 KB 56 KB 24 KB 4 KB 0 KB

29 30

Slides by Wes J. Lloyd

OBJECTIVES - 5/18

Questions from 5/16

Assignment 2 - June 2

Quiz 3 - Synchronized Array - June 2

Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 26

Assignment 3 (as a Tutorial) to be posted...

Chapter 16: Segmentation

Chapter 17: Free Space Management

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables. Multi-level Page Tables. Nevel Page Tables

Smaller Tables. Multi-level Page Tables. Nevel Page Tables

31 32

OBJECTIVES - 5/18

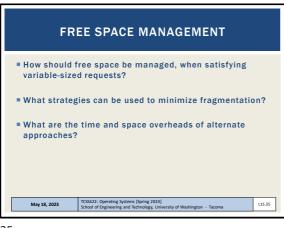

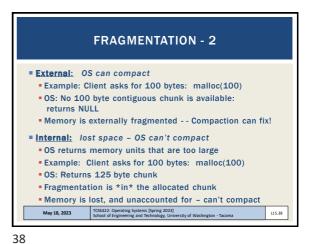

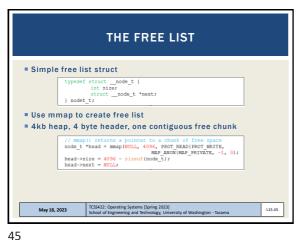

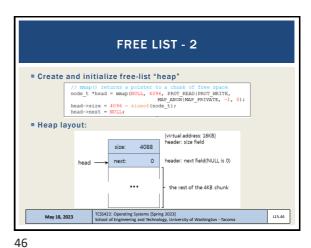

Chapter 17: Free Space Management

Fragmentation, Splitting, coalescing

The Free List

Memory Allocation Strategies

TCSS422: Operating Systems (Spring 2023)

School of Engineering and Technology, University of Washington - Taxoma

34

00

35 36

ALLOCATION STRATEGY: SPLITTING

Request for 1 byte of memory: malloc(1)

30-byte heap: free used free of 10 20 30 free list: head addr:0 len:10 hould

Splits chunk into two, returns first chunk

30-byte heap: free used free of 10 20 21 30 free list: head len:10 hould

30-byte heap: free used free of 10 20 21 30 free list: head len:10 hould free list: head len:10

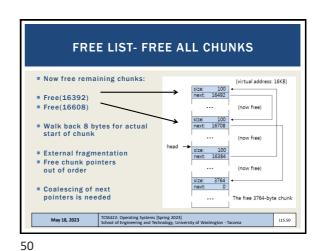

ALLOCATION STRATEGY: COALESCING

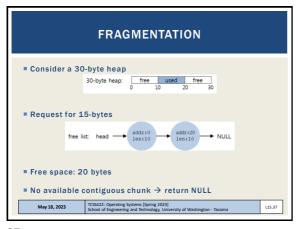

■ Consider 30-byte heap

■ Free() frees all 10 bytes segments (list of 3-free 10-byte chunks)

head → addr:10 → addr:0 → addr:20 → NULL

■ Request arrives: malloc(30)

■ SPLIT DOES NOT WORK - no contiguous 30-byte chunk exists!

■ Coalescing regroups chunks into contiguous chunk

head → addr:0 → NULL

■ Allocation can now proceed

■ Coalescing is defragmentation of the free space list

| May 18, 2023 | TSSA22. Operating Statems (Spring 2023) | TSSA22. Operat

39

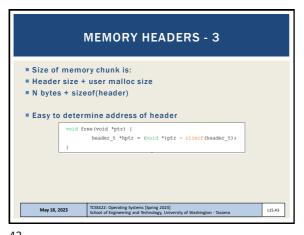

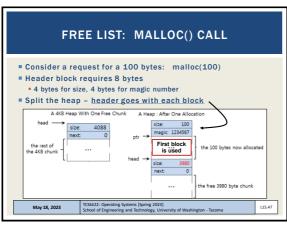

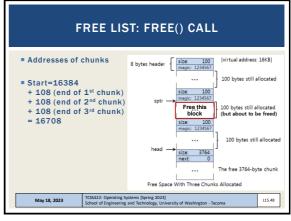

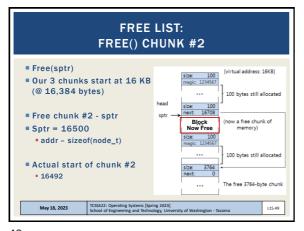

MEMORY HEADERS

If free(void \*ptr): Does not require a size parameter

How does the OS know how much memory to free?

Header block

Small descriptive block of memory at start of chunk

The header used by malloc library

The 20 bytes returned to caller

An Allocated Region Plus Header

May 18, 2023

TCSA12: Operating Systems (Spring 2023)

School of Engineering and Rechnology, University of Washington - Tocoma

MEMORY HEADERS - 2

hptr → size: 20

ptr → The 20 bytes returned to caller

Specific Contents of The Header

■ Contains size

■ Pointers: for faster memory access

■ Magic number: integrity checking

May 18, 2023

1755422: Operating Systems (Spring 2023)

School of Engineering and Technology, University of Washington - Tacoma

42

40

47 48

**GROWING THE HEAP** Start with small sized heap Request more memory when full sbrk(), brk() (not in use (not in use) Heap Heap (not in use) (not in use May 18, 2023 L15.51

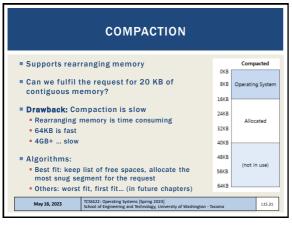

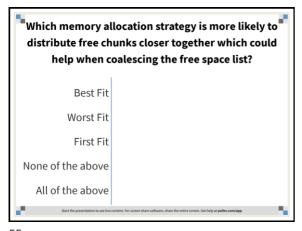

MEMORY ALLOCATION STRATEGIES Best fit Traverse free list Identify all candidate free chunks Note which is smallest (has best fit) • When splitting, "leftover" pieces are small (and potentially less useful - fragmented) ■ Worst fit Traverse free list Identify largest free chunk Split largest free chunk, leaving a still large free chunk May 18, 2023

51

**EXAMPLES** ■ Allocation request for 15 bytes Result of Best Fit Result of Worst Fit May 18, 2023 L15.53 53

**MEMORY ALLOCATION STRATEGIES - 2** ■ First fit Start search at beginning of free list • Find first chunk large enough for request Split chunk, returning a "fit" chunk, saving the remainder · Avoids full free list traversal of best and worst fit • Similar to first fit, but start search at last search location • Maintain a pointer that "cycles" through the list Helps balance chunk distribution vs. first fit • Find first chunk, that is large enough for the request, and split Avoids full free list traversal TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma May 18, 2023 L15.54

54

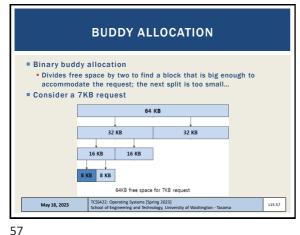

BUDDY ALLOCATION - 2

Buddy allocation: suffers from internal fragmentation

Allocated fragments, typically too large

Coalescing is simple

Two adjacent blocks are promoted up

Two adjacent blocks are promoted up

58

5/

A request is made to store 1 byte. For this scenario, which memory allocation strategy will always locate memory the fastest?

Best fit

Worst fit

Next fit

None of the above

All of the above

59 60

ADVANTAGES OF PAGING

Flexibility

Abstracts the process address space into pages

No need to track direction of HEAP / STACK growth

Just add more pages...

No need to store unused space

As with segments...

Simplicity

Pages and page frames are the same size

Easy to allocate and keep a free list of pages

May 18, 2023

TCSS422: Operating Systems [Spring 2023]

School of Engineering and Technology, University of Washington - Tacoma

64

66

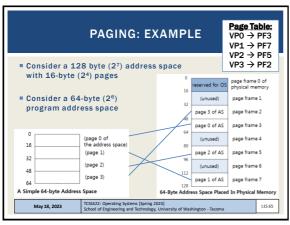

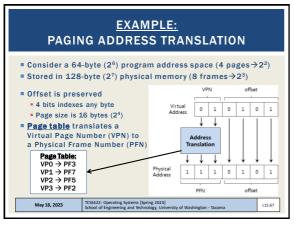

PAGING: ADDRESS TRANSLATION

PAGE: Has two address components

VPN: Virtual Page Number (serves as the page ID)

Offset: Offset within a Page (indexes any byte in the page)

VPN offset

Slides by Wes J. Lloyd

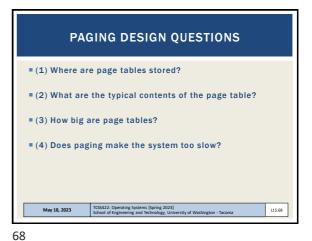

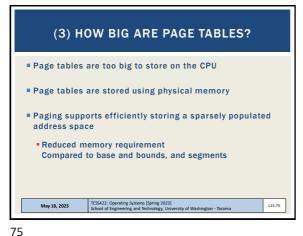

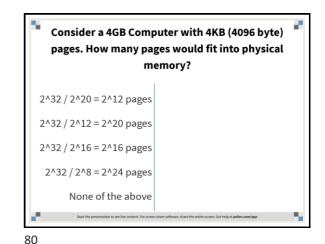

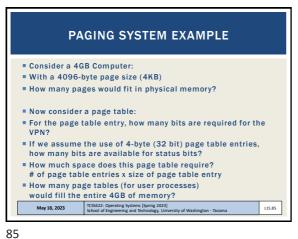

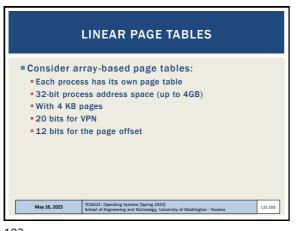

(1) WHERE ARE PAGE TABLES STORED? ■ Example: Consider a 32-bit process address space (4GB=2<sup>32</sup> bytes) With 4 KB pages (4KB=2<sup>12</sup> bytes) ■ 20 bits for VPN (220 pages) • 12 bits for the page offset (212 unique bytes in a page) ■ Page tables for each process are stored in RAM Support potential storage of 2<sup>20</sup> translations = 1,048,576 pages per process Each page has a page table entry size of 4 bytes May 18, 2023 L15.69

PAGE TABLE EXAMPLE ■ With 2<sup>20</sup> slots in our page table for a single process ■ Each slot (i.e. entry) dereferences a VPN VPN<sub>0</sub> Each entry provides a physical frame number VPN<sub>1</sub>  $VPN_2$ Each entry requires 4 bytes (32 bits) 20 for the PFN on a 4GB system with 4KB pages ---• 12 for the offset which is preserved . (note we have no status bits, so this is inrealistically small)  ${\rm VPN}_{\rm 1048576}$ How much memory is required to store the page table for 1 process? • Hint: # of entries x space per entry 4,194,304 bytes (or 4MB) to index one process May 18, 2023 L15.70

70

72

69

NOW FOR AN ENTIRE OS ■ If 4 MB is required to store one process Consider how much memory is required for an entire OS? • With for example 100 processes... ■ Page table memory requirement is now 4MB x 100 = 400MB If computer has 4GB memory (maximum for 32-bits), the page table consumes 10% of memory 400 MB / 4000 GB Is this efficient? May 18, 2023 L15.71 71

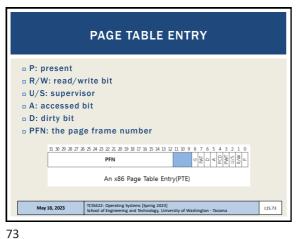

(2) WHAT'S ACTUALLY IN THE PAGE TABLE ■ Page table is data structure used to map virtual page numbers (VPN) to the physical address (Physical Frame Number PFN) Linear page table → simple array ■ Page-table entry • 32 bits for capturing state 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 An x86 Page Table Entry(PTE) TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma May 18, 2023 L15.72

PAGE TABLE ENTRY - 2 Common flags: • Valid Bit: Indicating whether the particular translation is valid. Protection Bit: Indicating whether the page could be read from, written to, or executed from Present Bit: Indicating whether this page is in physical memory or on disk(swapped out) Dirty Bit: Indicating whether the page has been modified since it was brought into memory Reference Bit(Accessed Bit): Indicating that a page has been accessed May 18, 2023 ersity of Washington - Tacoma

74

(4) DOES PAGING MAKE THE SYSTEM TOO SLOW? ■ Translation Issue #1: Starting location of the page table is needed HW Support: Page-table base register  $VPO \rightarrow PF3$ stores active process VP1 → PF7 Facilitates translation VP2 → PF5 Stored in RAM → VP3 → PF2 ■ Issue #2: Each memory address translation for paging requires an extra memory reference HW Support: TLBs (Chapter 19) TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Taco May 18, 2023 L15.76

76

```

PAGING MEMORY ACCESS

VPN = (VirtualAddress & VPN_MASK) >> SHIFT

// Form the address of the page-table

PTEAddr = PTBR + (VPN * sizeof(PTE))

// Fetch the PTE

PTE = AccessMemory(PTEAddr)

7.

8.

9.

10.

// Check if process can access the page

if (PTE.Valid == False)

RaiseException(SEGMENTATION_FAULT)

else if (CanAccess(PTE.ProtectBits) == False)

RaiseException(PROTECTION_FAULT)

12.

13.

14.

15.

16.

17.

18.

19.

offset = VirtualAddress & OFFSET_MASK

PhysAddr = (PTE.PFN << PFN_SHIFT) | offset

Register = AccessMemory(PhysAddr)

TCSS422: Operating Systems [Spring 2023]

School of Engineering and Technology, University of Washington - Tacoma

May 18, 2023

L15.77

```

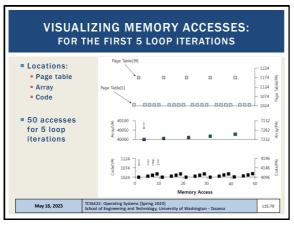

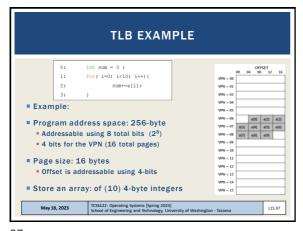

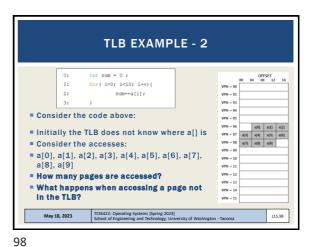

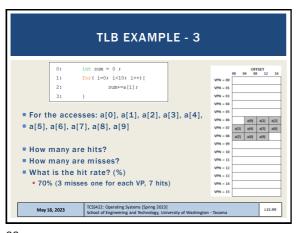

**COUNTING MEMORY ACCESSES** Example: Use this Array initialization Code int array[1000]; for (i = 0; i < 1000; i++)

array[i] = 0; Assembly equivalent: 0x1024 movl S0x0, (%edi, %eax, 4) 0x1028 incl %eax 0x102c cmpl \$0x03e8, %eax 0x1030 jne 0x1024 TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma May 18, 2023 L15.78

77 78

For the 4GB computer example, how many bits are required for the VPN? 24 VPN bits (indexes 2^24 locations) 16 VPN bits (indexes 2^16 locations) 20 VPN bits (indexes 2^20 locations) 12 VPN bits (indexes 2<sup>12</sup> locations) None of the above

For the 4GB computer example, how many bits are available for page status bits? 32 - 12 VPN bits = 20 status bits 32 - 24 VPN bits = 8 status bits 32 - 16 VPN bits = 16 status bits 32 - 20 VPN bits = 12 status bits None of the above

82

84

81

For the 4GB computer, how much space does this page table require? (number of page table entries x size of page table entry) 2^20 entries x 4b = 4 MB 2^12 entries x 4b = 16 KB 2^16 entries x 4b = 256 KB 2^24 entries x 4b = 64 MB None of the above TCSS422: Operating Systems [Spring 2023]

Onservourse Entitle of the Commission of t 83

For the 4GB computer, how many page tables (for user processes) would fill the entire 4GB of memory? 4 GB / 16 KB = 65,536 4 GB / 64 MB = 256 4GB / 256 KB = 16,384 4GB / 4MB = 1,024 None of the above

**OBJECTIVES - 5/18** Questions from 5/16 Assignment 2 - June 2 Quiz 3 - Synchronized Array - June 2 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 26 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 16: Segmentation ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables May 18, 2023 TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma 115.86

86

TRANSLATION LOOKASIDE BUFFER Legacy name... ■ Better name, "Address Translation Cache" ■TLB is an on CPU cache of address translations ■virtual → physical memory May 18, 2023 L15.88

88

**TRANSLATION LOOKASIDE BUFFER - 2** ■ Goal: Reduce access 1174 to the page - 1124 tables 1074 0000 0000 0000 0000 1024 Example: 50 RAM accesses for first 5 for-loop 7282 iterations ■ Move lookups from RAM to TLB by caching page table entries May 18, 2023 L15.89

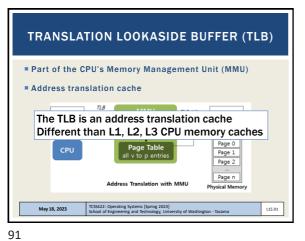

TRANSLATION LOOKASIDE BUFFER (TLB) ■ Part of the CPU's Memory Management Unit (MMU) Address translation cache Physical Address Page 0 Page 1 Page 2 Page n Address Translation with MMU TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma May 18, 2023 L15.90

89 90

```

TLB - ADDRESS TRANSLATION CACHE

■ Key detail:

For a TLB miss, we first access the page table in RAM to

populate the TLB... we then requery the TLB

All address translations go through the TLB

TCSS422: Operating Systems [Spring 2023]

School of Engineering and Technology, University of Washington - Tacoma

May 18, 2023

L15.95

```

**OBJECTIVES - 5/18** ■ Questions from 5/16 Assignment 2 - June 2 Quiz 3 - Synchronized Array - June 2 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 26 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 16: Segmentation ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables Multi-level Page Tables N-level Page Table May 18, 2023 TCSS422: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma L15.96

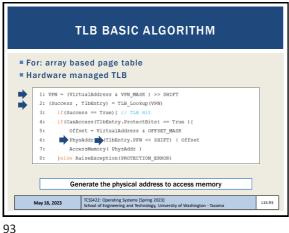

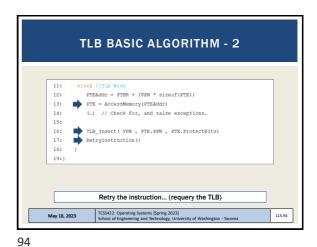

95 96

99 100

101 102

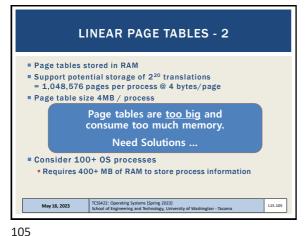

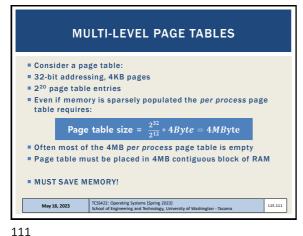

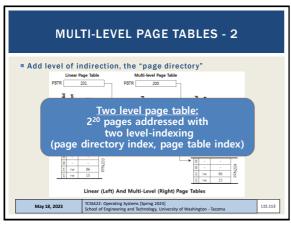

LINEAR PAGE TABLES - 2

■ Page tables stored in RAM

■ Support potential storage of 2<sup>20</sup> translations

= 1,048,576 pages per process @ 4 bytes/page

■ Page table size 4MB / process

Page table size = 2<sup>32</sup>/<sub>212</sub> \* 4Byte = 4MByte

■ Consider 100+ OS processes

■ Requires 400+ MB of RAM to store process information

May 18, 2023 | 10.55432- Operating Systems (Spring 2023) | School of Engineering and Technology, University of Washington - Tacoma | 115.104

103 104

OBJECTIVES - 5/18

Questions from 5/16

Assignment 2 - June 2

Quiz 3 - Synchronized Array - June 2

Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 26

Assignment 3 (as a Tutorial) to be posted...

Chapter 16: Segmentation

Chapter 17: Free Space Management

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables

May 18, 2023

May 18, 2023

School of Engineering souteres [Soring 2023]

School of Engineering and Technology, University of Washington - Tacoma

105 106

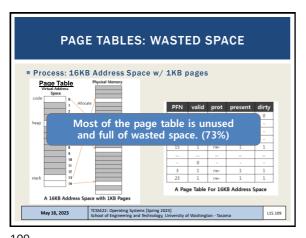

PAGE TABLES: WASTED SPACE

Process: 16KB Address Space w/ 1KB pages

Page Table

Process: 16KB Address Space w/ 1KB pages

Page Table

Process: 16KB Address Space w/ 1KB pages

A 16KB Address Space with 1KB pages

A 16KB Address Space with 1KB pages

TCSS42: Operating Systems (Spring 2023)

School of Engineering and Technology, University of Washington - Tacoma

L15.108

107 108

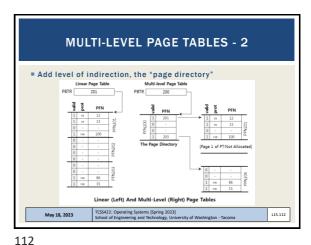

11

113 114

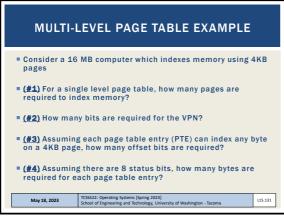

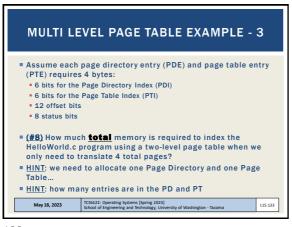

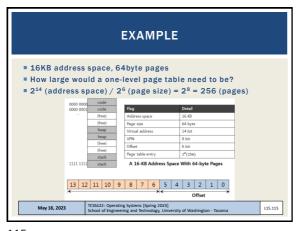

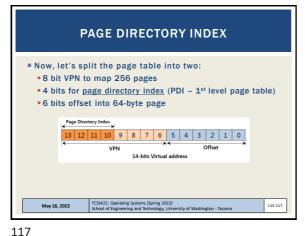

PAGE TABLE INDEX

# 4 bits page directory index (PDI – 1st level)

# 4 bits page table index (PTI – 2nd level)

# 5 page Directory Index (PTI – 2nd level)

# 6 page Directory Index (PTI – 2nd level)

# 7 page Directory Index (PTI – 2nd level)

# 8 page Table Index (PTI – 2nd level)

# 9 page Table Index (PTI – 3nd level)

# Offset

# To dereference one 64-byte memory page,

# We need one page directory entry (PDE)

# One page table Index (PTI) – can address 16 pages

# 1 TCSS422: Operating Systems (Spring 2023)

# School of Engineering and Technology, University of Washington - Tacoma (155.118)

118

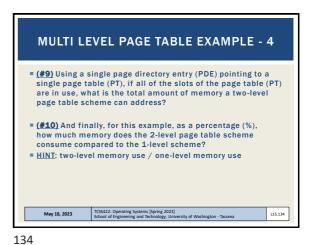

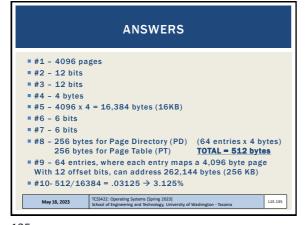

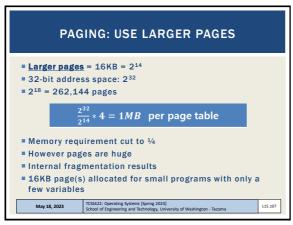

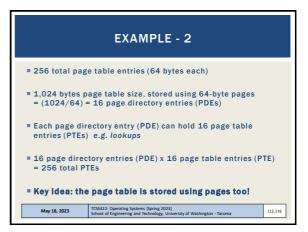

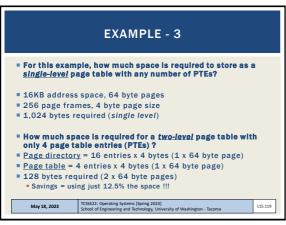

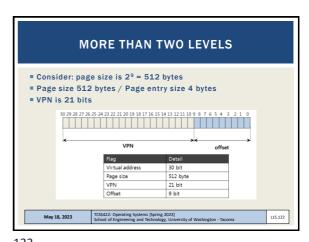

32-BIT EXAMPLE

Consider: 32-bit address space, 4KB pages, 220 pages

Only 4 mapped pages

Single level: 4 MB (we've done this before)

Two level: (old VPN was 20 bits, split in half)

Page directory = 210 entries x 4 bytes = 1 x 4 KB page

Page table = 4 entries x 4 bytes (mapped to 1 4KB page)

KB (8,192 bytes) required

Savings = using just .78 % the space !!!

100 sparse processes now require < 1MB for page tables

May 18, 2023

1CSS422: Operating Systems (Spring 2023)

School of Engineering and Technology, University of Washington - Tacoma

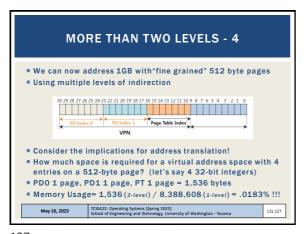

119 120

123 124

125 126

INVERTED PAGE TABLES

\*\*Keep a single page table for each physical page of memory

\*\*Consider 4GB physical memory

\*\*Using 4KB pages, page table requires 4MB to map all of RAM

\*\*Page table stores

\*\*Which process uses each page

\*\*Which process virtual page (from process virtual address space) maps to the physical page

\*\*All processes share the same page table for memory mapping, kernel must isolate all use of the shared structure

\*\*Finding process memory pages requires search of 2<sup>20</sup> pages

\*\*Hash table: can index memory and speed lookups

\*\*May 18, 2023\*\*

\*\*Install process speed lookups

\*\*Install process speed l

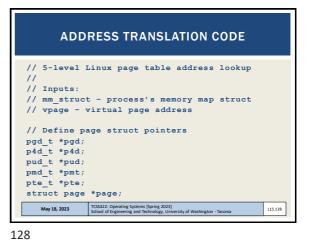

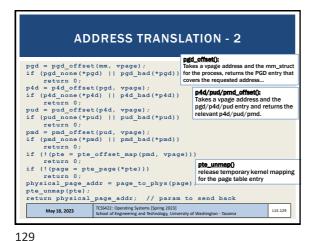

130

.23