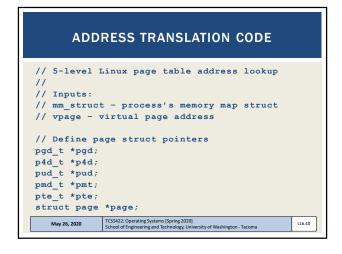

```

ADDRESS TRANSLATION - 2

pgd_offset():

pgd = pgd_offset(mm, vpage);

if (pgd_none(*pgd) || pgd_bad(*pgd))

Takes a vpage address and the mm_struct for the process, returns the PGD entry that

return 0:

covers the requested address...

p4d = p4d_offset(pgd, vpage);

if (p4d_none(*p4d) || p4d_bad(*p4d))

p4d/pud/pmd_offset():

Takes a vpage address and the

pgd/p4d/pud entry and returns the

relevant p4d/pud/pmd.

return 0;

pud = pud_offset(p4d, vpage);

if (pud_none(*pud) || pud_bad(*pud))

return 0;

pmd = pmd_offset(pud, vpage);

if (pmd_none(*pmd) || pmd_bad(*pmd))

return 0;

if (!(pte = pte offset map(pmd, vpage)))

return 0

pte_unmap()

oorary kernel mapping

physical page_addr = page_to_phys(page)

_page_addr; // param to send back

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

May 26, 2020

L16.41

```

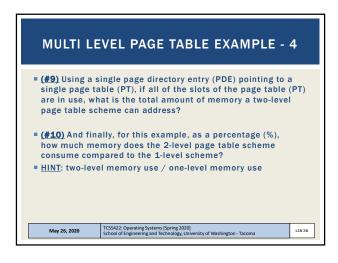

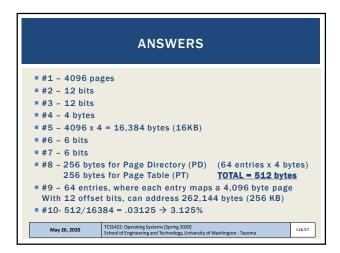

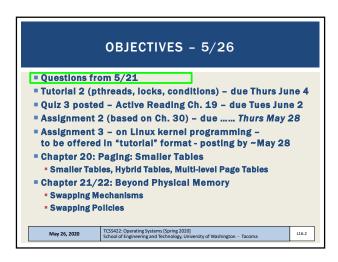

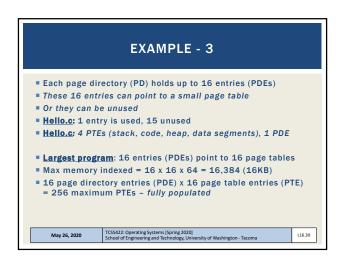

(#9) For a 2-level page table, using a single Page

Directory Entry (PDE) pointing to a single Page Table

(PT), where all slots of the PT are used, how much

memory can be addressed?

16 entries x 4096

bytes = 64 KB

32 entries x 4096

bytes = 128 KB

64 entries x 4096

bytes = 126 KB

256 entries x 4096

bytes = 1024 KB

4096 entries x 4096

bytes = 10384 KB

1038 entries x 4096

bytes = 16384 KB

1038 entries x 4096

bytes = 16384 KB

1038 entries x 4096

bytes = 16384 KB

(#10) For the previous example where one PDE points to a fully used PT, what percentage of memory does the 2-level page table consume vs. a 1-level page table?

256 / 16384

512 / 16384

1024 / 16384

100%

1084 26,2020r the procentariog systems (Spring 2020)

1084 26,2020r the procentariog systems (Spring 2020)

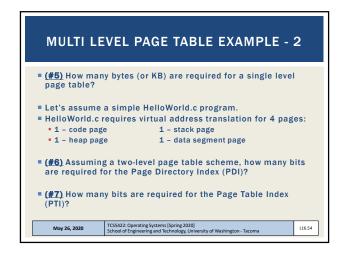

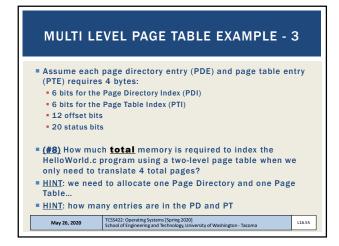

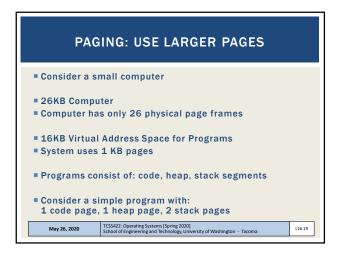

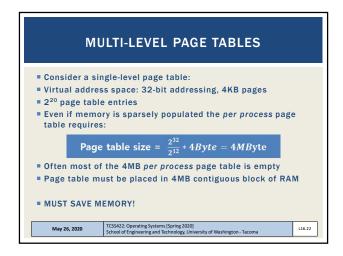

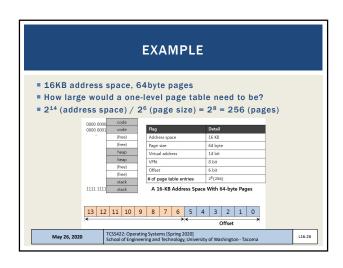

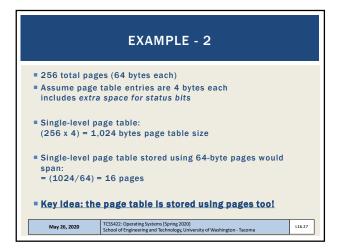

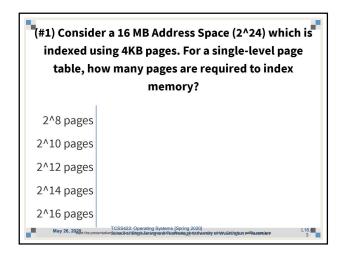

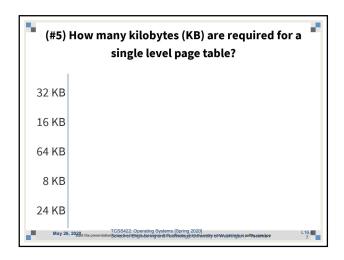

MULTI-LEVEL PAGE TABLE EXAMPLE

Consider a 16 MB computer which indexes memory using 4KB pages

(#1) For a single level page table, how many pages are required to index memory?

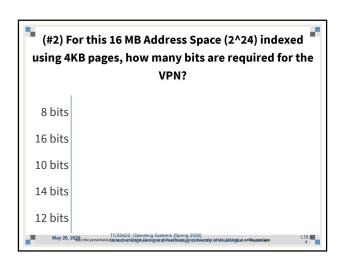

(#2) How many bits are required for the VPN?

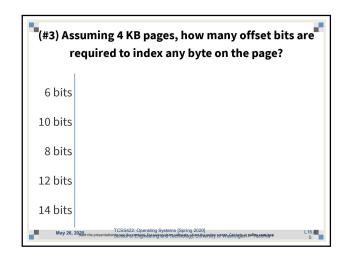

(#3) Assuming each page table entry (PTE) can index any byte on a 4KB page, how many offset bits are required?

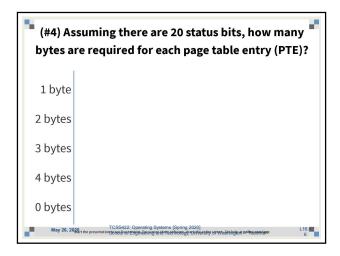

(#4) Assuming there are 20 status bits, how many bytes are required for each page table entry?