# TCSS 422: OPERATING SYSTEMS

# Introduction to Paging, Translation Lookaside Buffer (TLB)

Wes J. Lloyd School of Engineering and Technology University of Washington - Tacoma

111111111111

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

# **OBJECTIVES - 5/21**

- Questions from 5/19

- Tuesday Class Activity: (Submit by May 22 11:59pm AOE)

- Tutorial 2 posted (pthreads, locks, conditions)

- Quiz 3 posted Active Reading Chapter 19

- Assignment 2 (based on Ch. 30)

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Tradeoffs, Context Switch

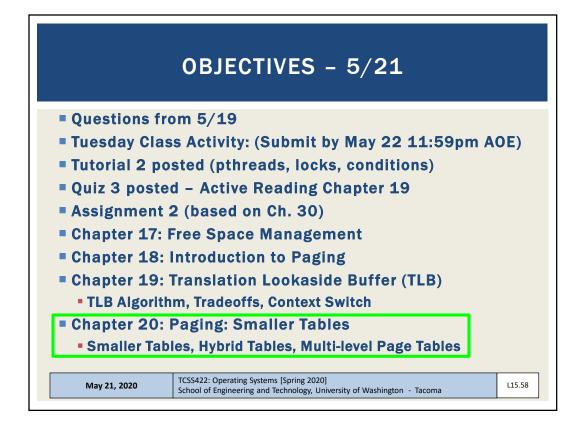

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Hybrid Tables, Multi-level Page Tables

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

# MATERIAL / PACE

- Please classify your perspective on material covered in today's class (46 respondents):

- 1-mostly review, 5-equal new/review, 10-mostly new

- Average  $6.53 (\downarrow from 6.74)$

- Please rate the pace of today's class:

- 1-slow, 5-just right, 10-fast

- Average 5.66 (\$\psi\$ from 5.77)

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

# FEEDBACK FROM 5/19

• Questions ?

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

L15.4

#### NOTE ON ASSIGNMENT 1 - EXTRA CREDIT

- Some programs did not include comments at the top of mash.c to notify graders which extra credit features to grade

- This requirement was documented in Assignment #1:

#### \* - EXTRA CREDIT- COMMENTS ARE REQUIRED:

Comments must be included at the top of the mash.c file to indicate which extra credit features (EC1, EC2, EC3, and EC4) have been implemented to receive credit. If there is no indication that extra credit features are implemented, no extra credit will be awarded.

Example of required comment:

// EXTRA CREDIT FEATURES: EC2, EC3 implemented

- If missing points, to request extra credit be graded:

- In Canvas, go to assignment #1, click: "Submission Details" link on the RIGHT

- Add a comment in the "Add a comment" box

- Indicate which extra credit (EC1, EC2, EC3, EC4) needs graded

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

L15.5

# **OBJECTIVES - 5/21**

- Questions from 5/19

- Tuesday Class Activity: (Submit by May 22 11:59pm AOE)

- Tutorial 2 posted (pthreads, locks, conditions)

- Quiz 3 posted Active Reading Chapter 19

- Assignment 2 (based on Ch. 30)

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Tradeoffs, Context Switch

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Hybrid Tables, Multi-level Page Tables

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

# **OBJECTIVES - 5/21**

- Questions from 5/19

- Tuesday Class Activity: (Submit by May 22 11:59pm AOE)

- Tutorial 2 posted (pthreads, locks, conditions)

- Quiz 3 posted Active Reading Chapter 19

- Assignment 2 (based on Ch. 30)

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Tradeoffs, Context Switch

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Hybrid Tables, Multi-level Page Tables

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

L15.7

# OBJECTIVES - 5/21

- Questions from 5/19

- Tuesday Class Activity: (Submit by May 22 11:59pm AOE)

- Tutorial 2 posted (pthreads, locks, conditions)

- Quiz 3 posted Active Reading Chapter 19

- Assignment 2 (based on Ch. 30)

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Tradeoffs, Context Switch

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Hybrid Tables, Multi-level Page Tables

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

# **OBJECTIVES - 5/21**

- Questions from 5/19

- Tuesday Class Activity: (Submit by May 22 11:59pm AOE)

- Tutorial 2 posted (pthreads, locks, conditions)

- Quiz 3 posted Active Reading Chapter 19

- Assignment 2 (based on Ch. 30)

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Tradeoffs, Context Switch

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Hybrid Tables, Multi-level Page Tables

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

# OBJECTIVES - 5/21 Questions from 5/19 Tuesday Class Activity: (Submit by May 22 11:59pm AOE) Tutorial 2 posted (pthreads, locks, conditions) Quiz 3 posted - Active Reading Chapter 19 Assignment 2 (based on Ch. 30) Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Tradeoffs, Context Switch Chapter 20: Paging: Smaller Tables Smaller Tables, Hybrid Tables, Multi-level Page Tables

#### **SEGREGATED LISTS**

- OS provides object caches:

- Collections of pre-initialized ready-to-use objects

- Allocated for popular OS data types/structures

- e.g. for kernel objects such as locks, inodes, etc.

- Managed as segregated free lists

- OS DESIGN QUESTION:

How much memory should be dedicated for OS object caches?

- If a given cache is low in memory, can request "slabs" of memory from the general allocator for caches.

- General allocator will reclaim slabs when not used

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.13

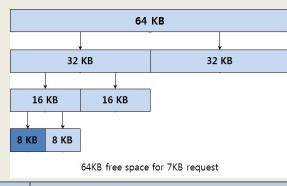

#### **BUDDY ALLOCATION**

- Binary buddy allocation

- Divides free space by two to find a block that is big enough to accommodate the request; the next split is too small...

- Consider a 7KB request

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

#### **BUDDY ALLOCATION - 2**

- Buddy allocation: suffers from internal fragmentation

- Allocated fragments, typically too large

- Coalescing is simple

- Two adjacent blocks are promoted up

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.15

A computer system manages program memory using three separate segments for code, stack, and the heap. The codesize of a program is 1KB but the minimal segment available is 16KB. This is an example of:

External fragmentation Binary buddy allocation Internal fragmentation Coalescing **Splitting**

# **OBJECTIVES - 5/21**

- Questions from 5/19

- Tuesday Class Activity: (Submit by May 22 11:59pm AOE)

- Tutorial 2 posted (pthreads, locks, conditions)

- Quiz 3 posted Active Reading Chapter 19

- Assignment 2 (based on Ch. 30)

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Tradeoffs, Context Switch

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Hybrid Tables, Multi-level Page Tables

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

L15.19

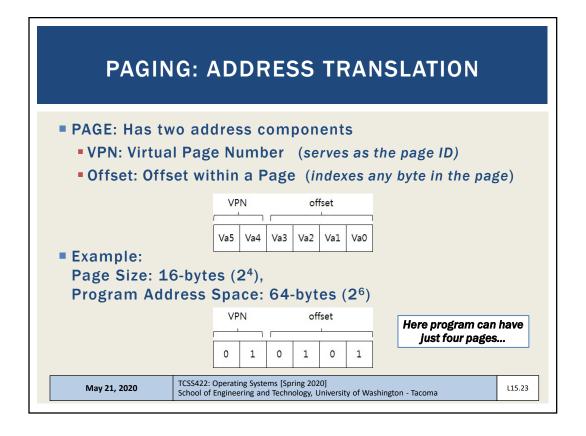

#### **PAGING**

- Split up address space of process into <u>fixed sized pieces</u> called pages

- Alternative to <u>variable sized pieces</u> (Segmentation) which suffers from significant fragmentation

- Physical memory is split up into an array of fixed-size slots called page frames.

- Each process has a page table which translates virtual addresses to physical addresses

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

L15.21

#### **ADVANTAGES OF PAGING**

- Flexibility

- Abstracts the process address space into pages

- No need to track direction of HEAP / STACK growth

- Just add more pages...

- No need to store unused space

- As with segments...

- Simplicity

- Pages and page frames are the same size

- Easy to allocate and keep a free list of pages

May 21, 2020 TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

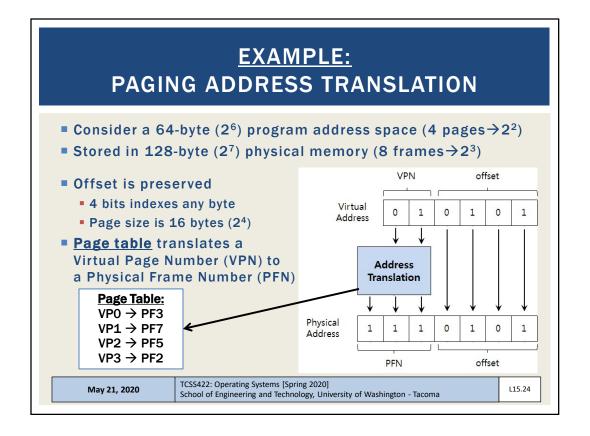

Page Table: **PAGING: EXAMPLE**  $VP0 \rightarrow PF3$  $VP1 \rightarrow PF7$ VP2 → PF5 VP3 → PF2 Consider a 128 byte (27) address space with 16-byte (24) pages page frame 0 of reserved for OS physical memory 16 ■ Consider a 64-byte (2<sup>6</sup>) (unused) page frame 1 program address space page frame 2 page 3 of AS page 0 of AS page frame 3 64 0 (page 0 of page frame 4 (unused) the address space) 16 80 page 2 of AS page frame 5 (page 1) 32 96 (page 2) (unused) page frame 6 48 112 (page 3) page 1 of AS page frame 7 128 A Simple 64-byte Address Space 64-Byte Address Space Placed In Physical Memory TCSS422: Operating Systems [Spring 2020] May 21, 2020 L15.22 School of Engineering and Technology, University of Washington - Tacoma

# PAGING DESIGN QUESTIONS

- (1) Where are page tables stored?

- (2) What are the typical contents of the page table?

- (3) How big are page tables?

- (4) Does paging make the system too slow?

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.25

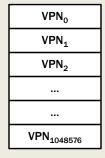

# (1) WHERE ARE PAGE TABLES STORED?

- Example:

- Consider a 32-bit process address space (4GB=2<sup>32</sup> bytes)

- With 4 KB pages (4KB=2<sup>12</sup> bytes)

- 20 bits for VPN (2<sup>20</sup> pages)

- 12 bits for the page offset (2<sup>12</sup> unique bytes in a page)

- Page tables for each process are stored in RAM

- Support potential storage of 2<sup>20</sup> translations

- = 1,048,576 pages per process

- Each page has a page table entry size of 4 bytes

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

#### PAGE TABLE EXAMPLE

- With 2<sup>20</sup> slots in our page table for a single process

- Each slot (i.e. entry) dereferences a VPN

- Each entry provides a physical frame number

- Each entry requires 4 bytes (32 bits)

- 20 for the PFN on a 4GB system with 4KB pages

- 12 for the offset which is preserved

- (note we have no status bits, so this is unrealistically small)

- How much memory is required to store the page table for 1 process?

- Hint: # of entries x space per entry

- 4,194,304 bytes (or 4MB) to index one process

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.27

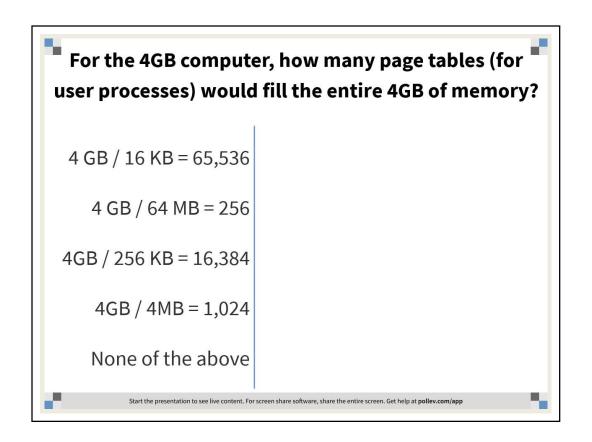

#### NOW FOR AN ENTIRE OS

- If 4 MB is required to store one process

- Consider how much memory is required for an entire OS?

- With for example 100 processes...

- Page table memory requirement is now 4MB x 100 = 400MB

- If computer has 4GB memory (maximum for 32-bits), the page table consumes 10% of memory

400 MB / 4000 GB

Is this efficient?

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

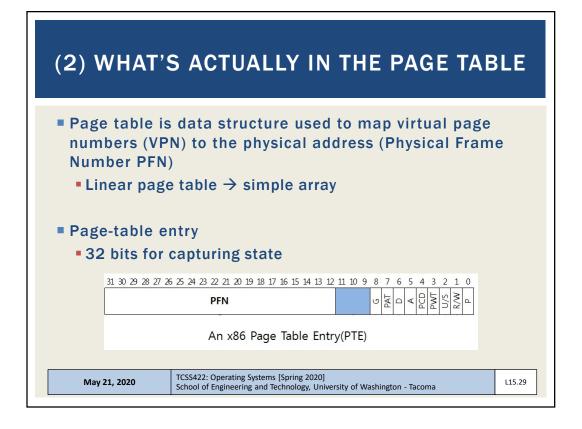

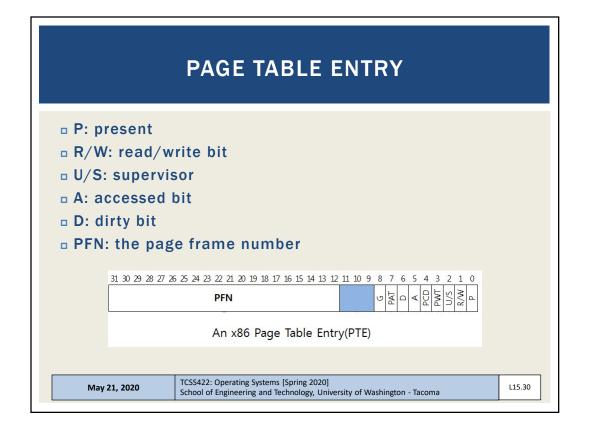

#### **PAGE TABLE ENTRY - 2**

- Common flags:

- Valid Bit: Indicating whether the particular translation is valid.

- Protection Bit: Indicating whether the page could be read from, written to, or executed from

- Present Bit: Indicating whether this page is in physical memory or on disk(swapped out)

- Dirty Bit: Indicating whether the page has been modified since it was brought into memory

- Reference Bit(Accessed Bit): Indicating that a page has been accessed

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

# (3) HOW BIG ARE PAGE TABLES?

- Page tables are too big to store on the CPU

- Page tables are stored using physical memory

- Paging supports efficiently storing a sparsely populated address space

- Reduced memory requirement Compared to base and bounds, and segments

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.33

# (4) DOES PAGING MAKE THE SYSTEM TOO SLOW?

- Translation

- Issue #1: Starting location of the page table is needed

- HW Support: Page-table base register

stores active process

Facilitates translation

Page Table:  $VP0 \rightarrow PF3$

$VP1 \rightarrow PF7$

VP2 → PF5

VP3 → PF2

Issue #2: Each memory address translation for paging requires an extra memory reference

Stored in RAM →

HW Support: TLBs (Chapter 19)

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

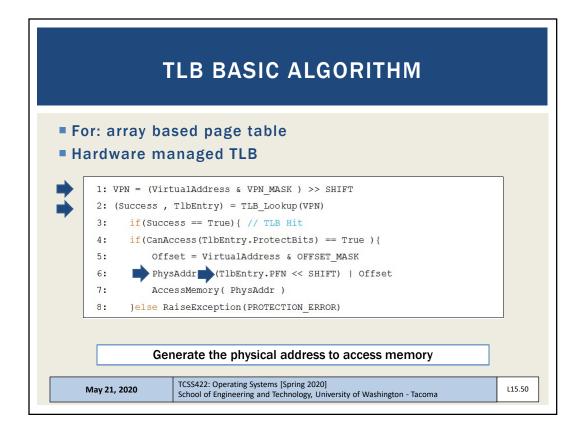

```

PAGING MEMORY ACCESS

// Extract the VPN from the virtual address

2.

VPN = (VirtualAddress & VPN_MASK) >> SHIFT

3.

4.

// Form the address of the page-table entry (PTE)

5.

PTEAddr = PTBR + (VPN * sizeof(PTE))

// Fetch the PTE

8.

PTE = AccessMemory(PTEAddr)

9.

// Check if process can access the page

10.

if (PTE.Valid == False)

11.

RaiseException(SEGMENTATION_FAULT)

13.

else if (CanAccess(PTE.ProtectBits) == False)

14.

RaiseException(PROTECTION_FAULT)

15.

else

16.

// Access is OK: form physical address and fetch it

offset = VirtualAddress & OFFSET_MASK

17.

18.

PhysAddr = (PTE.PFN << PFN_SHIFT) | offset

19.

Register = AccessMemory(PhysAddr)

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

May 21, 2020

L15.35

```

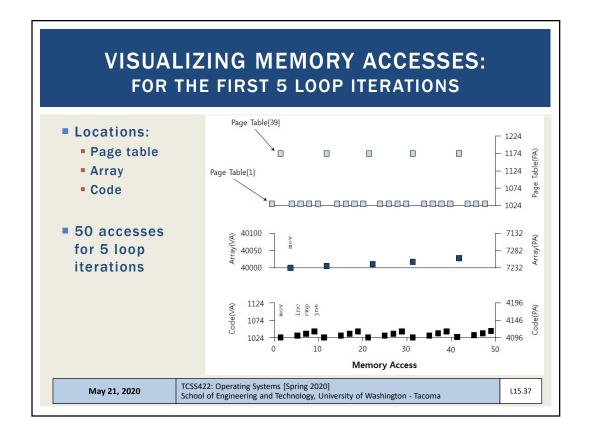

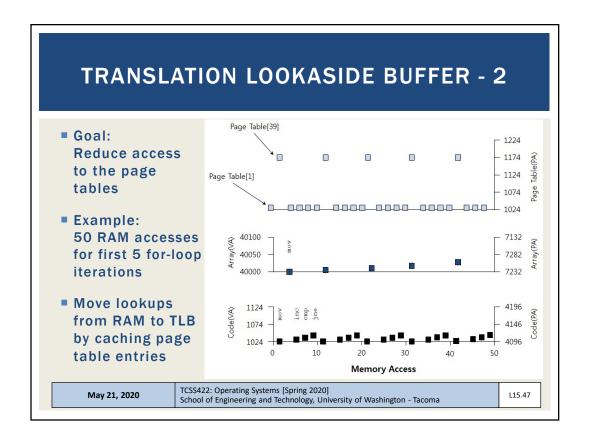

#### **COUNTING MEMORY ACCESSES**

Example: Use this Array initialization Code

Assembly equivalent:

```

0x1024 movl $0x0,(%edi,%eax,4)

0x1028 incl %eax

0x102c cmpl $0x03e8,%eax

0x1030 jne 0x1024

```

May 21, 2020 TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

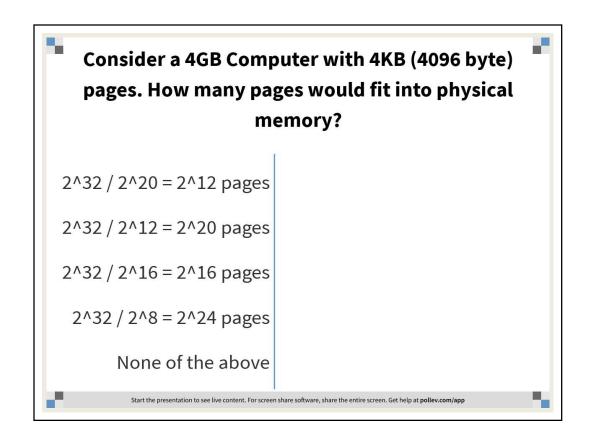

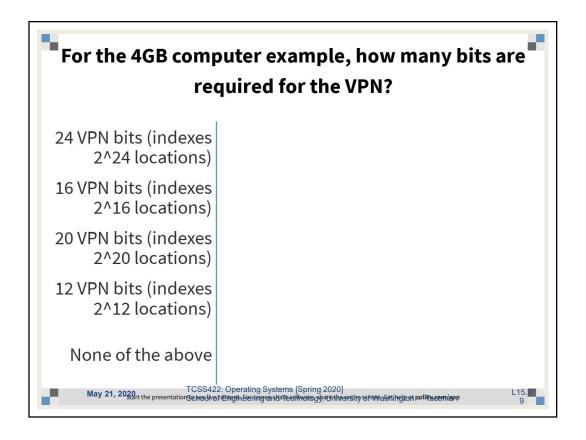

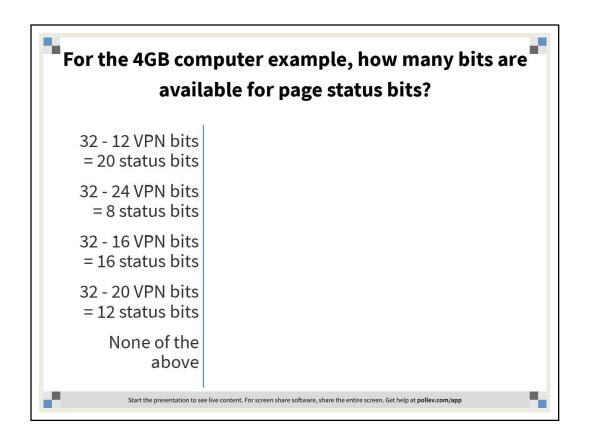

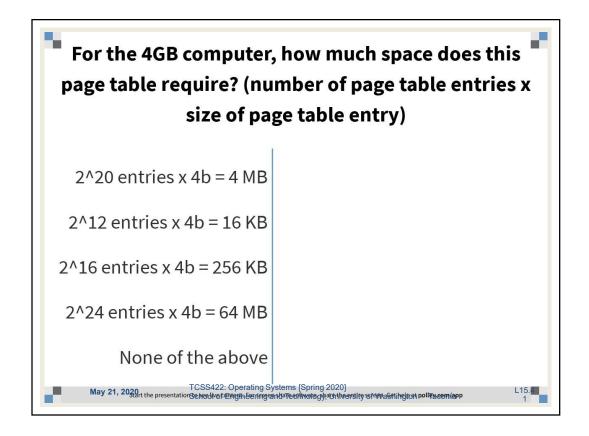

#### PAGING SYSTEM EXAMPLE

- Consider a 4GB Computer:

- With a 4096-byte page size (4KB)

- How many pages would fit in physical memory?

- Now consider a page table:

- For the page table entry, how many bits are required for the

- If we assume the use of 4-byte (32 bit) page table entries, how many bits are available for status bits?

- How much space does this page table require? # of page table entries x size of page table entry

- How many page tables (for user processes) would fill the entire 4GB of memory?

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

# **OBJECTIVES - 5/21**

- Questions from 5/19

- Tuesday Class Activity: (Submit by May 22 11:59pm AOE)

- Tutorial 2 posted (pthreads, locks, conditions)

- Quiz 3 posted Active Reading Chapter 19

- Assignment 2 (based on Ch. 30)

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Tradeoffs, Context Switch

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Hybrid Tables, Multi-level Page Tables

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

L15.45

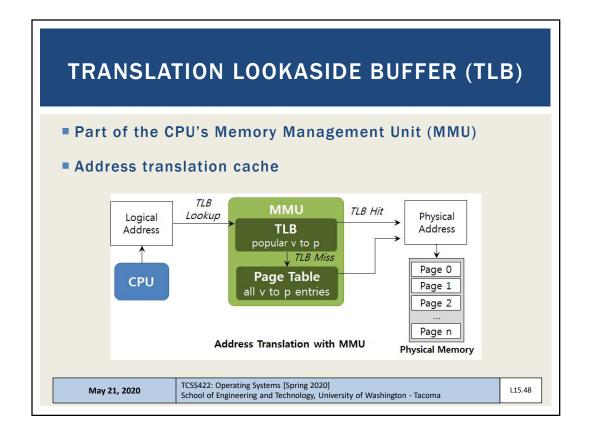

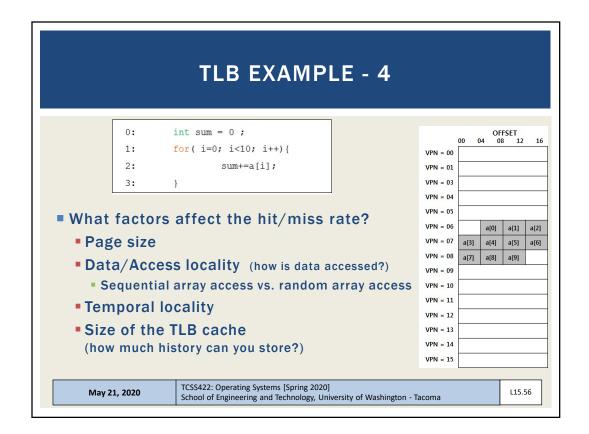

### TRANSLATION LOOKASIDE BUFFER

- Legacy name...

- Better name, "Address Translation Cache"

- ■TLB is an on CPU cache of address translations

- ■virtual → physical memory

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

# TLB - ADDRESS TRANSLATION CACHE Key detail: For a TLB miss, we first access the page table in RAM to populate the TLB... we then requery the TLB All address translations go through the TLB TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

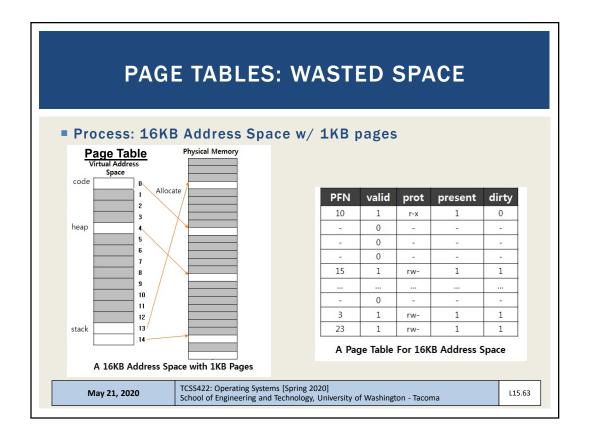

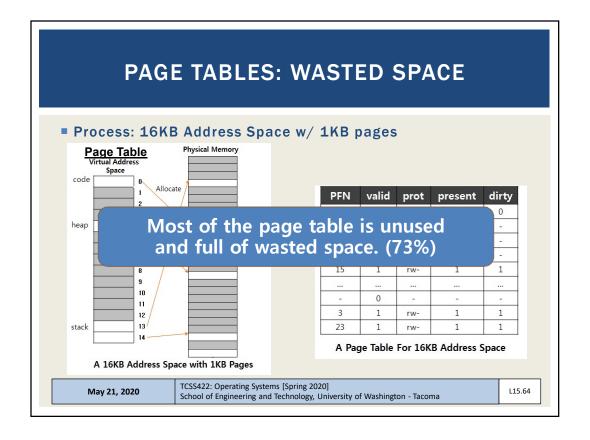

#### LINEAR PAGE TABLES

- Consider array-based page tables:

- Each process has its own page table

- 32-bit process address space (up to 4GB)

- With 4 KB pages

- 20 bits for VPN

- 12 bits for the page offset

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.59

#### **LINEAR PAGE TABLES - 2**

- Page tables stored in RAM

- Support potential storage of 2<sup>20</sup> translations

- = 1,048,576 pages per process @ 4 bytes/page

- Page table size 4MB / process

Page table size =

$$\frac{2^{32}}{2^{12}} * 4Byte = 4MByte$$

- Consider 100+ OS processes

- Requires 400+ MB of RAM to store process information

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

#### **LINEAR PAGE TABLES - 2**

- Page tables stored in RAM

- Support potential storage of 2<sup>20</sup> translations

- = 1,048,576 pages per process @ 4 bytes/page

- Page table size 4MB / process

Page tables are too big and consume too much memory.

**Need Solutions ...**

- Consider 100+ OS processes

- Requires 400+ MB of RAM to store process information

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.61

#### **PAGING: USE LARGER PAGES**

- Larger pages = 16KB = 2<sup>14</sup>

- 32-bit address space: 2<sup>32</sup>

- $2^{18} = 262,144$  pages

$$\frac{2^{32}}{2^{14}} * 4 = 1MB$$

per page table

- Memory requirement cut to 1/4

- However pages are huge

- Internal fragmentation results

- 16KB page(s) allocated for small programs with only a few variables

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

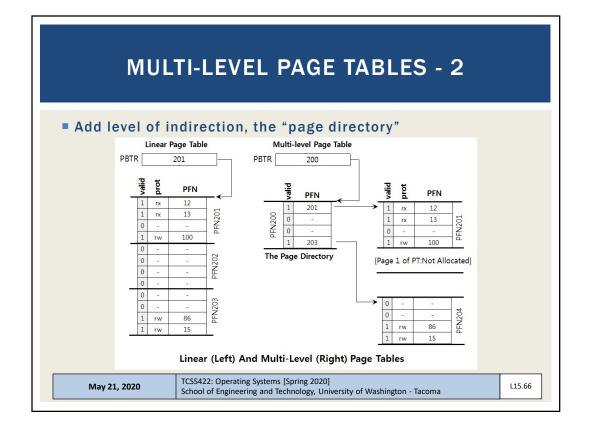

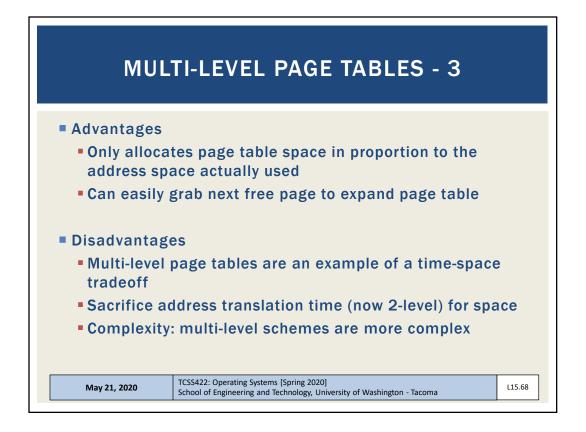

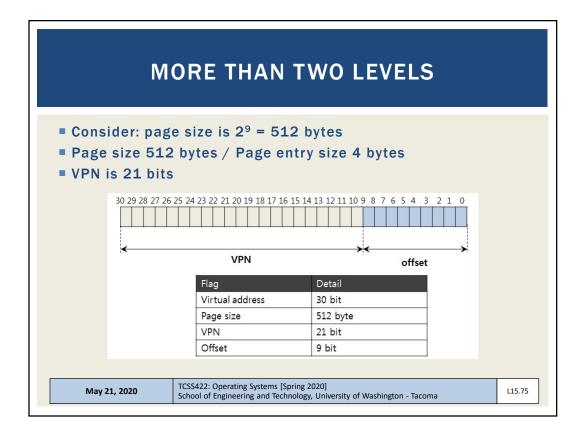

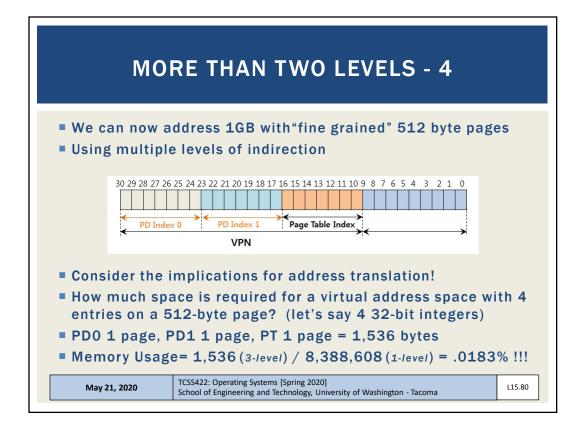

#### **MULTI-LEVEL PAGE TABLES**

- Consider a page table:

- 32-bit addressing, 4KB pages

- 2<sup>20</sup> page table entries

- Even if memory is sparsely populated the per process page table requires:

Page table size =

$$\frac{2^{32}}{2^{12}} * 4Byte = 4MByte$$

- Often most of the 4MB per process page table is empty

- Page table must be placed in 4MB contiguous block of RAM

- MUST SAVE MEMORY!

May 21, 2020 TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

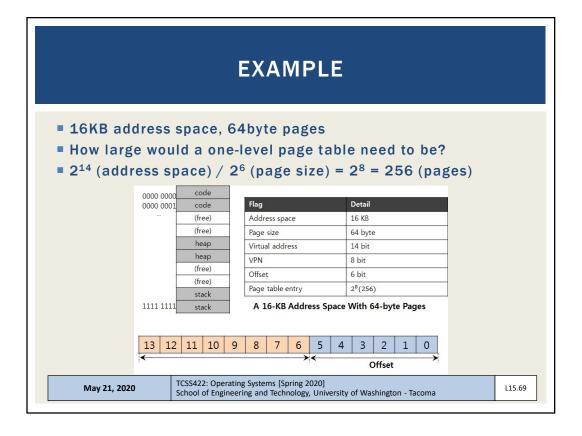

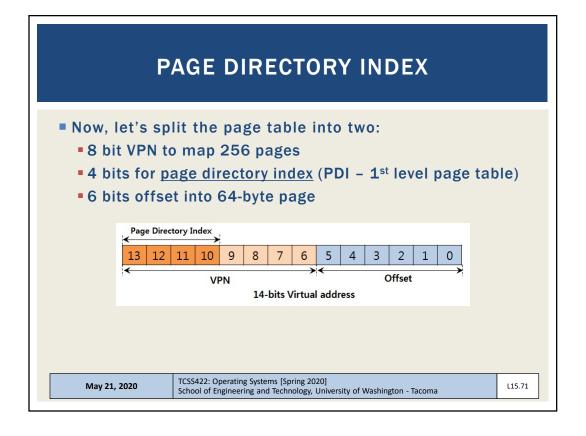

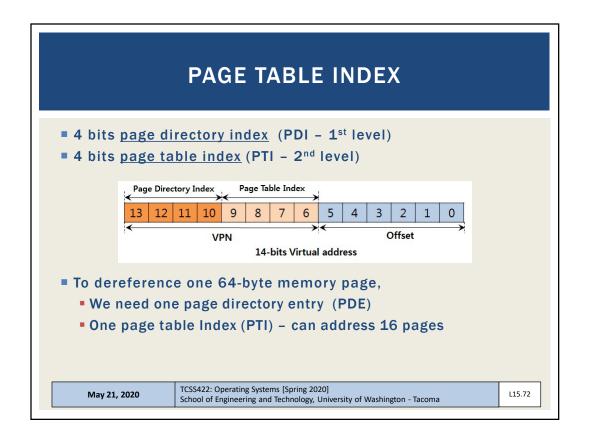

# **EXAMPLE - 2**

- 256 total page table entries (64 bytes each)

- 1,024 bytes page table size, stored using 64-byte pages

(1024/64) = 16 page directory entries (PDEs)

- Each page directory entry (PDE) can hold 16 page table entries (PTEs) e.g. lookups

- 16 page directory entries (PDE) x 16 page table entries (PTE)

256 total PTEs

- Key idea: the page table is stored using pages too!

May 21, 2020 TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

#### **EXAMPLE - 3**

- For this example, how much space is required to store as a <u>single-level</u> page table with any number of PTEs?

- 16KB address space, 64 byte pages

- 256 page frames, 4 byte page size

- 1,024 bytes required (single level)

- How much space is required for a <u>two-level</u> page table with only 4 page table entries (PTEs)?

- Page directory = 16 entries x 4 bytes (1 x 64 byte page)

- Page table = 4 entries x 4 bytes (1 x 64 byte page)

- 128 bytes required (2 x 64 byte pages)

- Savings = using just 12.5% the space !!!

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

L15.73

#### 32-BIT EXAMPLE

- Consider: 32-bit address space, 4KB pages, 2<sup>20</sup> pages

- Only 4 mapped pages

- Single level: 4 MB (we've done this before)

- Two level: (old VPN was 20 bits, split in half)

- Page directory = 2<sup>10</sup> entries x 4 bytes = 1 x 4 KB page

- Page table = 4 entries x 4 bytes (mapped to 1 4KB page)

- 8KB (8,192 bytes) required

- Savings = using just .78 % the space !!!

- 100 sparse processes now require < 1MB for page tables</p>

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

#### **ADDRESS TRANSLATION CODE**

```

// 5-level Linux page table address lookup

//

// Inputs:

// mm_struct - process's memory map struct

// vpage - virtual page address

// Define page struct pointers

pgd_t *pgd;

p4d_t *p4d;

pud_t *pud;

pmd_t *pud;

pmd_t *pmt;

pte_t *pte;

struct page *page;

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

```

#### **ADDRESS TRANSLATION - 2**

```

pgd_offset():

Takes a vpage address and the mm_struct

pgd = pgd_offset(mm, vpage);

if (pgd_none(*pgd) || pgd_bad(*pgd))

for the process, returns the PGD entry that

return 0;

covers the requested address...

p4d = p4d_offset(pgd, vpage);

p4d/pud/pmd_offset():

if (p4d_none(*p4d) || p4d_bad(*p4d))

Takes a vpage address and the

return 0;

pgd/p4d/pud entry and returns the

pud = pud offset(p4d, vpage);

relevant p4d/pud/pmd.

if (pud_none(*pud) || pud_bad(*pud))

return 0;

pmd = pmd offset(pud, vpage);

if (pmd_none(*pmd) || pmd_bad(*pmd))

return 0;

if (!(pte = pte_offset_map(pmd, vpage)))

return 0;

pte_unmap()

if (!(page = pte_page(*pte)))

release temporary kernel mapping

return 0;

for the page table entry

physical_page_addr = page_to_phys(page)

pte unmap(pte);

return physical_page_addr; // param to send back

TCSS422: Operating Systems [Spring 2020]

May 21, 2020

L15.82

School of Engineering and Technology, University of Washington - Tacoma

```

#### **INVERTED PAGE TABLES**

- Keep a single page table for each physical page of memory

- Consider 4GB physical memory

- Using 4KB pages, page table requires 4MB to map all of RAM

- Page table stores

- Which process uses each page

- Which process virtual page (from process virtual address space) maps to the physical page

- All processes share the same page table for memory mapping, kernel must isolate all use of the shared structure

- Finding process memory pages requires search of 2<sup>20</sup> pages

- Hash table: can index memory and speed lookups

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.83

#### **MULTI-LEVEL PAGE TABLE EXAMPLE**

- Consider a 16 MB computer which indexes memory using 4KB pages

- (#1) For a single level page table, how many pages are required to index memory?

- (#2) How many bits are required for the VPN?

- (#3) Assuming each page table entry (PTE) can index any byte on a 4KB page, how many offset bits are required?

- (#4) Assuming there are 8 status bits, how many bytes are required for each page table entry?

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

#### **MULTI LEVEL PAGE TABLE EXAMPLE - 2**

- (#5) How many bytes (or KB) are required for a single level page table?

- Let's assume a simple HelloWorld.c program.

- HelloWorld.c requires virtual address translation for 4 pages:

1 - code page

1 - stack page

1 - heap page

1 - data segment page

- (#6) Assuming a two-level page table scheme, how many bits are required for the Page Directory Index (PDI)?

- (#7) How many bits are required for the Page Table Index (PTI)?

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

L15.85

#### **MULTI LEVEL PAGE TABLE EXAMPLE - 3**

- Assume each page directory entry (PDE) and page table entry (PTE) requires 4 bytes:

- 6 bits for the Page Directory Index (PDI)

- 6 bits for the Page Table Index (PTI)

- 12 offset bits

- 8 status bits

- (#8) How much total memory is required to index the HelloWorld.c program using a two-level page table when we only need to translate 4 total pages?

- HINT: we need to allocate one Page Directory and one Page Table...

- HINT: how many entries are in the PD and PT

May 21, 2020

TCSS422: Operating Systems [Spring 2020]

School of Engineering and Technology, University of Washington - Tacoma

#### **MULTI LEVEL PAGE TABLE EXAMPLE - 4**

- (#9) Using a single page directory entry (PDE) pointing to a single page table (PT), if all of the slots of the page table (PT) are in use, what is the total amount of memory a two-level page table scheme can address?

- (#10) And finally, for this example, as a percentage (%), how much memory does the 2-level page table scheme consume compared to the 1-level scheme?

- HINT: two-level memory use / one-level memory use

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma

L15.87

#### **ANSWERS**

- **#1** 4096 pages

- #2 12 bits

- #3 12 bits

- #4 4 bytes

- $\blacksquare$  #5 4096 x 4 = 16,384 bytes (16KB)

- #6 6 bits

- #7 6 bits

- #8 256 bytes for Page Directory (PD) (64 entries x 4 bytes) 256 bytes for Page Table (PT) TOTAL = 512 bytes

- #9 64 entries, where each entry maps a 4,096 byte page With 12 offset bits, can address 262,144 bytes (256 KB)

- #10-512/16384 = .03125  $\rightarrow$  3.125%

May 21, 2020

TCSS422: Operating Systems [Spring 2020] School of Engineering and Technology, University of Washington - Tacoma