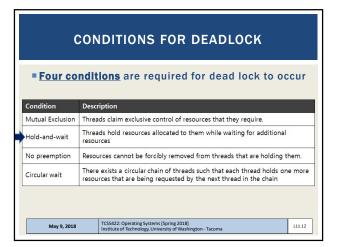

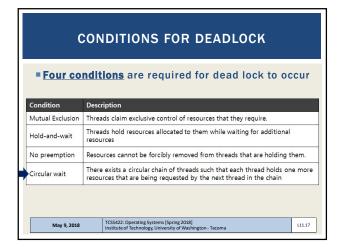

| = Four co        | nditions are required for dead lock to occur                                                                                                        |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Condition        | Description                                                                                                                                         |  |  |  |

| Mutual Exclusion | Threads claim exclusive control of resources that they require.                                                                                     |  |  |  |

| Hold-and-wait    | Threads hold resources allocated to them while waiting for additional<br>resources                                                                  |  |  |  |

| No preemption    | Resources cannot be forcibly removed from threads that are holding them.                                                                            |  |  |  |

| Circular wait    | There exists a circular chain of threads such that each thread holds one more<br>resources that are being requested by the next thread in the chain |  |  |  |

| PREVENTION - MUTUAL EXCLUSION                                                                                                                                                                                                                                                                | PREVEN                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

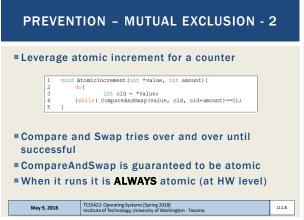

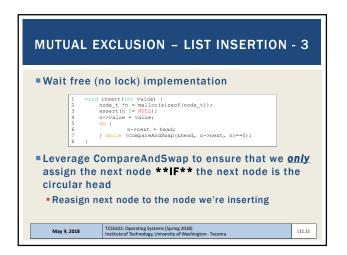

| <ul> <li>Build wait-free data structures         <ul> <li>Eliminate locks altogether</li> <li>Build structures using CompareAndSwap atomic CPU (HW) instruction</li> </ul> </li> <li>C pseudo code for CompareAndSwap (as before)</li> <li>Hardware executes this code atomically</li> </ul> | Leverage :<br>1 void<br>2 void<br>3 4<br>5 j |

| <pre>1 int CompareAndSwap(int *address, int expected, int new){ 2 if(*address == expected) { 3 *address = new; 4 return 1; // success 5 } 6 return 0; 7 }</pre>                                                                                                                              | successfu<br>Compare A<br>When it ru         |

| May 9, 2018         TCS5422: Operating Systems [Spring 2018]<br>Institute of Technology, University of Washington - Tacoma         L11.7                                                                                                                                                     | May 9, 2018                                  |

| PREVEN                                               | TION LOCK - HOLD AND WAIT                                                                              |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|                                                      | ıire all locks atomically<br>a "lock" "lock" ( <i>like a <u>guard lock</u></i> )                       |

|                                                      | <pre>1 lock (prevention) ; 2 lock(L1); 3 lock(L2); 4 - 5 unlock (prevention); </pre>                   |

| <ul> <li>Effective solu<br/>acquiring L1,</li> </ul> | tion – guarantees no race conditions while<br>L2, etc.                                                 |

|                                                      | matter for L1, L2                                                                                      |

|                                                      | LOBAL) lock decreases concurrency of code<br>ock granularity                                           |

|                                                      | consider the Java Vector class                                                                         |

| May 9, 2018                                          | TCSS422: Operating Systems [Spring 2018]<br>Institute of Technology, University of Washington - Tacoma |

| VIA                                                                                              | DEAD<br>INTE                  |                                   |              |         |        | NG     |

|--------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|--------------|---------|--------|--------|

| <ul> <li>Consider</li> <li>Schedu</li> <li>Consider</li> <li>4 Threa</li> <li>2 Locks</li> </ul> | er know<br>this sc<br>ds (T1, | vs whi<br>enario<br>T2, T3        | ch locl<br>: | ks thre | ads us | se     |

| Lock requ                                                                                        | iiremei                       | nts of t                          | thread       | ls:     |        |        |

|                                                                                                  |                               | T1                                | T2           | T3      | T4     |        |

|                                                                                                  | L1                            | yes                               | yes          | no      | no     |        |

|                                                                                                  | L2                            | yes                               | yes          | yes     | no     | ]      |

| May 9, 2018                                                                                      |                               | perating Syster<br>Technology, Ur |              |         | n 2    | L11.19 |

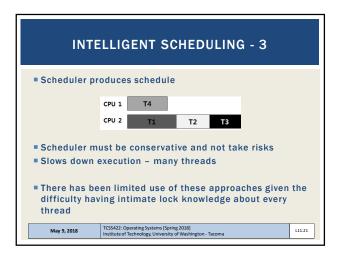

| INTE                                           | ELLIGE                                   | NT SC              | HEDUL                       | ING · | - 2    |

|------------------------------------------------|------------------------------------------|--------------------|-----------------------------|-------|--------|

| Scheduler                                      | produces                                 | s sched            | ule:                        |       |        |

|                                                | CPU 1                                    | Т3                 | T4                          |       |        |

|                                                | CPU 2                                    | T1                 | T2                          | 7     |        |

| <ul><li>No deadloc</li><li>Consider:</li></ul> | k can oc                                 | cur                |                             |       |        |

|                                                |                                          | T1 T2<br>ves ves   | T3<br>Ves                   | T4    |        |

|                                                | /                                        | yes yes<br>yes yes | yes                         | no    |        |

| May 9, 2018                                    | TCSS422: Operatin<br>Institute of Techno |                    | 2018]<br>Washington - Tacon | na    | 111.20 |

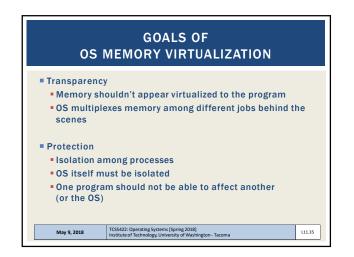

| MI          | EMORY VIRTUALIZATION                                                                                   |        |

|-------------|--------------------------------------------------------------------------------------------------------|--------|

| What is men | nory virtualization?                                                                                   |        |

| Classic use | irtual" memory,<br>of disk space as additional RAM<br>able RAM was low                                 |        |

| Less comm   | on recently                                                                                            |        |

|             |                                                                                                        |        |

| May 9, 2018 | TCSS422: Operating Systems [Spring 2018]<br>Institute of Technology, University of Washington - Tacoma | L11.25 |

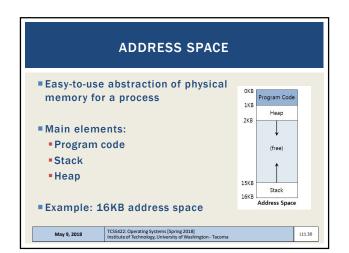

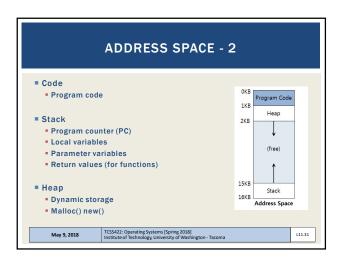

|                                                       | SYSTEM CALLS                                                                                           |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| <pre>brk(), sbrk(</pre>                               | )                                                                                                      |  |

| <ul><li>Used to chang</li><li>Don't use the</li></ul> | e data segment size (the end of the heap)<br>se                                                        |  |

| ■Mmap(), m                                            | unmap()                                                                                                |  |

| Can be used t<br>for a user prop<br>Can be user prop  | o create an extra independent "heap" of memory<br>gram                                                 |  |

| See man page                                          | 2                                                                                                      |  |

| May 9, 2018                                           | TCSS422: Operating Systems [Spring 2018]<br>Institute of Technology, University of Washington - Tacoma |  |

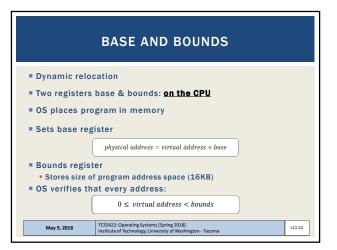

| DYNAMI                                                      | C RELOC                                             | ATION OF PROGRAMS                                                           |  |  |

|-------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Hardware requ                                               | irements:                                           |                                                                             |  |  |

| Requirem                                                    | ents                                                | HW support                                                                  |  |  |

| Privileged mode                                             |                                                     | CPU modes: kernel, user                                                     |  |  |

| Base / bounds registers                                     |                                                     | Registers to support address translation                                    |  |  |

| Translate virtual addr; check if in<br>bounds               |                                                     | Translation circuitry, check limits                                         |  |  |

| Privileged instruction(s) to<br>update base / bounds regs   |                                                     | Instructions for modifying base/bound registers                             |  |  |

| Privileged instruction(s)<br>to register exception handlers |                                                     | Set code pointers to OS code to handle faults                               |  |  |

| Ability to raise exceptions                                 |                                                     | For out-of-bounds memory access, or<br>attempts to access privileged instr. |  |  |

|                                                             | TCCC 422- On anti- Curt                             | (C-ris-2010)                                                                |  |  |

| May 9, 2018                                                 | TCSS422: Operating Syst<br>Institute of Technology, | tems [Spring 2018]<br>University of Washington - Tacoma                     |  |  |

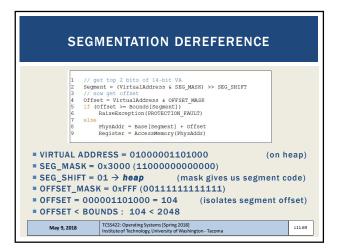

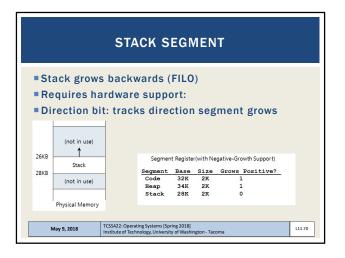

|                              | SEGMENT REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |                              |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|

|                              | erence memory during translation           13         12         11         10         9         7         6         5         4         3         2         1         0           13         12         11         10         9         7         6         5         4         3         2         1         0           Segment         Offset         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         < |                                       |                              |

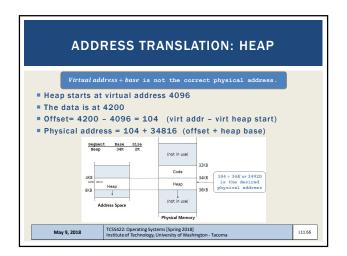

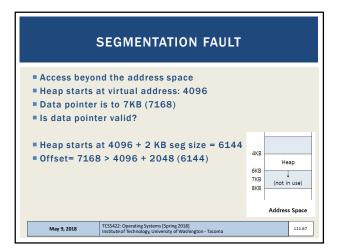

| Remaining bis                | identify segment type<br>ts identify memory offset<br>ual heap address 4200 (010000011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | L01000)                               |                              |

| 13 12 11<br>0 1 0<br>Segment | 10 9 8 7 6 5 4 3 2 1 0<br>0 0 0 0 1 1 0 1 0 0 0 0<br>Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Segment<br>Code<br>Heap<br>Stack<br>- | bits<br>00<br>01<br>10<br>11 |

| May 9, 2018                  | TCSS422: Operating Systems [Spring 2018]<br>Institute of Technology, University of Washington - Tacoma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | L11.68                       |

|                                                                             | COMPACTION                                                                                                                                      |                              |                  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|

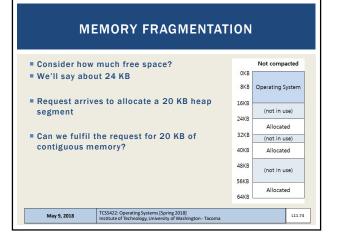

| Supports rear                                                               | ranging memory                                                                                                                                  |                              | Compacted        |

| Can we fulfil<br>contiguous m                                               | the request for 20 KB of emory?                                                                                                                 | 0KB<br>8KB                   | Operating System |

| <ul> <li>Drawback: Co</li> <li>Rearranging</li> <li>64KB is fast</li> </ul> | 16KB<br>24KB<br>32KB                                                                                                                            | Allocated                    |                  |

| most snug se                                                                | b list of free spaces, allocate the sgment for the request                                                                                      | 40KB<br>48KB<br>56KB<br>64KB | (not in use)     |

| <ul> <li>Others: wors</li> <li>May 9, 2018</li> </ul>                       | t fit, first fit (in future chapters)<br>TCSS422: Operating Systems [Spring 2018]<br>Institute of Technology, University of Washington - Tacoma | 04KB                         | L11.75           |