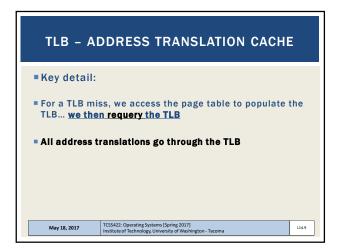

TRANSLATION LOOKASIDE BUFFER

■ Legacy name...

■ Better name, "Address Translation Cache"

■ TLB is an on CPU cache of address translations

■ virtual → physical memory

TCSS42: Operating Systems [Spring 2017]

Institute of Technology, University of Washington-Tacoma

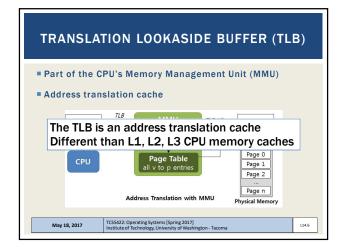

TRANSLATION LOOKASIDE BUFFER (TLB)

Part of the CPU's Memory Management Unit (MMU)

Address translation cache

TLB

Lookup

TLB

Physical

Address

Page 1

Page 2

Page 2

Page 2

Page 1

Page 2

Page 1

Physical Memory

Address Translation with MMU

Physical Memory

Address Translation with MMU

Page 1

Page 1

Page 1

Page 1

Page 2

Page 1

Page 2

Page 1

Physical Memory

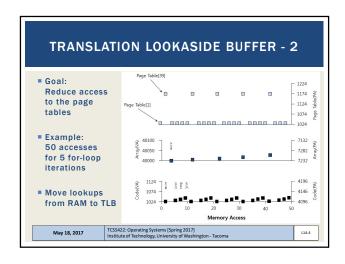

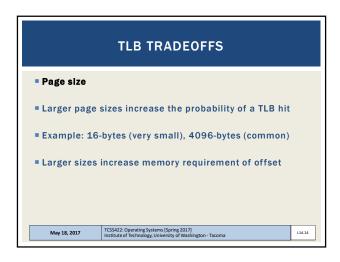

TLB TRADEOFFS - 2

Spatial locality

Accessing addresses local to each other improves the hit rate.

Consider random vs. sequential array access

What happens when the data size exceeds the TLB size?

E.g. 1st level TLB caches 64 4KB page addresses

Single program can cache data lookups for 256 KB

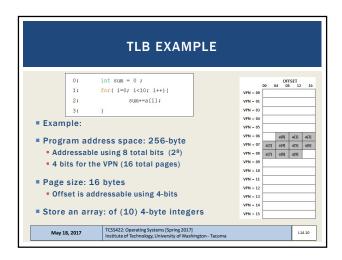

EXAMPLE: LARGE ARRAY ACCESS

Example: Consider an array of a custom struct where each struct is 64-bytes. Consider sequential access for an array of 8,192 elements stored contiguously in memory:

64 structs per 4KB page

128 total pages

TLB caches stores a maximum of 64 - 4KB page lookups

How many hits vs. misses for sequential array iteration?

1 miss for every 64 array accesses, 63 hits

Complete traversal: 128 total misses, 8,064 hits (98.4% hit ratio)