# FEEDBACK - 2

- Which (free space) memory allocation strategy does **Ubuntu use?**

- Overview from:

- https://en.wikibooks.org/wiki/The\_Linux\_Kernel/Memory

- https://zgqallen.github.io/2017/08/03/linux-glic-mmoverview/

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.3

**OVERVIEW OF VM SYSTEM IN LINUX** Brk()/mmap() TCSS422: Operating Systems [Fall 2018] November 26, 2018 L16.4 School of Engineering and Technology, University of Washington - Tacoma

#### **COMPONENTS**

- Memory Management Unit (MMU) HW module on CPU, integrates "TLB", supports virtual memory address translation

- Buddy Allocator Algorithm to allocate/reclaim page frames from physical memory

- Provides memory pages to consumers such as OS slab allocators (obj caches), kmalloc

- Page frames managed in a group for buddy allocation in sizes of 2<sup>n</sup> where (size=1,2,4,8,16,32,64,128,256,512,1024...)

- Memory Zones: DMA/DMA32 (Direct Memory Access) for device I/O, NORMAL, and HIGHMEM (32-bit machines)

- See /proc/zoneinfo

- Slab Allocator allocates OS object caches OS structs less than 4kb – provides efficient memory mgmt. for frequently used OS structs

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

L16.5

#### **COMPONENTS - 2**

- Kswapd kernel swap daemon maintains memory swap space in response to memory demands exceeding physical memory capacity

- Pages can be swapped to disk to reclaim physical memory

- Page frames carry state info to track what to do w/ a page

- FREE: available

- ACTIVE: can't swap

- INACTIVE DIRTY: no longer used, but modified page

- INACTIVE LAUNDERED: modified page, currently updating to disk

- INACTIVE CLEAN: no longer being used, can be swapped out

- Bdflush legacy, simple kernel daemon (pdflush thread) to ensure that dirty pages were periodically written to the underlying storage device - now a separate thread is maintained per device

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

## PAGING TO DISK?

- Looking for free space?

- What is a likely order of preferred states for selecting a page frame?

- Page frame state

- FREE: available

- ACTIVE: can't swap

- INACTIVE DIRTY: no longer used, but modified page

- INACTIVE LAUNDERED: modified page, currently updating to disk

- INACTIVE CLEAN: no longer being used, can be swapped out

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

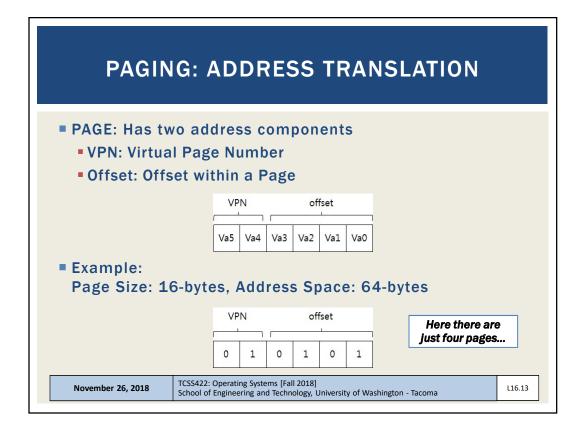

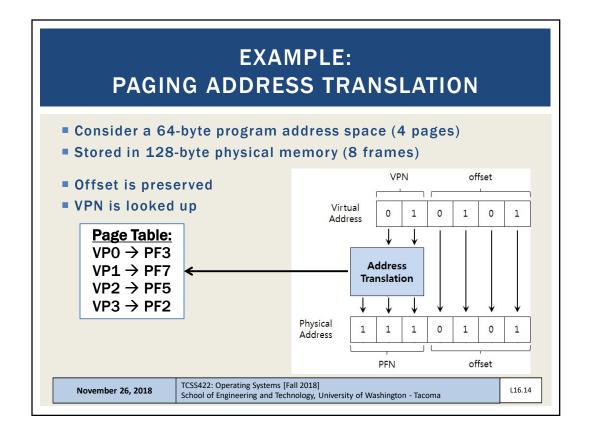

## PAGE TRANSLATION EXAMPLE

- Can you go over an example of the page table (address) translation?

- REVIEW Chapter 18...

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

L16.8

#### **PAGING**

- Split up address space of process into <u>fixed sized pieces</u> called pages

- Alternative to <u>variable sized pieces</u> (Segmentation) which suffers from significant fragmentation

- Physical memory is split up into an array of fixed-size slots called page frames.

- Each process has a page table which translates virtual addresses to physical addresses

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

L16.11

## **ADVANTAGES OF PAGING**

- Flexibility

- Abstracts the process address space into pages

- No need to track direction of HEAP / STACK growth

- Just add more pages...

- No need to store unused space

- As with segments...

- Simplicity

- Pages and page frames are the same size

- Easy to allocate and keep a free list of pages

November 26, 2018 TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

Page Table: **PAGING: EXAMPLE**  $VP0 \rightarrow PF3$  $VP1 \rightarrow PF7$ VP2 → PF5 VP3 → PF2 Consider a 128 byte address space with 16-byte pages page frame 0 of reserved for OS physical memory 16 Consider a 64-byte program (unused) page frame 1 address space page frame 2 page 3 of AS page frame 3 page 0 of AS 64 0 (page 0 of page frame 4 (unused) the address space) 16 80 page 2 of AS page frame 5 (page 1) 32 96 (page 2) (unused) page frame 6 48 112 (page 3) page 1 of AS page frame 7 128 A Simple 64-byte Address Space 64-Byte Address Space Placed In Physical Memory TCSS422: Operating Systems [Fall 2018] November 26, 2018 L16.12 School of Engineering and Technology, University of Washington - Tacoma

#### PAGE TRANSLATION EXAMPLE

- Can you go over an example of the page table (address) translation?

- Example:

- Consider a 64kb computer with 256-byte pages

- Consider a simple hello world program

- Program has only 4 memory pages

- 1 code page, 1 stack page, 1 heap page, 1 data segment page

- (1) How many 256-byte memory pages can the computer hold?

- (VPN) The operating system provides each user program a 64kb virtual address space.

- (2) How many VPN bits are required to index any virtual page?

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

L16.15

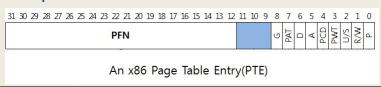

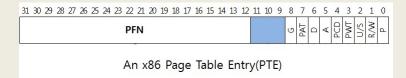

#### **EXAMPLE - 2**

- (3) To reference any individual byte on a 256-byte page, how many bits are required (OFFSET bits)?

- A single-level page table provides a one-dimensional array to look up the physical frame number of each virtual memory page

- Each page table entry (PTE) is like a record. It contains the Physical Frame Number (PFN) and status bits for the page

- PTE example with 20-bit PTE:

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

## **EXAMPLE - 3**

- Now consider our Page Table Entry (PTE) for our 64kb computer

- (4) How bits are required for the PFN?

- (5) Assuming there are 8 status bits, what is the PTE size in bits? Bytes?

- (6) What is the storage requirement for a 1-level page table?

- (7) Using 1-level page tables to index memory, how many process would fill main memory with page tables!!??

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

#### **OBJECTIVES**

- Quiz 4

- Quiz 5

- Program 3

- Paging

- Chapter 18 Introduction to Paging (finish...)

- Chapter 19 Translation Lookaside Buffer

- Chapter 20 Paging Smaller Tables

- Chapter 21/22 Beyond Physical Memory

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

L16.18

# PAGING DESIGN QUESTIONS

- (1) Where are page tables stored?

- (2) What are the typical contents of the page table?

- (3) How big are page tables?

- (4) Does paging make the system too slow?

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

# (1) WHERE ARE PAGE TABLES STORED?

- **Example:**

- Consider a 32-bit process address space (up to 4GB)

- With 4 KB pages

- 20 bits for VPN (2<sup>20</sup> pages)

- 12 bits for the page offset (2<sup>12</sup> unique bytes in a page)

- Page tables for each process are stored in RAM

- Support potential storage of 2<sup>20</sup> translations

- = 1,048,576 pages per process

- Each page has a page table entry size of 4 bytes

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.21

#### PAGE TABLE EXAMPLE

- With 2<sup>20</sup> slots in our page table for a single process

- Each slot dereferences a VPN

- Provides physical frame number

- Each slot requires 4 bytes (32 bits)

- 20 for the PFN on a 4GB system with 4KB pages

- 12 for the offset which is preserved

- (note we have no status bits, so this is unrealistically small)

VPN<sub>o</sub> VPN<sub>1</sub> VPN<sub>2</sub> VPN<sub>1048576</sub>

How much memory to store page table for 1 process?

4.194.304 bytes (or 4MB) to index one process

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

#### NOW FOR AN ENTIRE OS

- If 4 MB is required to store one process

- Consider how much memory is required for an entire OS?

- With for example 100 processes...

- Page table memory requirement is now 4MB x 100 = 400MB

- If computer has 4GB memory (maximum for 32-bits), the page table consumes 10% of memory

400 MB / 4000 GB

Is this efficient?

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.23

# (2) WHAT'S ACTUALLY IN THE PAGE TABLE

- Page table is data structure used to map virtual page numbers (VPN) to the physical address (Physical Frame Number PFN)

- Linear page table → simple array

- Page-table entry

- 32 bits for capturing state

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

# PAGE TABLE ENTRY - 2

- Common flags:

- Valid Bit: Indicating whether the particular translation is valid.

- Protection Bit: Indicating whether the page could be read from, written to, or executed from

- Present Bit: Indicating whether this page is in physical memory or on disk(swapped out)

- Dirty Bit: Indicating whether the page has been modified since it was brought into memory

- Reference Bit(Accessed Bit): Indicating that a page has been accessed

November 26, 2018 TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

# (3) HOW BIG ARE PAGE TABLES?

- Page tables are too big to store on the CPU

- Page tables are stored using physical memory

- Paging supports efficiently storing a sparsely populated address space

- Reduced memory requirement Compared to base and bounds, and segments

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.27

# (4) DOES PAGING MAKE THE SYSTEM TOO SLOW?

- Translation

- **Issue #1:** Starting location of the page table is needed

- HW Support: Page-table base register

- stores active process

- Facilitates translation

Page Table:

$VP0 \rightarrow PF3$

$VP1 \rightarrow PF7$

VP2 → PF5 VP3 → PF2

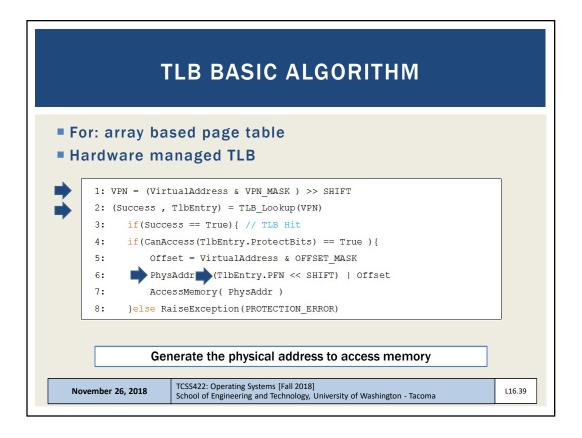

- Issue #2: Each memory address translation for paging requires an extra memory reference

- HW Support: TLBs (Chapter 19)

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

Stored in RAM →

```

PAGING MEMORY ACCESS

// Extract the VPN from the virtual address

2.

VPN = (VirtualAddress & VPN_MASK) >> SHIFT

3.

4.

// Form the address of the page-table entry (PTE)

5.

PTEAddr = PTBR + (VPN * sizeof(PTE))

// Fetch the PTE

PTE = AccessMemory(PTEAddr)

// Check if process can access the page

10.

if (PTE.Valid == False)

11.

RaiseException(SEGMENTATION_FAULT)

13.

else if (CanAccess(PTE.ProtectBits) == False)

14.

RaiseException(PROTECTION_FAULT)

15.

else

16.

// Access is OK: form physical address and fetch it

offset = VirtualAddress & OFFSET_MASK

17.

18.

PhysAddr = (PTE.PFN << PFN_SHIFT) | offset

19.

Register = AccessMemory(PhysAddr)

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

November 26, 2018

L16.29

```

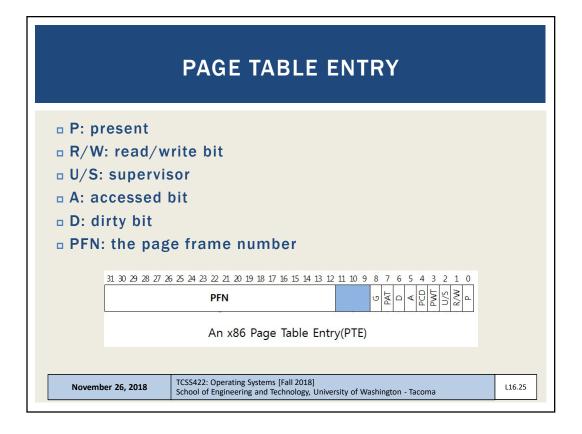

# **COUNTING MEMORY ACCESSES**

Example: Use this Array initialization Code

```

int array[1000];

for (i = 0; i < 1000; i++)

array[i] = 0;

```

Assembly equivalent:

```

0x1024 mov1 $0x0, (%edi, %eax, 4)

0x1028 incl %eax

0x102c cmpl $0x03e8, %eax

0x1030 jne 0x1024

```

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

#### PAGING SYSTEM EXAMPLE

- Consider a 4GB Computer:

- With a 4096-byte page size (4KB)

- How many pages would fit in physical memory?

- Now consider a page table:

- For the page table entry, how many bits are required for the VPN?

- If we assume the use of 4-byte (32 bit) page table entries, how many bits are available for status bits?

School of Engineering and Technology, University of Washington - Tacoma

- How much space does this page table require?

Page Table Entries x Number of pages

- How many page tables (for user processes) would fill the entire 4GB of memory?

would fill the entire 4GB of memory?

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

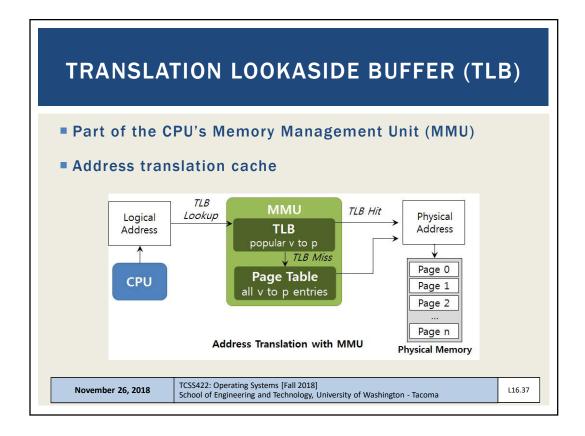

#### TRANSLATION LOOKASIDE BUFFER

- Legacy name...

- Better name, "Address Translation Cache"

- TLB is an on CPU cache of address translations

- ■virtual → physical memory

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.35

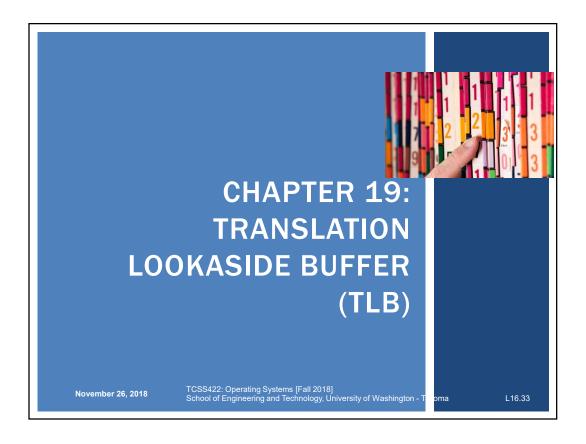

#### TRANSLATION LOOKASIDE BUFFER - 2 Page Table[39] ■ Goal: **Reduce access** 1174 to the page Page Table[1] 1124 tables 0-0000-0000-0000-000 Example: 50 RAM accesses 40100 7132 for first 5 for-loop 40050 7282 iterations 40000 7232 Move lookups 4196 1124 from RAM to TLB 1074 4146 by caching page 1024 table entries 50 **Memory Access** TCSS422: Operating Systems [Fall 2018] November 26, 2018 L16.36 School of Engineering and Technology, University of Washington - Tacoma

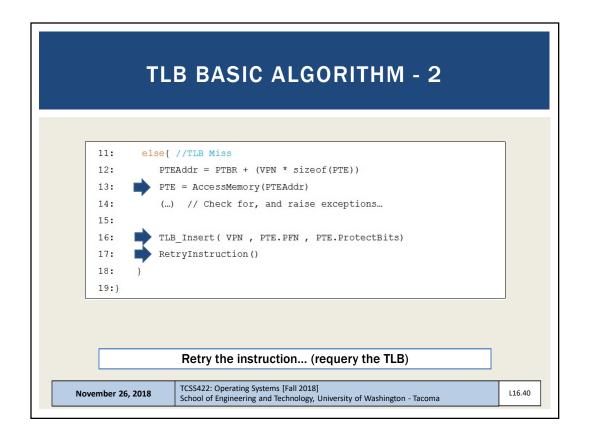

## TLB - ADDRESS TRANSLATION CACHE

- Key detail:

- For a TLB miss, we first access the page table in RAM to populate the TLB... we then requery the TLB

- All address translations go through the TLB

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

VPN = 00

VPN = 01VPN = 03**VPN** = 04

VPN = 07

VPN = 08

VPN = 09

**VPN** = 12

**VPN = 13 VPN** = 14

**VPN** = 15

a[8]

L16.41

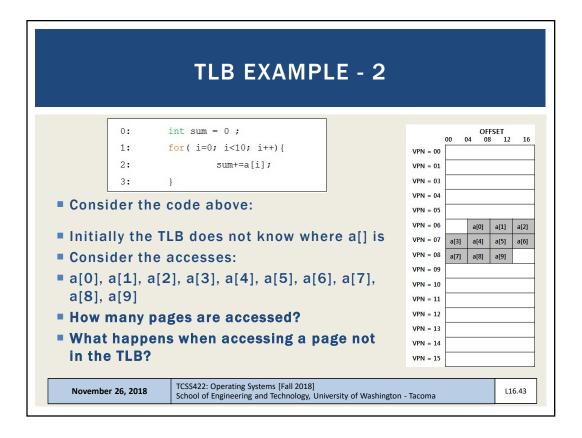

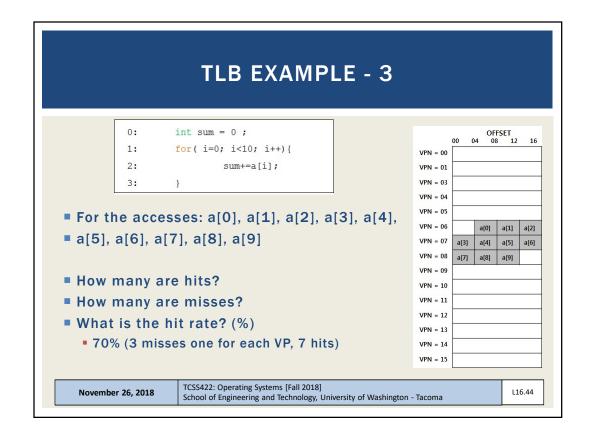

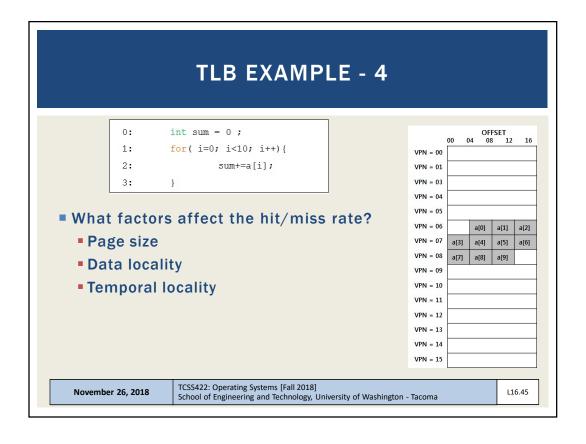

#### **TLB EXAMPLE**

int sum = 0; for( i=0; i<10; i++){</pre> 1: sum+=a[i];

- **Example:**

- Program address space: 256-byte

- Addressable using 8 total bits (28)

- 4 bits for the VPN (16 total pages)

- Page size: 16 bytes

- Offset is addressable using 4-bits

- Store an array: of (10) 4-byte integers

TCSS422: Operating Systems [Fall 2018] November 26, 2018

L16.42 School of Engineering and Technology, University of Washington - Tacoma

## **OBJECTIVES**

- Chapter 20

- Smaller tables

- Hybrid tables

- Multi-level page tables

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.47

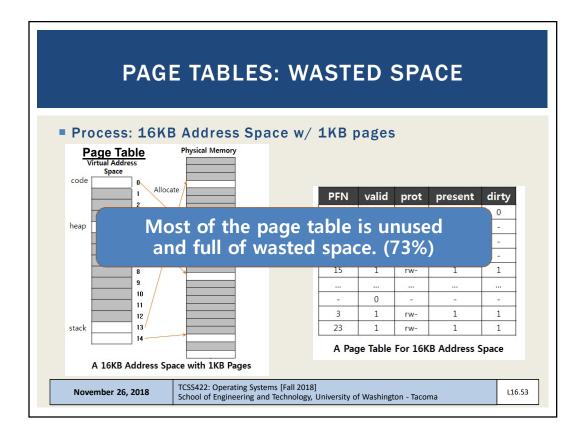

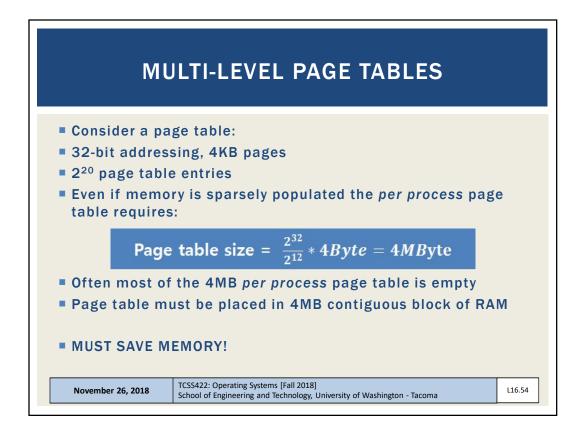

#### LINEAR PAGE TABLES

- Consider array-based page tables:

- Each process has its own page table

- 32-bit process address space (up to 4GB)

- With 4 KB pages

- 20 bits for VPN

- 12 bits for the page offset

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

#### **LINEAR PAGE TABLES - 2**

- Page tables stored in RAM

- Support potential storage of 2<sup>20</sup> translations

- = 1,048,576 pages per process @ 4 bytes/page

- Page table size 4MB / process

Page table size =

$$\frac{2^{32}}{2^{12}} * 4Byte = 4MByte$$

- Consider 100+ OS processes

- Requires 400+ MB of RAM to store process information

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

L16.49

#### **LINEAR PAGE TABLES - 2**

- Page tables stored in RAM

- Support potential storage of 2<sup>20</sup> translations

- = 1,048,576 pages per process @ 4 bytes/page

- Page table size 4MB / process

Page tables are too big and consume too much memory.

**Need Solutions ...**

- Consider 100+ OS processes

- Requires 400+ MB of RAM to store process information

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

#### **PAGING: USE LARGER PAGES**

- <u>Larger pages</u> = 16KB = 2<sup>14</sup>

- 32-bit address space: 2<sup>32</sup>

- $2^{18} = 262,144$  pages

$$\frac{2^{32}}{2^{14}} * 4 = 1MB$$

per page table

- Memory requirement cut to 1/4

- However pages are huge

- Internal fragmentation results

- 16KB page(s) allocated for small programs with only a few variables

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.51

PAGE TABLES: WASTED SPACE Process: 16KB Address Space w/ 1KB pages Page Table Allocate PFN valid prot present dirty 10 0 1 heap 0 0 6 0 15 rw-1 10 11 1 rw-12 13 rw-A Page Table For 16KB Address Space A 16KB Address Space with 1KB Pages TCSS422: Operating Systems [Fall 2018] November 26, 2018 L16.52 School of Engineering and Technology, University of Washington - Tacoma

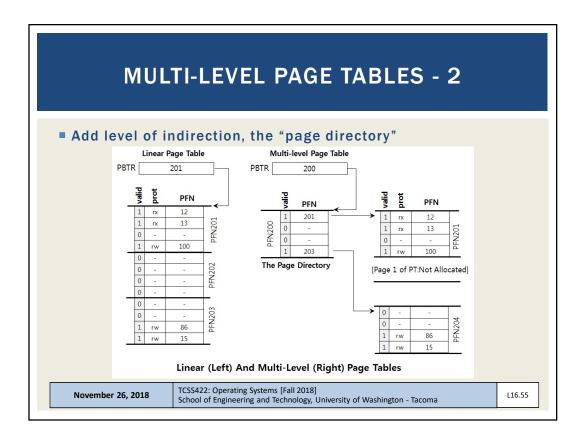

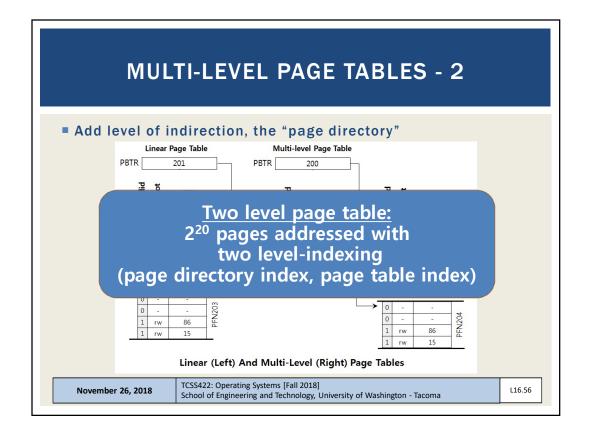

#### **MULTI-LEVEL PAGE TABLES - 3**

- Advantages

- Only allocates page table space in proportion to the address space actually used

- Can easily grab next free page to expand page table

- Disadvantages

- Multi-level page tables are an example of a time-space tradeoff

- Sacrifice address translation time (now 2-level) for space

- Complexity: multi-level schemes are more complex

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.57

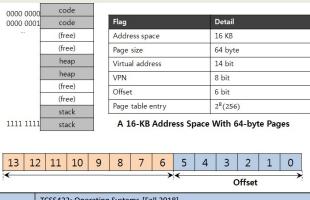

#### **EXAMPLE**

- 16KB address space, 64byte pages

- How large would a one-level page table need to be?

- $2^{14}$  (address space) /  $2^{6}$  (page size) =  $2^{8}$  = 256 (pages)

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

#### **EXAMPLE - 2**

- 256 total page table entries (64 bytes each)

- 1,024 bytes page table size, stored using 64-byte pages = (1024/64) = 16 page directory entries (PDEs)

- Each page directory entry (PDE) can hold 16 page table entries (PTEs) e.g. lookups

- 16 page directory entries (PDE) x 16 page table entries (PTE) = 256 total PTEs

- Key idea: the page table is stored using pages too!

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.59

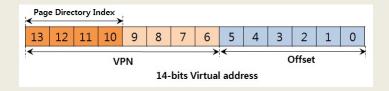

#### PAGE DIRECTORY INDEX

- Now, let's split the page table into two:

- 8 bit VPN to map 256 pages

- 4 bits for page directory index (PDI 1st level page table)

- 6 bits offset into 64-byte page

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

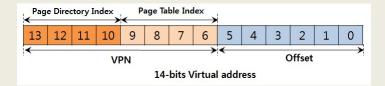

#### **PAGE TABLE INDEX**

- 4 bits page directory index (PDI 1st level)

- 4 bits page table index (PTI 2<sup>nd</sup> level)

- To dereference one 64-byte memory page,

- We need one page directory entry (PDE)

- One page table Index (PTI) can address 16 pages

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.61

#### **EXAMPLE - 3**

- For this example, how much space is required to store as a single-level page table with any number of PTEs?

- 16KB address space, 64 byte pages

- 256 page frames, 4 byte page size

- 1,024 bytes required (single level)

- How much space is required for a two-level page table with only 4 page table entries (PTEs)?

- Page directory = 16 entries x 4 bytes (1 x 64 byte page)

- Page table = 4 entries x 4 bytes (1 x 64 byte page)

- 128 bytes required (2 x 64 byte pages)

- Savings = using just 12.5% the space !!!

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

#### 32-BIT EXAMPLE

- Consider: 32-bit address space, 4KB pages, 2<sup>20</sup> pages

- Only 4 mapped pages

- **Single level**: 4 MB (we've done this before)

- Two level: (old VPN was 20 bits, split in half)

- Page directory = 2<sup>10</sup> entries x 4 bytes = 1 x 4 KB page

- Page table = 4 entries x 4 bytes (mapped to 1 4KB page)

- 8KB (8,192 bytes) required

- Savings = using just .78 % the space !!!

- 100 sparse processes now require < 1MB for page tables

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.63

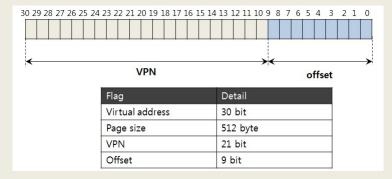

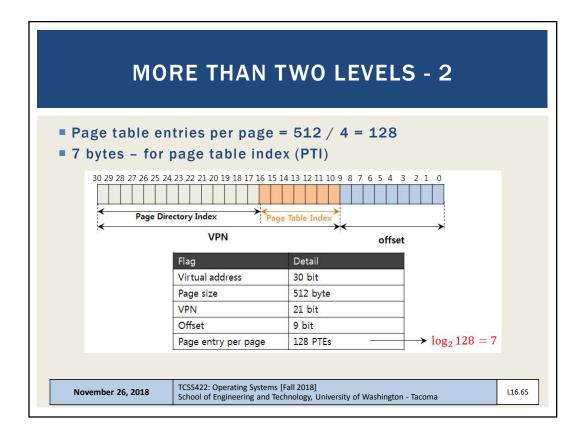

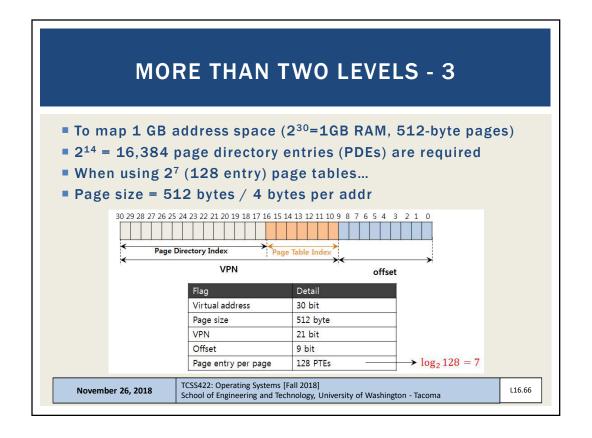

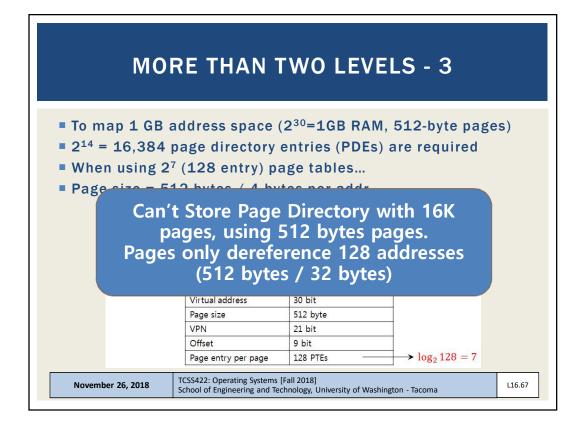

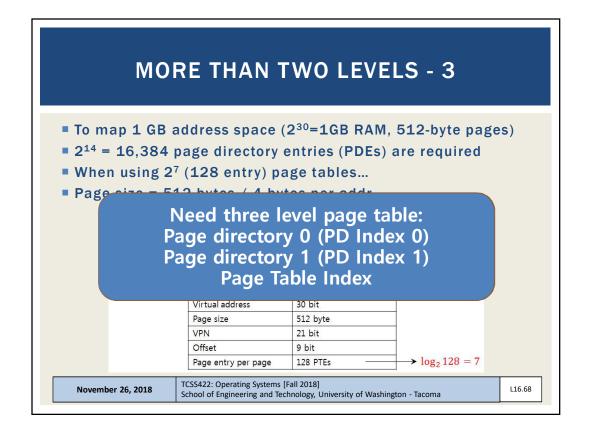

#### MORE THAN TWO LEVELS

- Consider: page size is 29 = 512 bytes

- Page size 512 bytes / Page entry size 4 bytes

- VPN is 21 bits

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

#### **MORE THAN TWO LEVELS - 4**

- We can now address 1GB with "fine grained" 512 byte pages

- Using multiple levels of indirection

- Consider the implications for address translation!

- How much space is required for a virtual address space with 4 entries on a 512-byte page? (let's say 4 32-bit integers)

- PD0 1 page, PD1 1 page, PT 1 page = 1,536 bytes

- Savings = 1,536 / 8,388,608 (8mb) = .0183% !!!

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.69

# **ADDRESS TRANSLATION CODE**

```

// 5-level Linux page table address lookup

//

// Inputs:

// mm_struct - process's memory map struct

// vpage - virtual page address

// Define page struct pointers

pgd_t *pgd;

p4d_t *p4d;

pud_t *pud;

pmd_t *pud;

pmd_t *pmt;

pte_t *pte;

struct page *page;

November 26, 2018 | TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma | 116.70

```

#### **ADDRESS TRANSLATION - 2**

pgd = pgd\_offset(mm, vpage); if (pgd none (\*pgd) || pgd bad (\*pgd)) | for the process, returns the PGD entry that return 0; p4d = p4d offset(pgd, vpage); if (p4d\_none(\*p4d) || p4d\_bad(\*p4d)) return 0: pud = pud offset(p4d, vpage); if (pud\_none(\*pud) || pud\_bad(\*pud)) return 0; pmd = pmd\_offset(pud, vpage); if (pmd\_none(\*pmd) || pmd\_bad(\*pmd)) return 0; if (!(pte = pte\_offset\_map(pmd, vpage))) return 0; if (!(page = pte\_page(\*pte))) return 0; physical page addr = page to phys(page) pte\_unmap(pte);

#### pgd\_offset():

Takes a vpage address and the mm\_struct covers the requested address...

#### p4d/pud/pmd\_offset():

Takes a vpage address and the pgd/p4d/pud entry and returns the relevant p4d/pud/pmd.

#### pte\_unmap()

release temporary kernel mapping for the page table entry

return physical\_page\_addr; // param to send back

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

L16.71

#### **INVERTED PAGE TABLES**

- Keep a single page table for each physical page of memory

- Consider 4GB physical memory

- Using 4KB pages, page table requires 4MB to map all of RAM

- Page table stores

- Which process uses each page

- Which process virtual page (from process virtual address space) maps to the physical page

- All processes share the same page table for memory mapping, kernel must isolate all use of the shared structure

- Finding process memory pages requires search of 2<sup>20</sup> pages

- Hash table: can index memory and speed lookups

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

### **MULTI-LEVEL PAGE TABLE EXAMPLE**

- Consider a 16 MB computer which indexes memory using 4KB pages

- (#1) For a single level page table, how many pages are required to index memory?

- (#2) How many bits are required for the VPN?

- (#3) Assuming each page table entry (PTE) can index any byte on a 4KB page, how many offset bits are required?

- (#4) Assuming there are 8 status bits, how many bytes are required for each page table entry?

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.73

### **MULTI LEVEL PAGE TABLE EXAMPLE - 2**

- (#5) How many bytes (or KB) are required for a single level page table?

- Let's assume a simple HelloWorld.c program.

- HelloWorld.c requires virtual address translation for 4 pages:

- 1 code page

- 1 stack page

- 1 heap page

- 1 data segment page

- (#6) Assuming a two-level page table scheme, how many bits are required for the Page Directory Index (PDI)?

- (#7) How many bits are required for the Page Table Index (PTI)?

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

### **MULTI LEVEL PAGE TABLE EXAMPLE - 3**

- Assume each page directory entry (PDE) and page table entry (PTE) requires 4 bytes:

- 6 bits for the Page Directory Index (PDI)

- 6 bits for the Page Table Index (PTI)

- 12 offset bits

- 8 status bits

- (#8) How much total memory is required to index the HelloWorld.c program using a two-level page table when we only need to translate 4 total pages?

- HINT: we need to allocate one Page Directory and one Page Table...

- HINT: how many entries are in the PD and PT

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.75

### **MULTI LEVEL PAGE TABLE EXAMPLE - 4**

- (#9) Using a single page directory entry (PDE) pointing to a single page table (PT), if all of the slots of the page table (PT) are in use, what is the total amount of memory a two-level page table scheme can address?

- **(#10)** And finally, for this example, as a percentage (%), how much memory does the 2-level page table scheme consume compared to the 1-level scheme?

- HINT: two-level memory use / one-level memory use

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

### **ANSWERS**

- **#1** 4096 pages

- #2 12 bits

- #3 12 bits

- #4 4 bytes

- **#**5 4096 x 4 = 16,384 bytes (16KB)

- #6 6 bits

- #7 6 bits

- #8 256 bytes for Page Directory (PD) (64 entries x 4 bytes)

256 bytes for Page Table (PT) TOTAL = 512 bytes

- #9 64 entries, where each entry maps a 4,096 byte page With 12 offset bits, can address 262,144 bytes (256 KB)

- #10-512/16384 = .03125  $\rightarrow$  3.125%

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

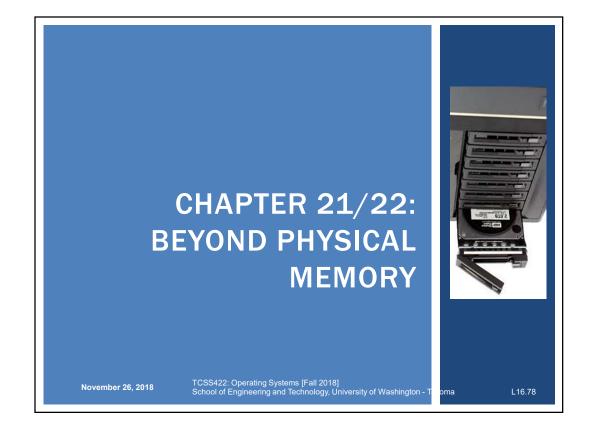

# **MEMORY HIERARCHY**

Disks (HDD, SSD) provide another level of storage in the memory hierarchy

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

# **MOTIVATION FOR EXPANDING THE ADDRESS SPACE**

- Can provide illusion of an address space larger than physical RAM

- For a single process

- Convenience

- Ease of use

- For multiple processes

- Large virtual memory space for many concurrent processes

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

L16.80

### **LATENCY TIMES**

- Design considerations

- SSDs 4x the time of DRAM

- HDDs 80x the time of DRAM

| Action                             | Latency (ns)  | (µs)      |                              |

|------------------------------------|---------------|-----------|------------------------------|

| L1 cache reference                 | 0.5ns         |           |                              |

| L2 cache reference                 | 7 ns          |           | 14x L1 cache                 |

| Mutex lock/unlock                  | 25 ns         |           |                              |

| Main memory reference              | 100 ns        |           | 20x L2 cache, 200x L1        |

| Read 4K randomly from SSD*         | 150,000 ns    | 150 μs    | ~1GB/sec SSD                 |

| Read 1 MB sequentially from memory | 250,000 ns    | 250 μs    |                              |

| Read 1 MB sequentially from SSD*   | 1,000,000 ns  | 1,000 µs  | 1 ms ~1GB/sec SSD, 4X memory |

| Read 1 MB sequentially from disk   | 20,000,000 ns | 20,000 μs | 20 ms 80x memory, 20X SSD    |

- Latency numbers every programmer should know

- From: https://gist.github.com/jboner/2841832#file-latency-txt

November 26, 2018 TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

### **SWAP SPACE** Disk space for storing memory pages "Swap" them in and out of memory to disk as needed PFN 0 PFN 1 PFN 2 PFN 3 **Physical** Proc 0 [VPN 0] Proc 1 [VPN 2] Proc 1 [VPN 3] Proc 2 [VPN 0] Memory Block 1 Block 2 Block 3 Block 4 Block 5 Block 6 Block 7 Block 0 Swap Proc 0 Proc 0 [VPN 2] Proc 1 Proc 1 Proc 3 Proc 3 [VPN 1] [VPN 0] [VPN 1] [VPN 0] [VPN 1] [VPN 1] **Physical Memory and Swap Space** TCSS422: Operating Systems [Fall 2018] November 26, 2018 L16.82

School of Engineering and Technology, University of Washington - Tacoma

### **PAGE LOCATION**

- Page table pages are:

- Stored in memory

- Swapped to disk

- Present bit

- In the page table entry (PTE) indicates if page is present

- Page fault

- Memory page is accessed, but has been swapped to disk

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.83

L16.84

### **PAGE FAULT**

- OS steps in to handle the page fault

- Loading page from disk requires a free memory page

- Page-Fault Algorithm

```

PFN = FindFreePhysicalPage()

if (PFN == -1)

// no free page found

PFN = EvictPage()

// run replacement algorithm

4:

DiskRead (PTE.DiskAddr, pfn)

// sleep (waiting for I/O)

5:

PTE.present = True

// set PTE bit to present

6:

PTE.PFN = PFN

// reference new loaded page

RetryInstruction()

// retry instruction

```

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

# PAGE REPLACEMENTS

- Page daemon

- Background threads which monitors swapped pages

- Low watermark (LW)

- Threshold for when to swap pages to disk

- Daemon checks: free pages < LW</p>

- Begin swapping to disk until reaching the highwater mark

- High watermark (HW)

- Target threshold of free memory pages

- Daemon free until: free pages >= HW

November 26, 2018

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

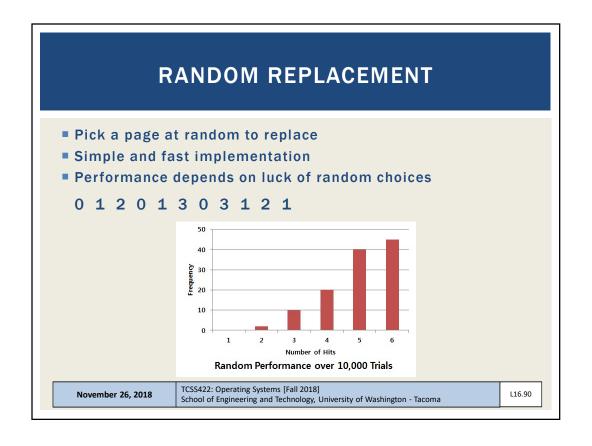

**REPLACEMENT POLICIES** CHANGES TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington -

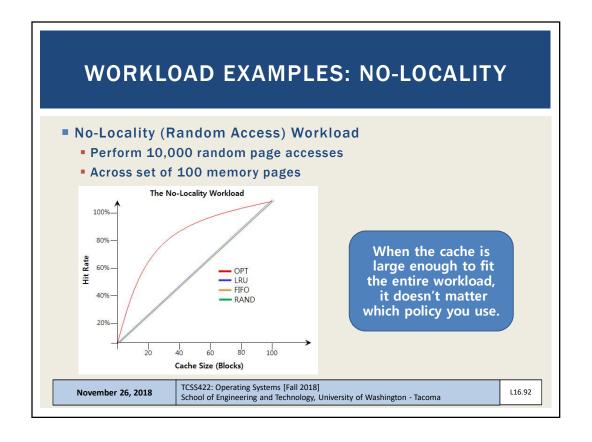

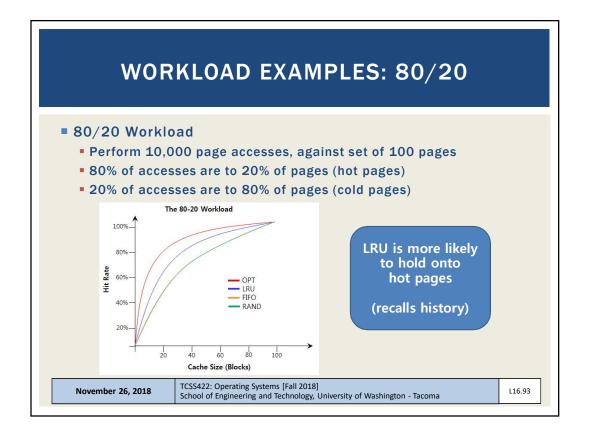

### **CACHE MANAGEMENT**

- Replacement policies apply to "any" cache

- Goal is to minimize the number of misses

- Average memory access time can be estimated:

$$AMAT = (P_{Hit} * T_M) + (P_{Miss} * T_D)$$

| Argument   | Meaning                                                      |

|------------|--------------------------------------------------------------|

| $T_{M}$    | The cost of accessing memory (time)                          |

| $T_D$      | The cost of accessing disk (time)                            |

| $P_{Hit}$  | The probability of finding the data item in the cache(a hit) |

| $P_{Miss}$ | The probability of not finding the data in the cache(a miss) |

- Consider  $T_M = 100 \text{ ns}, T_D = 10 \text{ms}$

- Consider P<sub>hit</sub> = .9 (90%), P<sub>miss</sub> = .1

- Consider P<sub>hit</sub> = .999 (99.9%), P<sub>miss</sub> = .001

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

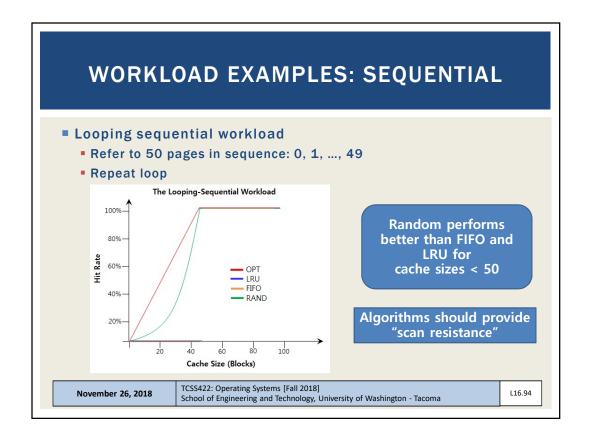

### **OPTIMAL REPLACEMENT POLICY**

- What if:

- We could predict the future (... with a magical oracle)

- All future page accesses are known

- Always replace the page in the cache used farthest in the future

- Used for a comparison

- Provides a "best case" replacement policy

- Consider a 3-element empty cache with the following page accesses:

0 1 2 0 1 3 0 3 1 2 1

What is the hit/miss ratio?

6 hits

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.88

# FIFO REPLACEMENT Queue based Always replace the oldest element at the back of cache Simple to implement Doesn't consider importance... just arrival ordering Consider a 3-element empty cache with the following page accesses: 0 1 2 0 1 3 0 3 1 2 1 What is the hit/miss ratio? How is FIFO different than LRU? A hits RUIncorporates history

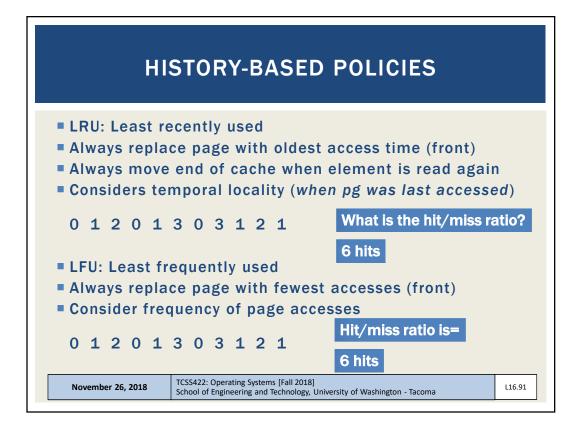

### **IMPLEMENTING LRU**

- Implementing last recently used (LRU) requires tracking access time for all system memory pages

- Times can be tracked with a list

- For cache eviction, we must scan an entire list

- Consider: 4GB memory system (2<sup>32</sup>), with 4KB pages (212)

- This requires 2<sup>20</sup> comparisons !!!

- Simplification is needed

- Consider how to approximate the oldest page access

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.95

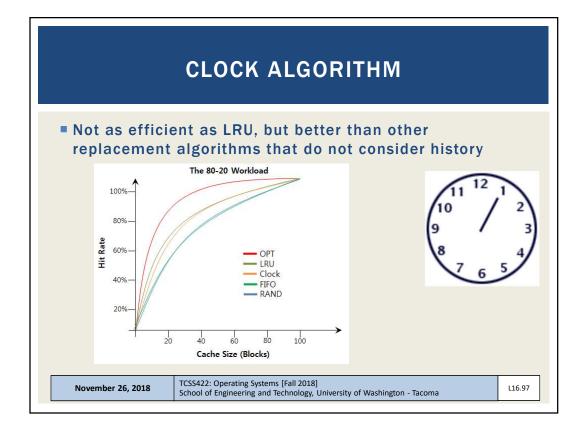

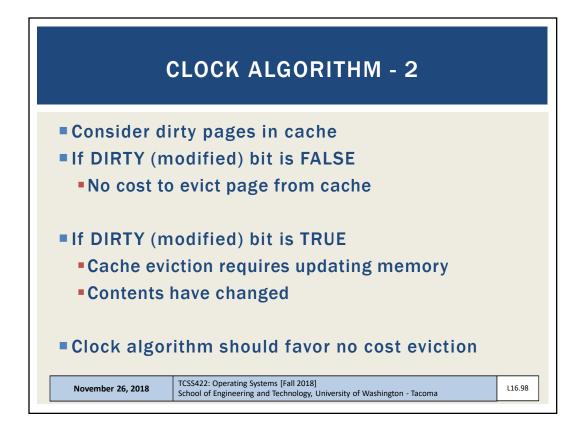

### **IMPLEMENTING LRU - 2**

- Harness the Page Table Entry (PTE) Use Bit

- HW sets to 1 when page is used

- OS sets to 0

- Clock algorithm (approximate LRU)

- Refer to pages in a circular list

- Clock hand points to current page

- Loops around

- IF USE\_BIT=1 set to USE\_BIT = 0

- IF USE\_BIT=0 replace page

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

### WHEN TO LOAD PAGES

- On demand → demand paging

- Prefetching

- Preload pages based on anticipated demand

- Prediction based on locality

- Access page P, suggest page P+1 may be used

- What other techniques might help anticipate required memory pages?

- Prediction models, historical analysis

- In general: accuracy vs. effort tradeoff

- High analysis techniques struggle to respond in real time

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma

L16.99

## OTHER SWAPPING POLICIES

- Page swaps / writes

- Group/cluster pages together

- Collect pending writes, perform as batch

- Grouping disk writes helps amortize latency costs

- Thrashing

- Occurs when system runs many memory intensive processes and is low in memory

- Everything is constantly swapped to-and-from disk

November 26, 2018

TCSS422: Operating Systems [Fall 2018]

School of Engineering and Technology, University of Washington - Tacoma

# OTHER SWAPPING POLICIES - 2

- Working sets

- Groups of related processes

- When thrashing: prevent one or more working set(s) from running

- Temporarily reduces memory burden

- •Allows some processes to run, reduces thrashing

November 26, 2018

TCSS422: Operating Systems [Fall 2018] School of Engineering and Technology, University of Washington - Tacoma