```

HISTORICAL IMPLEMENTATION

To implement mutual exclusion

Disable interrupts upon entering critical sections

| void lock() {

| DisableInterrupts(); |

| 4 void unlock() {

| 5 EnableInterrupts(); |

| 6 }

| Any thread could disable system-wide interrupt

What if lock is never released?

On a multiprocessor processor each CPU has its own interrupts

Do we disable interrupts for all cores simultaneously?

While interrupts are disabled, they could be lost

If not queued...

| TCSS422:Operating Systems [Fall 2016] |

| Institute of Technology, University of Washington - Tacoma | 17.11 |

```

```

DIY: TEST-AND-SET INSTRUCTION

C implementation

Implements atomicity for a spin lock

Try this...

I int TestAndSet (int *ptr, int new) {

int old = *ptr; // fetch old value at ptr

int old = *ptr; // store vhee* into ptr

int old = *ptr; // store vhee* into ptr

int old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr; // store vhee* into ptr

into old = *ptr;

```

```

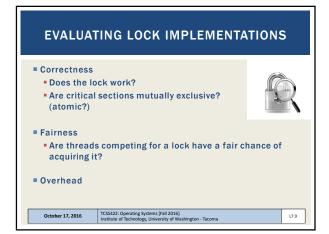

SPIN LOCK EVALUATION

Correctness:

Spin locks guarantee: critical sections won't be executed simultaneously by (2) threads

Fairness:

No fairness guarantee. Once a thread has a lock, nothing forces it to relinquish it...

Performance:

Spin locks perform "busy waiting"

Spin locks are best for short periods of waiting

Performance is slow when multiple threads share a CPU

Especially for long periods

Cotober 17, 2016

Cotober 17, 2016

TCSS422-Operating Systems [Fail 2016]

Institute of Technology, University of Washington - Tacoma

```

```

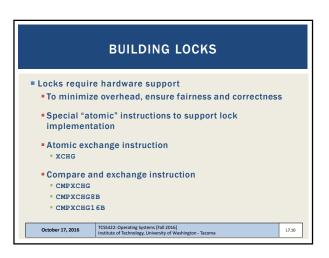

TWO MORE "LOCK BUILDING"

CPU INSTRUCTIONS

Instructions used together to support synchronization

No support on x86 processors

Supported by RISC: Alpha, PowerPC, ARM

Load-linked (LL)

Loads value into register

Same as typical load

Used as a mechanism to track competition

Store-conditional (SC)

Performs "mutually exclusive" store

Allows only one thread to store value

```

```

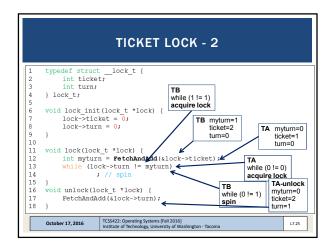

FETCH-AND-ADD

### CPU Instruction

Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Increment counter atomically in one instruction

| Incremen

```

```

HARDWARE SPIN LOCKS - SUMMARY

Simple, correct

Slow

With long locks, waiting threads spin for entire timeslice

Repeat comparison continuously

Busy waiting

How To Avoid Spinning?

Need both HW & OS Support !

```

```

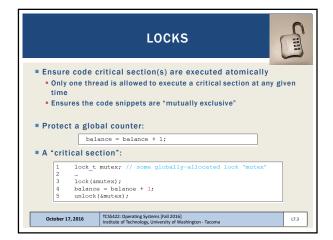

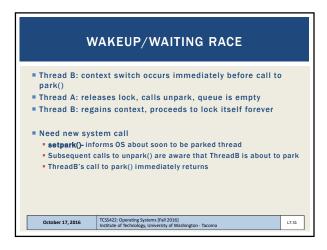

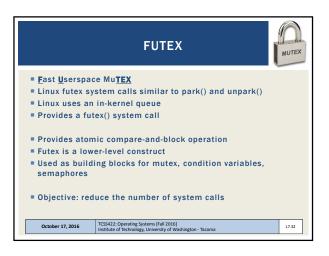

THREAD QUEUES

Don't allow the OS to control your program

Use internal Thread Queues

Allows programmer to maintain control

Ensure fairness, prevent starvation

Better for synchronizing large #'s of threads

Require OS support for adding/removing theads to/from queue(s)

Solaris

park(): puts thread to sleep

unpark(threadID): wakes specified thread

Linux: futex()

TCSS42: Operating Systems [Fall 2016] Institute of Technology, University of Washington - Tacoma

```

```

FUTEX - 2

■ futex_wait(addr, expected)

■ Put calling thread to sleep

■ If value @ addr!= expected → return immediately

■ futex_wake(addr)

■ Wake one thread that is waiting on the queue

■ These are not exposed as C library calls

■ Call futex() with FUTEX_WAIT or FUTEX_WAKE

■ Use a 32-bit integer

■ The leftmost bit (the +/- sign) tracks the lock state

■ 0 - free

■ 1 - locked

■ Remaining 31 bits: identifies thread

```

```

FUTEX - 3

Void mutex_lock(int *mutex) {

int v;

/* Bit 31 was clear, we got the mutex (this is a fast lock!)

if (atomic_bit_test_set (mutex, 31) == 0)

return;

/* "adds" mutex to queue

atomic_interement (mutex);

while /s lock available?

// is lock available?

if (atomic_bit_test_set (mutex, 31) == 0 {

// remove mutex from queue - it has the lock now

atomic_decrement (mutex);

return;

}

// Have to wait. Make sure futex value is locked (negative)

v = *mutex;

iv (v >= 0)

continue;

// wait to be woken up when lock is available

// this is not a spin lock. (signal)

futex_wait (mutex, v);

}

October 17, 2016

TCSS422-Operating Systems [Fall 2016]

instruct of Technology, University of Weshington-Tacoms

```

```

TWO PHASE LOCKS

Hybrid between spin-locks and yielding

Useful if lock is about to be released

First phase

Spin lock for some time waiting for the lock to be released

If lock is not acquired after time expires enter phase two.

Second phase

Thread sleeps (yields)

Is awoken when the lock becomes free

```