| DOES PAGING MAKE<br>THE SYSTEM TOO SLOW?                                                |                                                                                                      |                                                                   |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Translation                                                                             |                                                                                                      |                                                                   |

| Issue #1: Starting location of the page table is needed                                 |                                                                                                      |                                                                   |

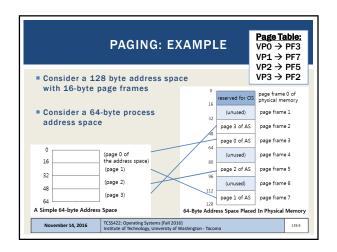

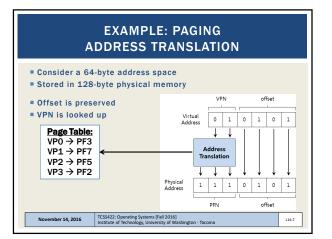

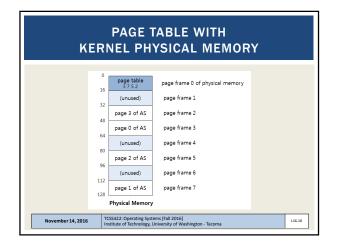

| <ul> <li>HW Support: Page-table base register</li> <li>stores active process</li> </ul> |                                                                                                      | Page Table:<br>VP0 → PF3                                          |

| ■ Facilitates translation<br>Stored in RAM →                                            |                                                                                                      | $VP1 \rightarrow PF7$ $VP2 \rightarrow PF5$ $VP3 \rightarrow PF2$ |

| Issue #2: Each memory address translation for paging requires an extra memory reference |                                                                                                      |                                                                   |

| HW Support: TLBs (Chapter 19)                                                           |                                                                                                      |                                                                   |

| November 14, 2016                                                                       | TCSS422: Operating Systems [Fall 2016]<br>Institute of Technology, University of Washington - Tacoma | L16.15                                                            |

|                                                                                                                                            | PAGING MEMORY ACCESS                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1.<br>2.<br>3.                                                                                                                             | <pre>// Extract the VPN from the virtual address VPN = (virtualaddress &amp; VPN_MASK) &gt;&gt; SHIFT</pre>              |

| 4.<br>5.<br>6.                                                                                                                             | <pre>// Form the address of the page-table entry (PTE) PTEAddr = PTBR + (VPN * sizeof(PTE))</pre>                        |

| 7.<br>8.<br>9.                                                                                                                             | // Fetch the PTE<br>PTE = AccessMemory(PTEAddr)                                                                          |

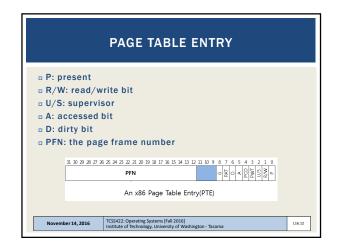

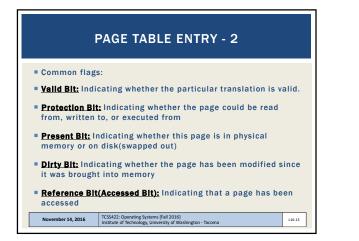

| 10.<br>11.                                                                                                                                 | <pre>// Check if process can access the page if (PTE.valid == False)</pre>                                               |

| 12.<br>13.<br>14.                                                                                                                          | RaiseException(SEGMENTATION_FAULT)<br>else if (CanAccess(PTE.ProtectBits) == False)<br>RaiseException(PROTECTION_FAULT)  |

| 15.                                                                                                                                        | else // Access is OK: form physical address and fetch it                                                                 |

| 17.<br>18.<br>19.                                                                                                                          | offset = VirtualAddress & OFFSET_MASK<br>PhysAddr = (PTE.PFN << PFN_SHIFT)   offset<br>Register = AccessHemory(PhysAddr) |

| November 14, 2016         TCSS422: Operating Systems [Fall 2016]<br>Institute of Technology, University of Washington - Tacoma         Lte |                                                                                                                          |