**COURSE EVALUATION - EXTRA CREDIT Q 11:59p, June 4th: 44% (28 of 63)** ■ 50%+ participation: All students +2 pts 'Feedback Surveys' extra credit 2% \* (total-pts / 19) = 0.32% boost ■ 70%+ participation: All students +5 pts 'Feedback Surveys' extra credit ■ 2% \* (total-pts / 19) = 0.53% boost ■ 90%+ participation: All students +8 pts 'Feedback Surveys' extra credit \* 2% \* (total-pts / 19) = 0.84% boost 100% participation: • All students +9.5 pts 'Feedback Surveys' extra credit 2% \* (total-pts / 19) = 1 % boost

June 5, 2025 TCSS422: Operating Systems [Spring School of Engineering and Technolo L19.2 rsity of Washington - Tacoma

<u>I</u>

ONLINE DAILY FEEDBACK SURVEY

Daily Feedback Quiz in Canvas – Available After Each Class

Extra credit available for completing surveys ON TIME

Tuesday surveys: due by ~ Wed @ 11:59p

Thursday surveys: due ~ Mon @ 11:59p

TCSS 422 A > Assignments

Symbol Syllabus

Announcements

Zoom

Syllabus

Assignments

TCSS 422 - Online Daily Feedback Survey - 4/1

Assistant until for 3 x 11:5/ps | Dox Ap 5 x 12/ps | 1/4 ps |

TCSS 422 - Online Daily Feedback Survey - 4/1

Assistant until for 3 x 11:5/ps | Dox Ap 5 x 12/ps | 1/4 ps |

TCSS 422 - Computer Operating Systems (Sping 2025)

School of Engineering and Technology, University of Washington - Tacoma

3

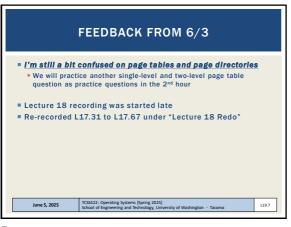

MATERIAL / PACE

■ Please classify your perspective on material covered in today's class (33 of 63 respondents - 52.4%):

■ 1-mostly review, 5-equal new/review, 10-mostly new

■ Average - 5.64 (↑- previous 5.13)

■ Please rate the pace of today's class:

■ 1-slow, 5-just right, 10-fast

■ Average - 4.91 (↓- previous 5.00)

Slides by Wes J. Lloyd

5

L19.1

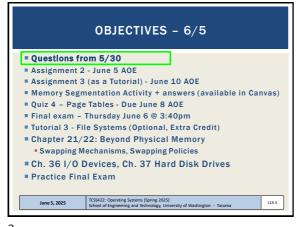

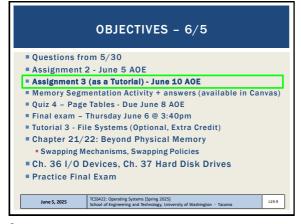

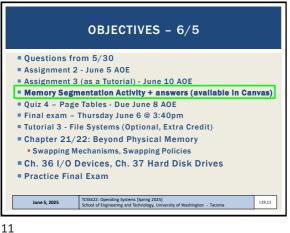

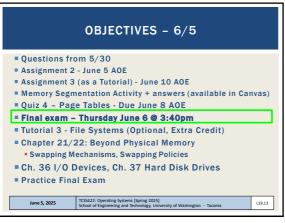

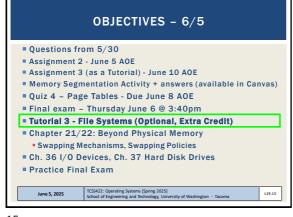

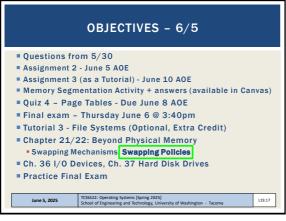

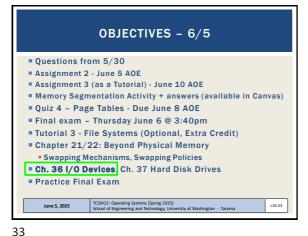

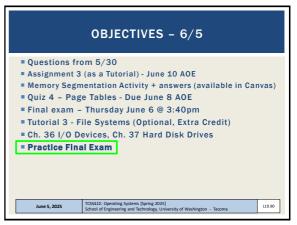

OBJECTIVES - 6/5 Questions from 5/30 = Assignment 2 - June 5 AOE Assignment 3 (as a Tutorial) - June 10 A0E Memory Segmentation Activity + answers (available in Canvas) Quiz 4 - Page Tables - Due June 8 AOE Final exam - Thursday June 6 @ 3:40pm ■ Tutorial 3 - File Systems (Optional, Extra Credit) Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies Ch. 36 I/O Devices, Ch. 37 Hard Disk Drives ■ Practice Final Exam June 5, 2025 L19.8

**ASSIGNMENT 3:** INTRODUCTION TO LINUX KERNEL MODULES Assignment 3 provides an introduction to kernel programming by demonstrating how to create a Linux Kernel Module Kernel modules are commonly used to write device drivers and can access protected operating system data structures For example: Linux task\_struct process data structure June 5, 2025 L19.10

10

9

**OBJECTIVES - 6/5** ■ Questions from 5/30 Assignment 2 - June 5 AOE Assignment 3 (as a Tutorial) - June 10 AOE Memory Segmentation Activity + answers (available in Canvas) Quiz 4 – Page Tables - Due June 8 AOE Final exam - Thursday June 6 @ 3:40pm ■ Tutorial 3 - File Systems (Optional, Extra Credit) Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies ■ Ch. 36 I/O Devices, Ch. 37 Hard Disk Drives ■ Practice Final Exam June 5, 2025 TCSS422: Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washington - Tacoma L19.12

12

Slides by Wes J. Lloyd

L19.2

FINAL EXAM - THURSDAY JUNE 12 @ 3:40PM<sup>TH</sup> Thursday June 12 from 3:40 to 5:40 pm Final (100 points) . SHORT: similar number of questions as the midterm 2-hours Focus on new content - since the midterm (~70% new, 30% before) Final Exam Review Complete Memory Segmentation Activity Complete Ouiz 4 Practice Final Exam Questions - 2<sup>nd</sup> hour of June 1<sup>st</sup> class session Ouiz 2 Review Individual work 2 pages of notes (any sized paper), double sided Basic calculators allowed NO smartphones, laptop, book, Internet, group work L19.14

14

16

13

CATCH UP FROM LECTURE 18

Switch to Lecture 18 Slides

Slides 18.20 to 18.38

TCS542: Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washington - Tacoma

15

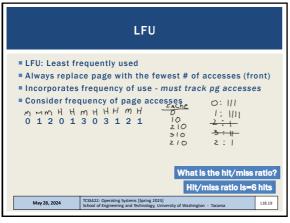

LFU

LFU: Least frequently used

Always replace page with the fewest # of accesses (front)

Incorporates frequency of use - must track pg accesses

Consider frequency of page accesses

0 1 2 0 1 3 0 3 1 2 1

What is the hit/miss ratio?

Hit/miss ratio is=6 hits

May 28, 2024

TCSS422: Operating Systems (Spring 2025)

School of Engineering and Technology, University of Washington - Taccims

19

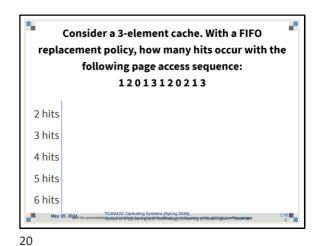

Consider a 3-element cache. With an LRU replacement policy, how many hits occur with the following page access sequence:

12013120213

2 hits

3 hits

4 hits

5 hits

6 hits

May 28, 2024: tap presenting 2014 tems (Spring 2025)

May 28, 2024: tap presenting 2014 tems (Spring 2025)

WORKLOAD EXAMPLES: NO-LOCALITY

In No-Locality (Random Access) Workload

Perform 10,000 random page accesses

Across set of 100 memory pages

The No-Locality Workload

When the cache is large enough to fit the entire workload, it doesn't matter which policy you use.

May 28, 2024

ITCS/422: Operating Systems (Spring 2025)

School of Engineering and Technology, University of Washington - Tacoma

22

21

WORKLOAD EXAMPLES: 80/20

= 80/20 Workload

• Perform 10,000 page accesses, against set of 100 pages

• 80% of accesses are to 20% of pages (hot pages)

• 20% of accesses are to 80% of pages (cold pages)

The 80-20 Workload

| COPT | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 | 1000 |

Cache Size (Blocks)

TCSS422: Operating Systems (Sp School of Engineering and Technology

23 24

L18.23

Slides by Wes J. Lloyd

May 28, 2024

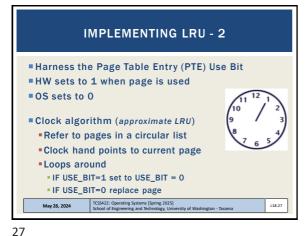

**IMPLEMENTING LRU** Implementing last recently used (LRU) requires tracking access time for all system memory pages Times can be tracked with a list For cache eviction, we must scan an entire list Consider: 4GB memory system (232), with 4KB pages (212) ■ This requires 2<sup>20</sup> comparisons !!! ■ Simplification is needed Consider how to approximate the oldest page access L18.26 ersity of Washington - Tacoma

26

**CLOCK ALGORITHM** Not as efficient as LRU, but better than other replacement algorithms that do not consider history May 28, 2024 L18.28

28

30

**CLOCK ALGORITHM - 2** Consider dirty pages in cache If DIRTY (modified) bit is FALSE No cost to evict page from cache If DIRTY (modified) bit is TRUE Cache eviction requires updating memory Contents have changed Clock algorithm should favor no cost eviction TCSS422: Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washington - Tacoma May 28, 2024 L18.29 29

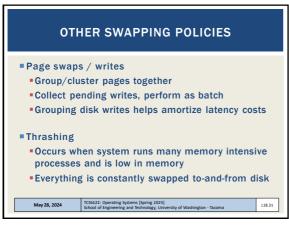

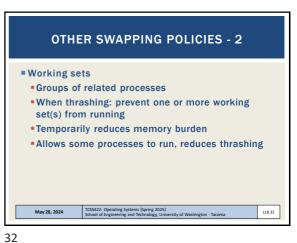

WHEN TO LOAD PAGES ■ On demand → demand paging Prefetching Preload pages based on anticipated demand Prediction based on locality Access page P, suggest page P+1 may be used What other techniques might help anticipate required memory pages? Prediction models, historical analysis • In general: accuracy vs. effort tradeoff High analysis techniques struggle to respond in real time May 28, 2024 TCSS422: Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washington - Tacoma L18.30

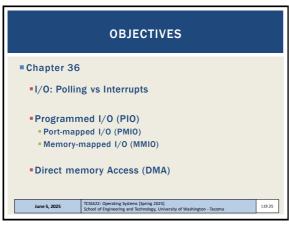

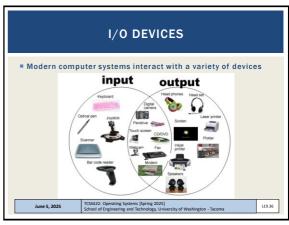

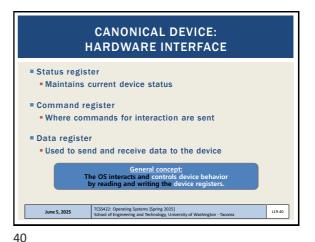

CHAPTER 36:

I/O DEVICES

June 5, 2025

TGSS422. Operating Systems (Spring 2020)

School of Engineering and Technology, University of Washington, 11. oma 1.19.34

34

33

35 36

Slides by Wes J. Lloyd

L19.6

.

41 42

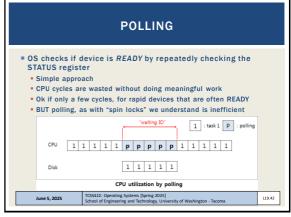

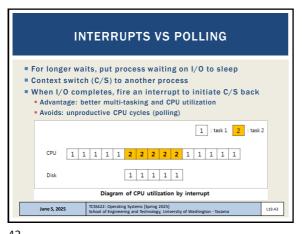

Unterrupts vs Polling - 2

What is the tradeoff space?

Interrupts are not always the best solution

How long does the device I/O require?

What is the cost of context switching?

If device I/O is fast → polling is better.

When I/O time < 1 CPU time slice (e.g. 10 ms)

If device I/O is slow → interrupts are better.

When I/O time > 1 CPU time slice

43 44

INTERRUPTS VS POLLING - 3

Alternative: two-phase hybrid approach

Initially poll, then sleep and use interrupts

Issue: livelock problem

Common with network I/O

Many arriving packets generate many many interrupts

Overloads the CPU!

No time to execute code, just interrupt handlers!

Livelock optimization

Coalesce multiple arriving packets (for different processes) into fewer interrupts

Must consider number of interrupts a device could generate

1058422: Operating Systems (Spring 2025)

School of Engineering and Technology, University of Washington - Tacoma

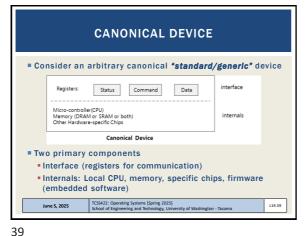

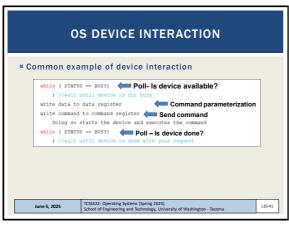

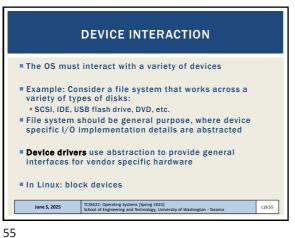

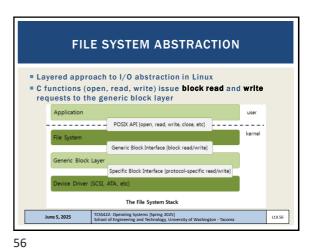

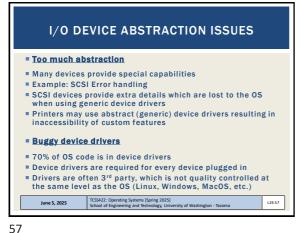

DEVICE I/O

To interact with a device we must send/receive DATA

Two general approaches:

Programmed I/O (PIO):

Port mapped I/O (PMIO)

Memory mapped I/O (MMIO)

Direct memory access (DMA)

46

45

| Transfer Modes  |                       |                              |            |  |  |  |

|-----------------|-----------------------|------------------------------|------------|--|--|--|

| Mode ¢          | # +                   | Maximum transfer rate (MB/s) | cycle time |  |  |  |

|                 | 0                     | 3.3                          | 600 ns     |  |  |  |

| PIO             | 1                     | 5.2                          | 383 ns     |  |  |  |

|                 | 2                     | 8.3                          | 240 ns     |  |  |  |

|                 | 3                     | 11.1                         | 180 ns     |  |  |  |

|                 | 4                     | 16.7                         | 120 ns     |  |  |  |

| 1               | 0                     | 2.1                          | 960 ns     |  |  |  |

| Single-word DMA | 1                     | 4.2                          | 480 ns     |  |  |  |

|                 | 2                     | 8.3                          | 240 ns     |  |  |  |

| Multi-word DMA  | 0                     | 4.2                          | 480 ns     |  |  |  |

|                 | 1                     | 13.3                         | 150 ns     |  |  |  |

|                 | 2                     | 16.7                         | 120 ns     |  |  |  |

|                 | 3[34]                 | 20                           | 100 ns     |  |  |  |

|                 | 4[34]                 | 25                           | 80 ns      |  |  |  |

|                 | 0                     | 16.7                         | 240 ns + 2 |  |  |  |

| Ultra DMA       | 1                     | 25.0                         | 160 ns + 2 |  |  |  |

|                 | 2 (Ultra ATA/33)      | 33.3                         | 120 ns + 2 |  |  |  |

|                 | 3                     | 44.4                         | 90 ns + 2  |  |  |  |

|                 | 4 (Ultra ATA/66)      | 66.7                         | 60 ns + 2  |  |  |  |

|                 | 5 (Ultra ATA/100)     | 100                          | 40 ns + 2  |  |  |  |

|                 | 6 (Ultra ATA/133)     | 133                          | 30 ns + 2  |  |  |  |

|                 | 7 (Ultra ATA/167)[35] | 167                          | 24 ns + 2  |  |  |  |

PROGRAMMED I/O (PIO)

I 1/O performed on the CPU

CPU time is consumed performing I/O

CPU supports data movement (input/output)

PIO

Cover-burdened

1: task 1 2: task 2

C: copy data from memory

CPU 1 1 1 1 1 C C C 2 2 2 2 2 1 1 1

Disk

Diagram of CPU utilization

1: task 2 2: task 2 3: task 2 4: task 2 5: t

47 48

PROGRAMMED I/O DEVICE (PIO)

INTERACTION

Two primary PIO methods

Port mapped I/O (PMIO)

Memory mapped I/O (MMIO)

TCSS422: Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washington - Tacoma

49

PORT MAPPED I/O (PMIO)

■ Device specific CPU I/O Instructions

■ Follows a Complex Instruction Set - CISC model (Intel):

■ Specific CPU instructions are used for device I/O

■ x86/x86-64: in and out instructions

■ outb, outw, outl

■ 1, 2, 4 byte copy from EAX → device's I/O port

51

54

50

June 5, 2025

52

62

64

61

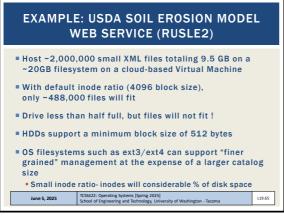

**EXAMPLE: USDA SOIL EROSION MODEL** WEB SERVICE (RUSLE2) - 2 ■ Free space in bytes (df) total size bytes-used bytes-free usage /dev/vda2 13315844 9556412 3049188 76%/mnt ■ Free inodes (df -i) @ 512 bytes / node Device total inodes used free usage 3552528 1999823 1552705 57% /mnt /dev/vda2 June 5, 2025 L19.66 ersity of Washington - Tacoma

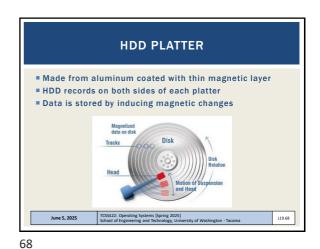

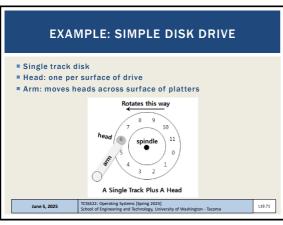

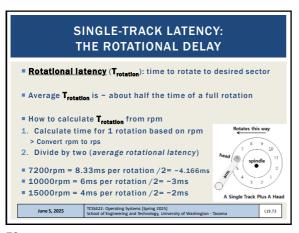

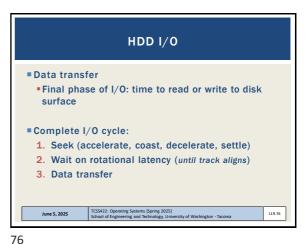

**HDD SPINDLE** Connected to motor which spins the disk ■ Speed measures in RPM (rotations per minute) ■ Typical: 7200-15000 rpm ■ 10000 rpm - 1 rotation in 6ms; 15k rpm 1 rotation in 4ms Tracks June 5, 2025 L19.69

**HDD TRACK** ■ Concentric circle of sectors ■ Single side of platter contains 290 K tracks (2008) Zones: groups of tracks with same # of sectors Outer tracks have More sectors June 5, 2025 L19.70

70

72

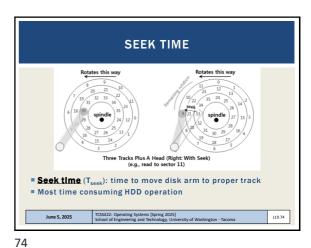

HARD DISK STRUCTURE June 5, 2025 L19.72

Slides by Wes J. Lloyd

75 7

83 84

07

89 90

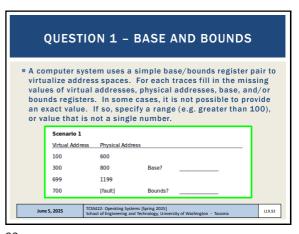

| Q1 - 2                                                                                                                        |                                                                      |      |                  |      |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------|------------------|------|--|--|--|

|                                                                                                                               | Scenario 2 <br><u>Virtual Address</u><br>300<br>1600<br>1801<br>2801 | 2800 | Base?<br>Bounds? |      |  |  |  |

|                                                                                                                               | Scenario 3 Virtual Address                                           | 1100 | Base?<br>Bounds? | 2000 |  |  |  |

| June 5, 2025 TCS5422: Operating Systems (Spring 2025) School of Engineering and Technology, University of Washington - Tacoma |                                                                      |      |                  |      |  |  |  |

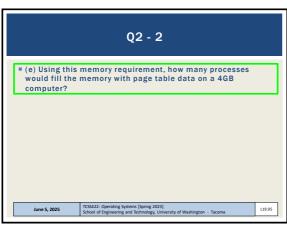

| Consider a computer with 4 GB (2<sup>32</sup>) of physical memory, where the page size is 4 KB (2<sup>12</sup>). For simplicity assume than 1GB=1000MB, 1MB=1000KB, 1KB=1000 bytes

| (a) How many pages must be tracked by a single-level page table if the computer has 4GB (2<sup>32</sup>) of physical memory and the page size is 4 KB (2<sup>12</sup>)?

| (b) How many bits are required for the virtual page number (VPN) to address any page within this 4GB (2<sup>32</sup>) memory space?

| (c) Assuming that the smallest addressable unit of memory within a page is a byte (8-bits), how many bits are required for the offset to refer to any byte in the 4 KB page?

| (d) Assuming each page table entry (PTE) requires 4 bytes of memory, how much memory is required to store the page table for one process (in MB)?

| June 5, 2025 | TCSS22: Operating Systems [Spring 2025] | Colorenting Systems [Spring 2025] |

94

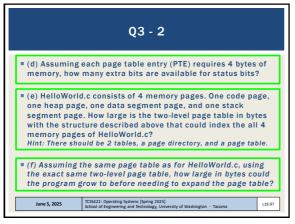

**QUESTION 3 - TWO-LEVEL PAGE TABLE**  Consider a computer with 1 GB (2<sup>30</sup>) of physical memory where the page size is 1024 bytes (1KB) ( $2^{10}$ ). We would like to index memory pages using a two level page table consisting of a page directory which refers to page tables which are created on demand to index the entire memory space. For simplicity assume than 1GB=1000MB, 1MB=1000KB, 1KB=1000 bytes (a) For a two-level page table, divide the VPN in half. How many bits are required for the page directory index (PDI) in a two-level scheme? (b) How many bits are required for the page table index (PTI)? (c) How many bits are required for an offset to address any byte in the 1 KB page? TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, University of Washington - Tacoma June 5, 2025 L19.96

95 96

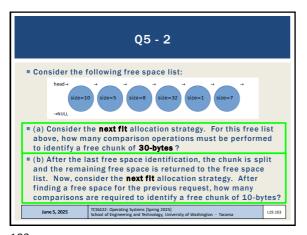

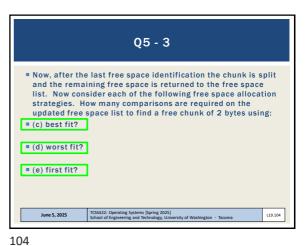

QUESTION 4 - CACHE TRACING

Consider a 3-element cache with the cache arrival sequences below.

Determine the number of cache hits and cache misses using each of the following cache replacement policies:

A Optimal policy

Arrival sequence:

Cache 1:

Cache 1:

Cache 3:

# Hits:

# Misses:

TCSS422: Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washington - Tacoma

99

Q4 - 3

C. LRU policy

Arrival sequence:

Cache 1:

5 3 7 5 3 1 0 7 1 6 4 3 2 1 3

Cache 2:

Cache 3:

# Hits:

# Misses:

June 5, 2025

School of Engineering and Technology, University of Washington - Tacoma

L19.101

101

102

98

100