FEEDBACK FROM 5/23 Which method of memory segmentation is best for an online multiplayer game? Starting with early Intel 32-bit processors (i386) paging support was added to CPUs (~1986), and segmentation largely was replaced with paging throughout operating systems Pure segmentation based approaches were used to manage memory on earlier systems: Intel 16-bit i286 Mainframes TCSS422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Tacoma May 28, 2024 L18.6

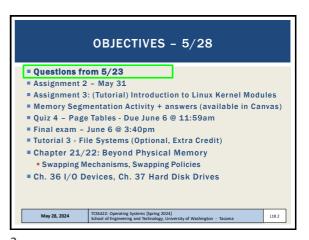

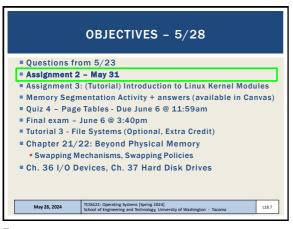

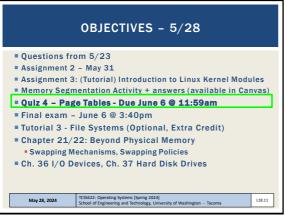

OBJECTIVES - 5/28

Questions from 5/23

Assignment 2 - May 31

Assignment 3: (Tutorial) Introduction to Linux Kernel Modules

Memory Segmentation Activity + answers (available in Canvas)

Quiz 4 - Page Tables - Due June 6 @ 11:59am

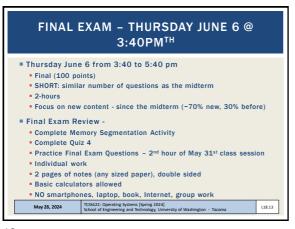

Final exam - June 6 @ 3:40pm

Tutorial 3 - File Systems (Optional, Extra Credit)

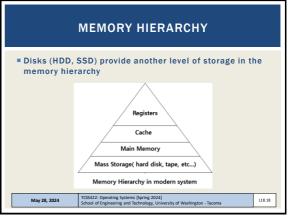

Chapter 21/22: Beyond Physical Memory

Swapping Mechanisms, Swapping Policies

Ch. 36 I/O Devices, Ch. 37 Hard Disk Drives

May 28, 2024

TCSS42: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Taxoma

10

9

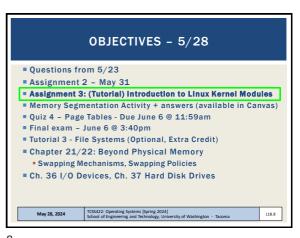

OBJECTIVES - 5/28

Questions from 5/23

Assignment 2 - May 31

Assignment 3: (Tutorial) Introduction to Linux Kernel Modules

Memory Segmentation Activity + answers (available in Canvas)

Quiz 4 - Page Tables - Due June 6 @ 11:59am

Final exam - June 6 @ 3:40pm

Tutorial 3 - File Systems (Optional, Extra Credit)

Chapter 21/22: Beyond Physical Memory

Swapping Mechanisms, Swapping Policies

Ch. 36 I/O Devices, Ch. 37 Hard Disk Drives

May 28, 2024

TCSS42: Operating Systems [Syring 2024]

School of Engineering and Technology, University of Washington - Tacoma

11 12

Slides by Wes J. Lloyd

L18.2

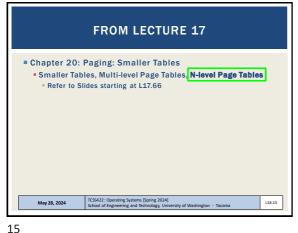

**OBJECTIVES - 5/28** ■ Questions from 5/23 Assignment 2 - May 31 Assignment 3: (Tutorial) Introduction to Linux Kernel Modules Memory Segmentation Activity + answers (available in Canvas) Quiz 4 - Page Tables - Due June 6 @ 11:59am Final exam - June 6 @ 3:40pm Tutorial 3 - File Systems (Optional, Extra Credit) Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies Ch. 36 I/O Devices, Ch. 37 Hard Disk Drives May 28, 2024 L18.14

14

16

13

**OBJECTIVES - 5/28** ■ Questions from 5/23 Assignment 2 - May 31 Assignment 3: (Tutorial) Introduction to Linux Kernel Modules ■ Memory Segmentation Activity + answers (available in Canvas) Quiz 4 - Page Tables - Due June 6 @ 11:59am ■ Final exam - June 6 @ 3:40pm Tutorial 3 - File Systems (Optional, Extra Credit) Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies Ch. 36 I/O Devices, Ch. 37 Hard Disk Drives May 28, 2024 L18.16

17 18

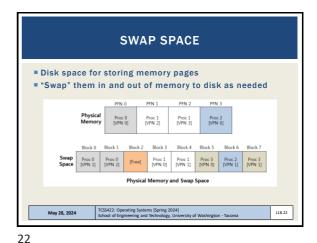

**SWAP SPACE - 3** Swap space lives on a separate logical volume in Ubuntu Linux that is managed separately from the root file system Check logical volumes with "sudo lvdisplay" command: See also "Ivm Ivs" command May 28, 2024 L18.24 ersity of Washington - Tacoma

23 24

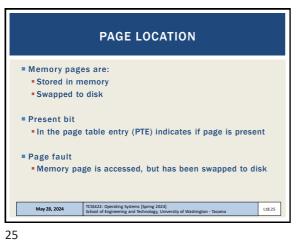

**PAGE FAULT** OS steps in to handle the page fault Loading page from disk requires a free memory page ■ Page-Fault Algorithm PFN = FindFreePhysicalPage() PFN = EvictPage() // run replacement algorith 4: DiskRead(PTE.DiskAddr, pfn) PTE.present = True // set PTE bit to present 5: // reference new loaded page RetryInstruction() // retry instruction May 28, 2024 L18.26 ersity of Washington - Tacoma

26

**OBJECTIVES - 5/28** ■ Questions from 5/23 Assignment 2 - May 31 Assignment 3: (Tutorial) Introduction to Linux Kernel Modules ■ Memory Segmentation Activity + answers (available in Canvas) Quiz 4 - Page Tables - Due June 6 @ 11:59am ■ Final exam - June 6 @ 3:40pm ■ Tutorial 3 - File Systems (Optional, Extra Credit) Chapter 21/22: Beyond Physical Memory Swapping Mechanisms

Swapping Policies Ch. 36 I/O Devices, Ch. 37 Hard Disk Drives May 28, 2024 L18.28

28

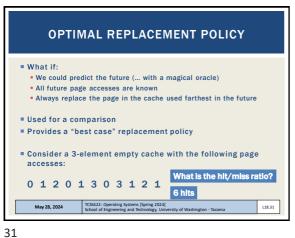

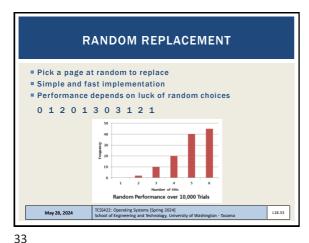

**CACHE MANAGEMENT** Replacement policies apply to "any" cache Goal is to minimize the number of misses Average memory access time (AMAT) can be estimated:  $AMAT = (P_{Hit} * T_M) + (P_{Miss} * T_D)$ Meaning The cost of accessing memory (time) The cost of accessing disk (time) The probability of finding the data item in the cache(a hit) The probability of not finding the data in the cache(a miss Consider T<sub>M</sub> = 100 ns, T<sub>D</sub> = 10ms • Consider  $P_{hit}$  = .9 (90%),  $P_{miss}$  = .1 ■ Consider P<sub>hit</sub> = .999 (99.9%), P<sub>miss</sub> = .001 TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma May 28, 2024 L18.30

30

Slides by Wes J. Lloyd

**FIFO REPLACEMENT** Oueue based Always replace the oldest element at the back of cache ■ Simple to implement Doesn't consider importance... just arrival ordering Consider a 3-element empty cache with the following 0 1 2 0 1 3 0 3 1 2 1 4 hits ■ What is the hit/miss ratio? LRU inc How is FIFO different than LRU? May 28, 2024 L18.32

32

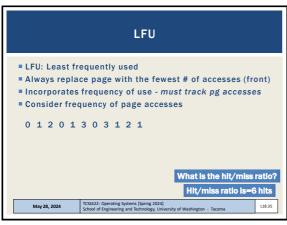

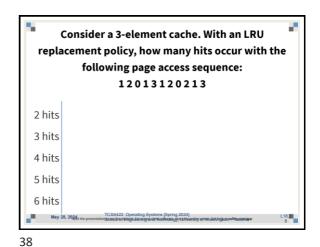

**HISTORY-BASED POLICIES** ■ LRU: Least recently used Always replace page with oldest access time (front) Always move end of cache when element is read again LRU requires constant reorganization of the cache Considers temporal locality (when pg was last accessed) What is the hit/miss ratio? 0 1 2 0 1 3 0 3 1 2 1 6 hits ■ LFU: Least frequently used Always replace page with the fewest # of accesses (front) ■ Incorporates frequency of use - must track pg accesses Consider frequency of page accesses 0 1 2 0 1 3 0 3 1 2 1 May 28, 2024 L18.34

34

35 36

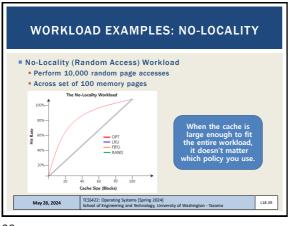

**WORKLOAD EXAMPLES: 80/20** ■ 80/20 Workload Perform 10,000 page accesses, against set of 100 pages 80% of accesses are to 20% of pages (hot pages) 20% of accesses are to 80% of pages (cold pages) LRU is more likely to hold onto hot pages (recalls history) May 28, 2024 L18.40

40

39

**WORKLOAD EXAMPLES: SEQUENTIAL** Looping sequential workload Refer to 50 pages in sequence: 0, 1, ..., 49 Repeat loop Random performs better than FIFO and LRU for cache sizes < 50 Algorithms should provide TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, Uni May 28, 2024 L18.41 41

With small cache sizes, for the looping sequential workload, why do FIFO and LRU fail to provide cache om. Unpredictable accesses require a random cache replacement policy for cache hits dly are too spread apart temporally to benefit from caching Unlike Random cache replacement, both FIFO and LRU fail to speculate memory accesses in advance to improve caching

42

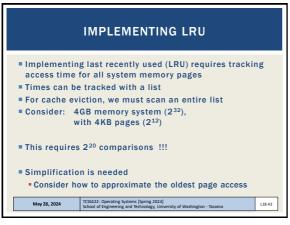

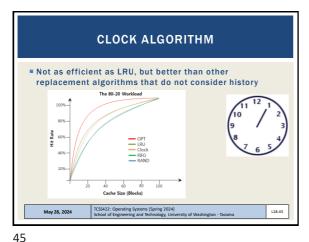

IMPLEMENTING LRU - 2

Harness the Page Table Entry (PTE) Use Bit

HW sets to 1 when page is used

OS sets to 0

Clock algorithm (approximate LRU)

Refer to pages in a circular list

Clock hand points to current page

Loops around

IF USE\_BIT=1 set to USE\_BIT = 0

IF USE\_BIT=1 replace page

May 28, 2024

ICCS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma

43 44

CLOCK ALGORITHM - 2

Consider dirty pages in cache

If DIRTY (modified) bit is FALSE

No cost to evict page from cache

If DIRTY (modified) bit is TRUE

Cache eviction requires updating memory

Contents have changed

Clock algorithm should favor no cost eviction

46

45

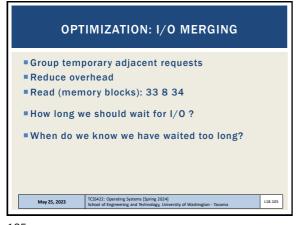

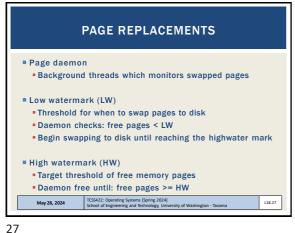

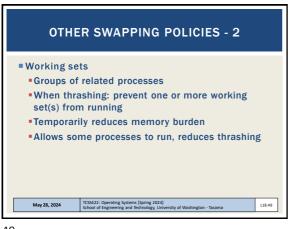

OTHER SWAPPING POLICIES

Page swaps / writes

Group/cluster pages together

Collect pending writes, perform as batch

Grouping disk writes helps amortize latency costs

Thrashing

Occurs when system runs many memory intensive processes and is low in memory

Everything is constantly swapped to-and-from disk

May 28, 2024

TXSS422: Operating Systems Ispring 2024|

School of Engineering and Technology, University of Washington - Tacoma

LIS. 48

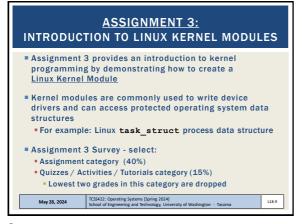

OBJECTIVES - 5/28

Questions from 5/23

Assignment 2 - May 31

Assignment 3: (Tutorial) Introduction to Linux Kernel Modules

Memory Segmentation Activity + answers (available in Canvas)

Quiz 4 - Page Tables - Due June 6 @ 11:59am

Final exam - June 6 @ 3:40pm

Tutorial 3 - File Systems (Optional, Extra Credit)

Chapter 21/22: Beyond Physical Memory

Swapping Mechanisms, Swapping Policies

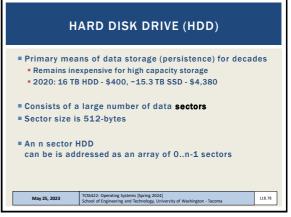

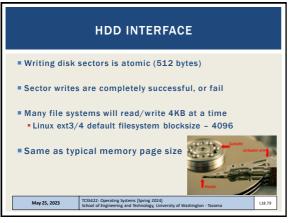

Ch. 36 I/O Devices

Ch. 37 Hard Disk Drives

50

52

54

49

...

OBJECTIVES

Chapter 36

I/O: Polling vs Interrupts

Programmed I/O (PIO)

Port-mapped I/O (PMIO)

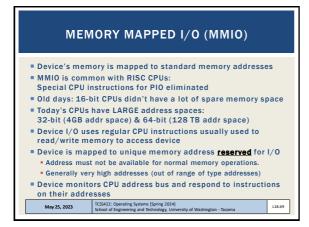

Memory-mapped I/O (MMIO)

Direct memory Access (DMA)

May 25, 2023

CS422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Tacoma

51

I/O DEVICES

Modern computer systems interact with a variety of devices

input

Output

Factorian COCK/O Parker

Forse

Forse

TCSS422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Tacoma

L18.53

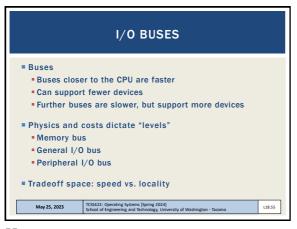

COMPUTER SYSTEM ARCHITECTURE

CPU

Memory

Memory Bus

(proprietarly)

General I/O Bus

(e.g., PCI)

Peripheral I/O Bus

(e.g., SCSI, SATA, USB)

Prototypical System Architecture

VERY FAST: CPU is attached to main memory via a Memory bus.

FAST: High speed devices (e.g. video) are connected via a General I/O bus.

SLOWER: Disks are connected via a Peripheral I/O bus.

TXSS422 Operating Systems (prima 2024)

School of Engineering and Technology, University of Washington -Taxoma

Slides by Wes J. Lloyd

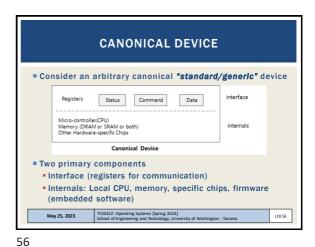

CANONICAL DEVICE:

HARDWARE INTERFACE

Status register

Maintains current device status

Command register

Where commands for interaction are sent

Data register

Used to send and receive data to the device

General concept:

The OS interacts and controls device behavior by reading and writing the device registers.

May 25, 2023

TCSS422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington -Tacoma

57

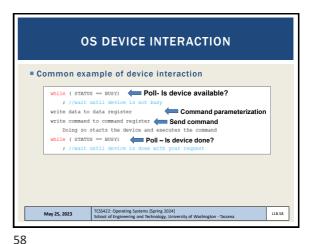

POLLING

OS checks if device is READY by repeatedly checking the STATUS register

Simple approach

CPU cycles are wasted without doing meaningful work

Ok if only a few cycles, for rapid devices that are often READY

BUT polling, as with "spin locks" we understand is inefficient

Wasting IO'

CPU 1 1 1 1 1 1 P P P P P 1 1 1 1 1 1

Disk

CPU utilization by polling

TCSS422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Wassington - Taxoma

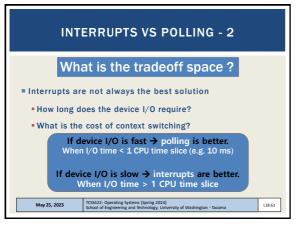

INTERRUPTS VS POLLING

For longer waits, put process waiting on I/O to sleep

Context switch (C/S) to another process

When I/O completes, fire an interrupt to initiate C/S back

Advantage: better multi-tasking and CPU utilization

Avoids: unproductive CPU cycles (polling)

1: task 1 2: task 2

CPU 1 1 1 1 1 2 2 2 2 2 1 1 1 1 1

Disk 1 1 1 1 1 1

Diagram of CPU utilization by interrupt

TCSS42: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Tacoma

60

INTERRUPTS VS POLLING - 3

Alternative: two-phase hybrid approach

Initially poll, then sleep and use interrupts

Issue: livelock problem

Common with network I/O

Many arriving packets generate many many interrupts

Overloads the CPU!

No time to execute code, just interrupt handlers!

Livelock optimization

Coalesce multiple arriving packets (for different processes) into fewer interrupts

Must consider number of interrupts a device could generate

62

61

| DEVICE I/O        |                                                                                                                     |        |

|-------------------|---------------------------------------------------------------------------------------------------------------------|--------|

| ■To interact DATA | with a device we must send/receive                                                                                  |        |

| There are to      | wo general approaches:                                                                                              |        |

| · ·               | ned I/O (PIO):                                                                                                      |        |

|                   | pped I/O (PMIO)<br>mapped I/O (MMIO)                                                                                |        |

| Direct me         | mory access (DMA)                                                                                                   |        |

|                   |                                                                                                                     |        |

| May 25, 2023      | TCSS422: Operating Systems [Spring 2024]<br>School of Engineering and Technology, University of Washington - Tacoma | L18.63 |

Transfer Modes um transfer rate

cycle time 5.2 383 ns PIO 8.3 240 ns 11.1 180 ns 16.7 120 ns 2.1 960 ns ingle-word DMA 4.2 480 ns 42 480 ns 13.3 150 ns Multi-word DMA 16.7 120 ns 20 100 ns 16.7 240 ns + 2 25.0 160 ns + 2 2 (Ultra ATA/33) 33.3 120 ns + 2 44.4 90 ns + 2 Ultra DMA 4 (Ultra ATA/66) 5 (Ultra ATA/100) 100 40 ns + 2 6 (Ultra ATA/133) 133 30 ns + 2 7 (Ultra ATA/167)[3 167 24 ns + 2

63 64

| PROGRAMMED I/O (PIO) |                                                                                                                  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| ■ CPU supports       | d on the CPU consumed performing I/O s data movement (input/output) CPU is occupied with meaningless work        |  |  |

| PIO                  | "over-burdened"  1 : task 1 2 : task 2  C : copy data from memory                                                |  |  |

| CPU 1 1              | 1 1 0 0 0 2 2 2 2 1 1 1                                                                                          |  |  |

|                      | Diagram of CPU utilization                                                                                       |  |  |

| May 25, 2023         | TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma |  |  |

PIO DEVICES

Legacy serial ports

Legacy parallel ports

PS/2 keyboard and mouse

Legacy MIDI, joysticks

Old network interfaces

TCSS422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Tacoma

65 66

PORT MAPPED I/O (PMIO)

■ Device specific CPU I/O Instructions

■ Follows a CISC model:

specific CPU instructions used for device I/O

■ x86-x86-64: in and out instructions

■ outb, outw, out1

■ 1, 2, 4 byte copy from EAX → device's I/O port

67

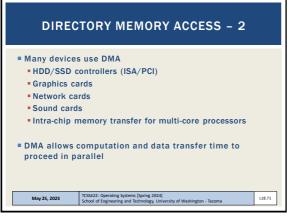

DIRECT MEMORY ACCESS (DMA)

- Copy data in memory by offloading to "DMA controller"

- Many devices (including CPUs) integrate DMA controllers

- CPU gives DMA: memory address, size, and copy instruction

- DMA performs I/O independent of the CPU

- DMA controller generates CPU interrupt when I/O completes

- CPU 1 1 1 1 2 2 2 2 2 2 2 1 1 1

DMA CDISK DIAGRAPH OF CPU utilization by DMA

Disk Diagram of CPU utilization by DMA

TESSEZ: Operating Systems [Spring 2024]

TESSEZ: Operating Systems [Spring 2024]

May 25, 2023 Stood of Engineering and Technology, University of Washington - Tacoma

69

70

72

68

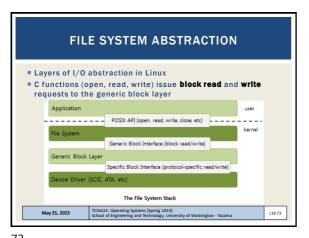

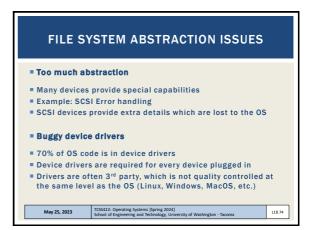

DEVICE INTERACTION

The OS must interact with a variety of devices

Example: Consider a file system that works across a variety of types of disks:

SCSI, IDE, USB flash drive, DVD, etc.

File system should be general purpose, where device specific I/O implementation details are abstracted

Device drivers use abstraction to provide general interfaces for vendor specific hardware

In Linux: block devices

May 25, 2023

TSSS22: Operating Systems (Spring, 2024)

Shoot of Engineering and Technology, University of Washington - Taxoma

L18.72

73

77 78

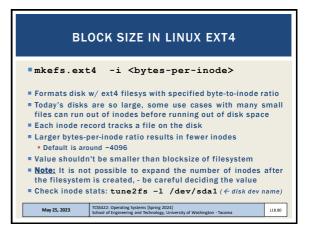

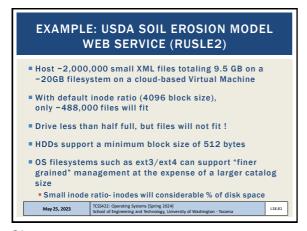

**EXAMPLE: USDA SOIL EROSION MODEL** WEB SERVICE (RUSLE2) - 2 ■ Free space in bytes (df) total size bytes-used bytes-free usage /dev/vda2 13315844 9556412 3049188 76%/mnt ■ Free inodes (df -i) @ 512 bytes / node Device total inodes used free usage 3552528 1999823 1552705 57% /mnt /dev/vda2 May 25, 2023 L18.82

82

81

84

EXAMPLE: SIMPLE DISK DRIVE

Single track disk

Head: one per surface of drive

Arm: moves heads across surface of platters

Rotates this way

head

spindle

spindle

11

0

A Single Track Plus A Head

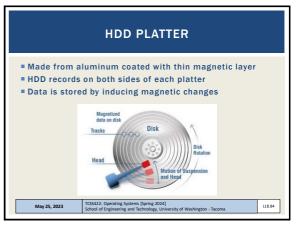

HARD DISK STRUCTURE

track f spinalle

cylinder c spinalle

rad write head

May 25, 2023 | TSSA22. Opening Systems (Sping 2028) | Catool of Engineering and Technology, University of Washington - Taxoma

87

May 25, 2023

SINGLE-TRACK LATENCY:

THE ROTATIONAL DELAY

Rotational latency (Trotation): time to rotate to desired sector

Average Trotation is ~ about half the time of a full rotation

How to calculate Trotation from rpm

Calculate time for 1 rotation based on rpm

Convert rpm to rps

Divide by two (average rotational latency)

7200rpm = 8.33ms per rotation /2= ~4.166ms

10000rpm = 6ms per rotation /2= ~3ms

15000rpm = 4ms per rotation /2= ~2ms

A Single Track Plus A Head

115.50

115.50

115.50

115.50

115.50

SEEK TIME

Rotates this way

Population of the proper track and the proper track

Seek time (T<sub>seek</sub>): time to move disk arm to proper track

May 25, 2023

May 25, 2023

Rotates this way

Rota

90

88

L18.87

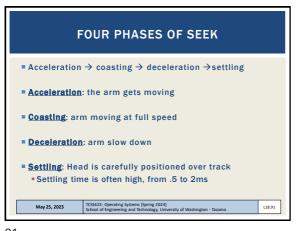

## Data transfer

# Final phase of I/O: time to read or write to disk surface

## Complete I/O cycle:

1. Seek (accelerate, coast, decelerate, settle)

2. Wait on rotational latency (until track aligns)

3. Data transfer

91

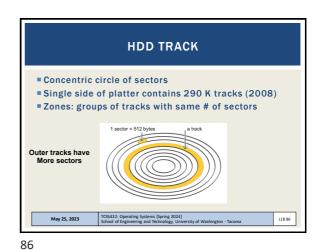

TRACK SKEW

Sectors are offset across tracks to allow time for head to reposition for sequential reads

Without track skew, when head is repositioned sector would have already been passed

Rotates this way

Three Tracks: Track Skew Of 2

May 25, 2023

TCS5422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Tacoma

TRACK SKEW - 2

TRACK SKEW - 2

Track Skew - 2

May 25, 2023

TCS542: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

93

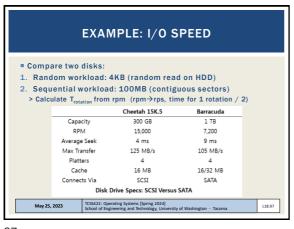

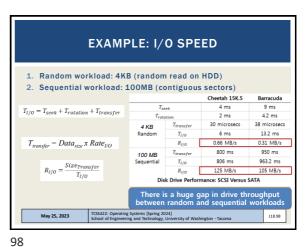

TRANSFER SPEED

Can calculate I/O transfer speed with:

I/O Time:  $T_{I/O} = T_{seek} + T_{rotation} + T_{transfer}$ Transfer = DATA<sub>size</sub> x Rate<sub>I/O</sub>

Rate of I/O:  $R_{I/O} = \frac{Size_{Transfer}}{T_{I/O}}$

96

92

94

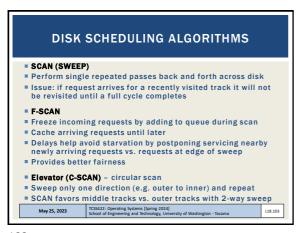

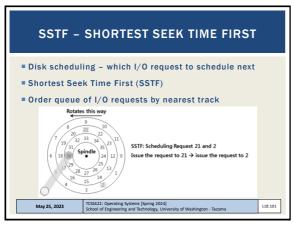

DISK SCHEDULING

Disk scheduler: determine how to order I/O requests

Multiple levels - OS and HW

OS: provides ordering

HW: further optimizes using intricate details of physical HDD implementation and state

May 25, 2023

TCS5422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

99 100

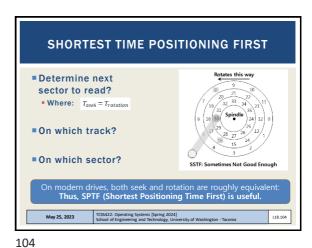

SSTF ISSUES

Problem 1: HDD abstraction

Drive geometry not available to OS. Nearest-block-first is a comparable alternate algorithm.

Problem 2: Starvation

Steady stream of requests for local tracks may prevent arm from traversing to other side of platter

May 25, 2023

TCSS42: Operating Systems | Spring 2024| School of Engineering and Technology, University of Washington - Tacoma

101 102