Slides by Wes J. Lloyd

2<sup>1</sup> 2 2<sup>17</sup> 131.072 2<sup>33</sup> 8.589.934.592 249 562,949,953,421,312

| 2-                       | 4      | 2                          | 131,072       | 2                           | 8,389,934,392       | 12.                     | 362,949,933,421,312        |

|--------------------------|--------|----------------------------|---------------|-----------------------------|---------------------|-------------------------|----------------------------|

| 2 <sup>2</sup>           | 4      | 218                        | 262,144       | 234                         | 17,179,869,184      | 250                     | 1,125,899,906,842,624      |

| 2 <sup>3</sup>           | 8      | 219                        | 524,288       | 235                         | 34,359,738,368      | 2 <sup>51</sup>         | 2,251,799,813,685,248      |

| 24                       | 16     | 2 <sup>20</sup><br>megaby  | 1,048,576     | 2 <sup>36</sup>             | 68,719,476,736      | 252                     | 4,503,599,627,370,496      |

| 2 <sup>5</sup>           | 32     | 221                        | 2,097,152     | 237                         | 137,438,953,472     | 253                     | 9,007,199,254,740,992      |

| 2 <sup>6</sup>           | 64     | 222                        | 4,194,304     | 238                         | 274,877,906,944     | 254                     | 18,014,398,509,481,984     |

| 27                       | 128    | 223                        | 8,388,608     | 239                         | 549,755,813,888     | 255                     | 36,028,797,018,963,968     |

| 28                       | 256    | 224                        | 16,777,216    | 2 <sup>40</sup><br>terabyte | 1,099,511,627,776   | 2 <sup>56</sup>         | 72,057,594,037,927,936     |

| 29                       | 512    | 2 <sup>25</sup>            | 33,554,432    | 241                         | 2,199,023,255,552   | 257                     | 144,115,188,075,855,872    |

| 2 <sup>10</sup><br>kilet | 1,024  | 2 <sup>26</sup>            | 67,108,864    | 242                         | 4,398,046,511,104   | 258                     | 288,230,376,151,711,744    |

| 211                      | 2,048  | 227                        | 134,217,728   | 243                         | 8,796,093,022,208   | 259                     | 576,460,752,303,423,488    |

| 212                      | 4,096  | 228                        | 268,435,456   | 244                         | 17,592,186,044,416  | 260                     | 1,152,921,504,606,846,976  |

| 2 <sup>13</sup>          | 8,192  | 229                        | 536,870,912   | 245                         | 35,184,372,088,832  | 261                     | 2,305,843,009,213,693,952  |

| 214                      | 16,384 | 2 <sup>30</sup><br>gigabyt | 1,073,741,824 | 246                         | 70,368,744,177,664  | 262                     | 4,611,686,018,427,387,904  |

| 2 <sup>15</sup>          | 32,768 | 231                        | 2,147,483,648 | 247                         | 140,737,488,355,328 | 263                     | 9,223,372,036,854,775,808  |

| 2 <sup>16</sup>          | 65,536 | 232                        | 4,294,967,296 | 248                         | 281,474,976,710,656 | 2 <sup>64</sup><br>bubb | 18,446,744,073,709,551,616 |

FEEDBACK - 4 How many bits are required to index the following amounts of memory? 1. 1,024 bytes = 1 kilobyte (2^10) → 10 bits 2. 1,024 kilobytes = 1 megabyte (2^20) → 20 bits 3. 1,024 megabytes = 1 gigabyte (2^30) → 30 bits 4. 1,024 gigabytes = 1 terabyte (2^40) → 40 bits 5. 1,024 terrabytes = 1 petabyte (2^50) → 50 bits May 29, 2025 L17.10

10

12

9

**FEEDBACK - 5** With paging, we divide an address space in fixed sized pieces (known as the page size) Assuming a computer indexes memory using 1 kilobyte memory pages (2^10) How many unique pages are required to manage/index memory?

1 kilobyte (2^10) of memory • 1 page ■ 1 megabyte (2^20) of memory 1024 pages (2^10)

1 gigabyte (2^30) of memory

1,048,576 pages (2^20)

1 terabyte (2^40) of memory 1,073,741,824 pages (2^30) 1 petabyte (2^50) of memory - 1,099,511,627,776 pages (2^40) TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, University of Washington - Tacoma May 29, 2025 L17.11 11

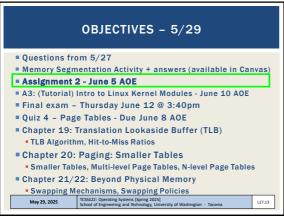

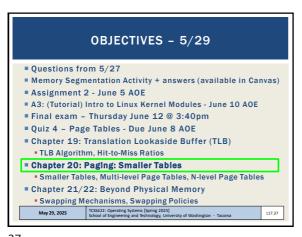

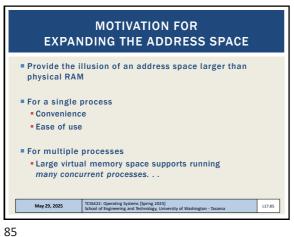

**OBJECTIVES - 5/29** ■ Questions from 5/27 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - June 5 AOE A3: (Tutorial) Intro to Linux Kernel Modules - June 10 A0E Final exam - Thursday June 12 @ 3:40pm Quiz 4 - Page Tables - Due June 8 AOE ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables ■ Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies May 29, 2025 TCSS422: Operating Systems (Spring 2025 School of Engineering and Technology, Ur L17.12

Slides by Wes J. Lloyd

**OBJECTIVES - 5/29** ■ Questions from 5/27 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - June 5 AOE = A3: (Tutorial) intro to Linux Kernel Modules - June 10 AOE ■ Final exam – Thursday June 12 @ 3:40pm Quiz 4 - Page Tables - Due June 8 AOE Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables ■ Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies May 29, 2025 TCSS422: Operating Systems (Spring 2025 School of Engineering and Technology, Ur L17.14

13 14

**OBJECTIVES - 5/29** ■ Questions from 5/27 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - June 5 AOE A3: (Tutorial) Intro to Linux Kernel Modules - June 10 AOE Final exam – Thursday June 12 @ 3:40pm Quiz 4 - Page Tables - Due June 8 AOE ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies TCSS422: Operating Systems [Spring 202: School of Engineering and Technology, U May 29, 2025 L17.16

16

18

15

FINAL EXAM - THURSDAY JUNE 12 @ 3:40PMTH ■ Thursday June 12 from 3:40 to 5:40 pm Final (100 points) Similar number of questions as the midterm 2-hours • Focus on new content - since the midterm (~70% new, 30% before) Final Exam Review - Complete Memory Segmentation Activity Complete Quiz 4 Practice Final Exam Questions – 2<sup>nd</sup> hour of June 5<sup>th</sup> class session Individual work 3 pages of notes (any sized paper), double sided Basic calculators allowed NO smartphones, laptop, book, Internet, group work May 29, 2025 TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, University of Washington - Tacoma L17.17 17

OBJECTIVES - 5/29 ■ Questions from 5/27 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - June 5 AOE A3: (Tutorial) Intro to Linux Kernel Modules - June 10 A0E Final exam - Thursday June 12 @ 3:40pm Quiz 4 - Page Tables - Due June 8 AOE Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables ■ Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies May 29, 2025 TCSS422: Operating Systems (Spring 2025 School of Engineering and Technology, Un L17.18 ersity of Washington - Tacoma

OBJECTIVES - 5/29

Questions from 5/27

Memory Segmentation Activity + answers (available in Canvas)

Assignment 2 - June 5 AOE

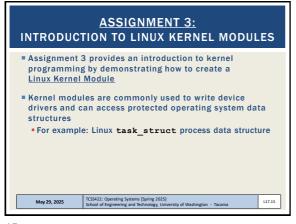

A3: (Tutorial) Intro to Linux Kernel Modules - June 10 AOE

Final exam - Thursday June 12 @ 3:40pm

Quiz 4 - Page Tables - Due June 8 AOE

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

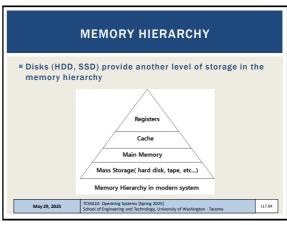

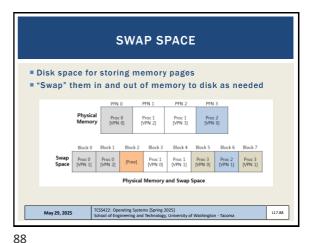

Chapter 21/22: Beyond Physical Memory

Swapping Mechanisms, Swapping Policies

May 29, 2025

TISSAUC Generals Systems (Spring 2025)

May 29, 2025

TSSAUC Generals Systems (Spring 2025)

May 29, 2025

TSSAUC Generals Systems (Spring 2025)

Stood of Engineering a University of Washington - Tacoma

117.20

19 20

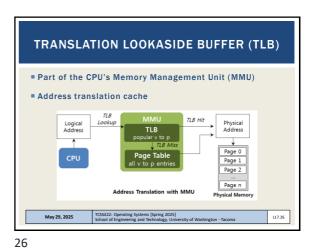

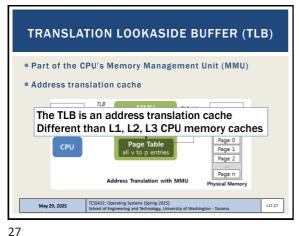

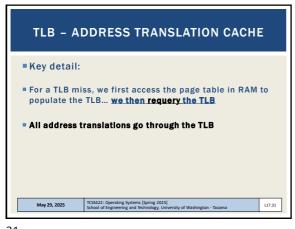

TRANSLATION LOOKASIDE BUFFER

■ Legacy name...

■ Better name, "Address Translation Cache"

■ TLB is an on CPU cache of address translations

■ virtual → physical memory

| TCSS422: Operating Systems | Spring 2025| | School of Engineering and Technology, University of Washington - Tacoma | 117.22

22

21

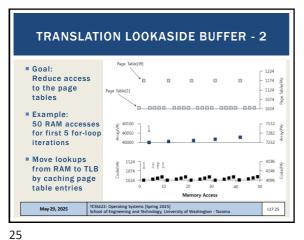

**VISUALIZING MEMORY ACCESSES:** FOR THE FIRST 5 LOOP ITERATIONS Locations: Page table 1174 Array 1124 • Code 1074 0 0000 0000 0000 0000 000 - 1024 50 accesses for 5 loop 7282 iterations 4146 May 29, 2025 L17.24

23 24

**OBJECTIVES - 5/29** ■ Questions from 5/27 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - June 5 AOE A3: (Tutorial) Intro to Linux Kernel Modules - June 10 AOE Final exam - Thursday June 12 @ 3:40pm Quiz 4 - Page Tables - Due June 8 AOE ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies May 29, 2025 L17.28

28

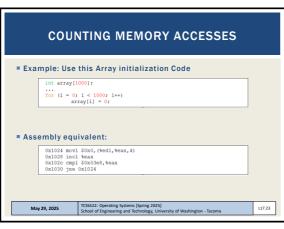

```

TLB BASIC ALGORITHM

For: array based page table

■ Hardware managed TLB

1: VPN = (VirtualAddress & VPN_MASK ) >> SHIFT

2: (Success , TlbEntry) = TLB_Lookup(VPN)

if(Success == True){ // TLB H

if(CanAccess(TlbEntry.ProtectBits) == True){

5:

Offset = VirtualAddress & OFFSET MASK

PhysAddr (TlbEntry.PFN << SHIFT) | Offset

AccessMemory( PhysAddr )

else RaiseException(PROTECTION_ERROR)

Generate the physical address to access memory

TCSS422: Operating Systems [Spring 2025]

School of Engineering and Technology, Uni

May 29, 2025

L17.29

```

**TLB BASIC ALGORITHM - 2** 11: else{ //TLB Mis: PTEAddr = PTBR + (VPN \* sizeof(PTE)) 12: ▶ PTE = AccessMemory(PTEAddr) 13: (...) // Check for, and raise exceptions... TLB\_Insert( VFN , PTE.PFN , PTE.ProtectBits)

RetryInstruction() 16: 17: 18: Retry the instruction... (requery the TLB) May 29, 2025 L17.30 rsity of Washington - Tacoma

29 30

**OBJECTIVES - 5/29** ■ Questions from 5/27 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - June 5 AOE A3: (Tutorial) Intro to Linux Kernel Modules - June 10 A0E Final exam - Thursday June 12 @ 3:40pm Quiz 4 - Page Tables - Due June 8 AOE ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, HIt-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables ■ Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies

May 29, 2025

TCSS422: Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washi L17.32

31 32

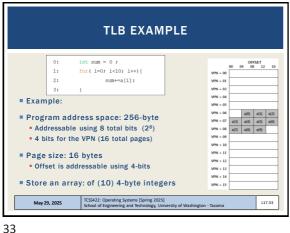

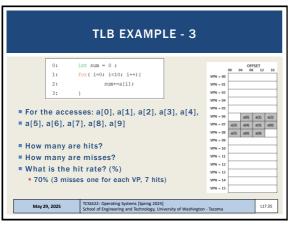

**TLB EXAMPLE - 2** for( i=0; i<10; i++){ VPN = 03 Consider the code above: VPN - 03 Initially the TLB does not know where a[] is Consider the accesses: VPN = 0 a[0], a[1], a[2], a[3], a[4], a[5], a[6], a[7], VPN = 10 a[8], a[9] How many pages are accessed? What happens when accessing a page not VPN - 14 in the TLB? May 29, 2025 L17.34

34

**TLB EXAMPLE - 4** for( i=0; i<10; i++){ 1: VPN = 03 VPN = 05 ■ What factors affect the hit/miss rate? Page size Data/Access locality (how is data accessed?) Sequential array access vs. random array access Temporal locality VPN = 12 • Size of the TLB cache VPN - 14 (how much history can you store?) TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, Uni May 29, 2025 L17.36

35 36

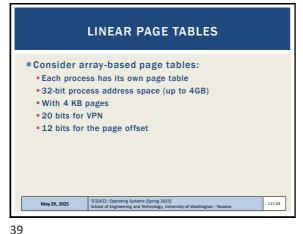

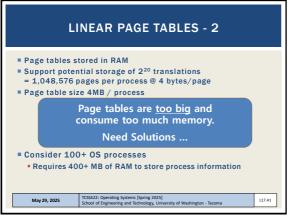

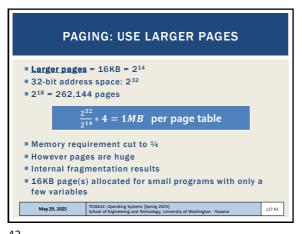

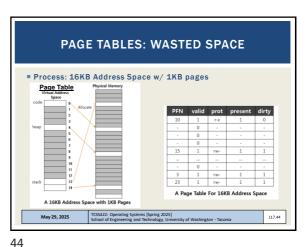

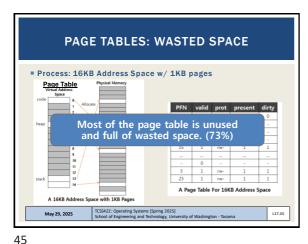

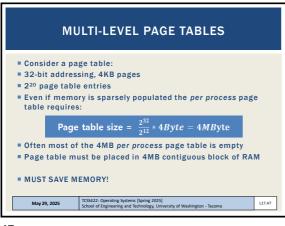

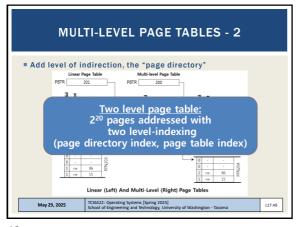

LINEAR PAGE TABLES - 2

Page tables stored in RAM

Support potential storage of 2<sup>20</sup> translations

= 1,048,576 pages per process @ 4 bytes/page

Page table size 4MB / process

Page table size = 2<sup>32</sup>/<sub>212</sub> \* 4Byte = 4MByte

Consider 100+ OS processes

Requires 400+ MB of RAM to store process information

TCS5422: Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washington - Tacoma

40

39

**OBJECTIVES - 5/29** ■ Questions from 5/27 ■ Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - June 5 AOE A3: (Tutorial) Intro to Linux Kernel Modules - June 10 A0E Final exam - Thursday June 12 @ 3:40pm Quiz 4 - Page Tables - Due June 8 AOE Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables Multi-level Page Tables, N-level Page Tables Chapter 21/22: Beyond Physical Memory Swapping Mechanisms, Swapping Policies TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, University of Washington - Tacoma May 29, 2025 L17.42

41 42

OBJECTIVES - 5/29

Questions from 5/27

Memory Segmentation Activity + answers (available in Canvas)

Assignment 2 - June 5 AOE

A3: (Tutorial) Intro to Linux Kernel Modules - June 10 AOE

Final exam - Thursday June 12 @ 3:40pm

Quiz 4 - Page Tables - Due June 8 AOE

Chapter 19: Translation Lookaside Buffer (TLB)

\*TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables

Smaller Tables

MultI-level Page Tables.

Chapter 21/22: Beyond Physical Memory

Swapping Mechanisms, Swapping Policies

May 29, 2025

| CONTROL | CONTR

46

43

47 48

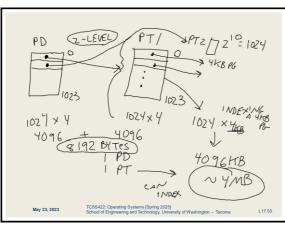

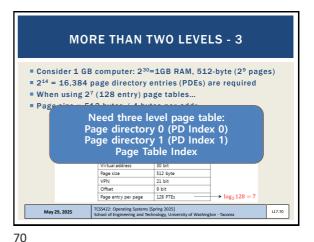

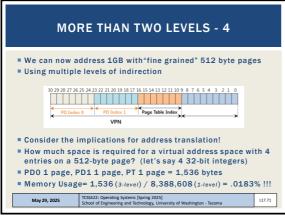

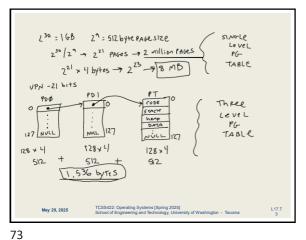

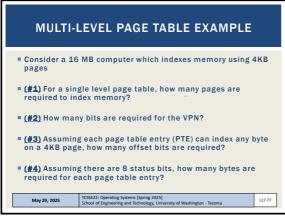

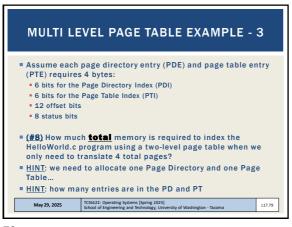

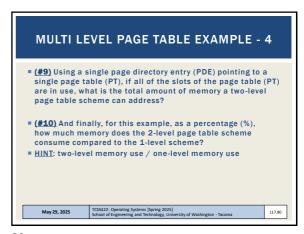

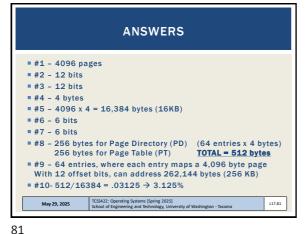

4 GB computer (2^32) and 4KB pages (2^12)

1. How much space is required for a 2-level page table with one page directory (PD) and one page table (PT)?

2. How much memory can a single PD pointing to a single PT address?

49

May 23, 2023 TCS8422-Operating Systems (Spring 2025).

May 23, 2023 School of Engineering and Technology, University of Washington - Tacoms L17.52

51

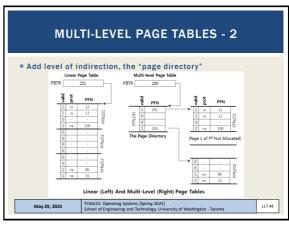

MULTI-LEVEL PAGE TABLES - 3

Advantages

Only allocates page table space in proportion to the address space actually used

Can easily grab next free page to expand page table

Disadvantages

Multi-level page tables are an example of a time-space tradeoff

Sacrifice address translation time (now 2-level) for space

Complexity: multi-level schemes are more complex

54

50

52

53

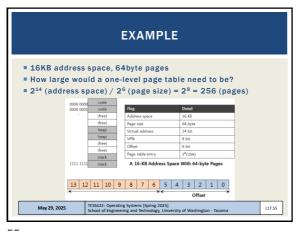

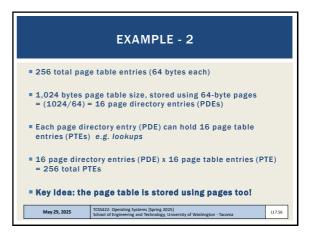

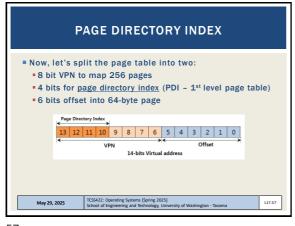

PAGE TABLE INDEX

# 4 bits page directory index (PDI - 1st level)

# 4 bits page table index (PTI - 2nd level)

# 7 page Directory Index Page Table Index (PTI - 2nd level)

# 13 12 11 10 9 8 7 6 5 4 3 2 1 0

# VPN Offset

# To dereference one 64-byte memory page,

# We need one page directory entry (PDE)

# One page table Index (PTI) - can address 16 pages

# TCSS422 Operating Systems [Spring 2025]

School of Engineering and Technology, University of Washington - Tacoma

58

57

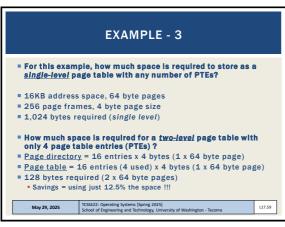

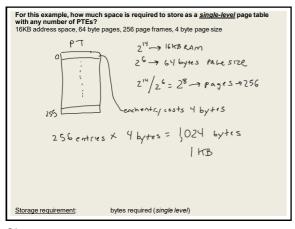

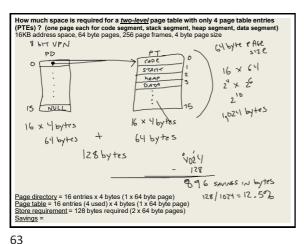

For this example, how much space is required to store as a <u>single-level</u> page table with any number of PTEs?

16KB address space, 64 byte pages, 256 page frames, 4 byte page size

Storage requirement: bytes required (single level)

59 60

61 62

64

65 66

71 72

**INVERTED PAGE TABLES** Keep a single page table for each physical page of memory Consider 4GB physical memory Using 4KB pages, page table requires 4MB to map all of RAM ■ Page table stores Which process uses each page Which process virtual page (from process virtual address space) maps to the physical page All processes share the same page table for memory mapping, kernel must isolate all use of the shared structure Finding process memory pages requires search of 220 pages Hash table: can index memory and speed lookups May 29, 2025 L17.76

76

**MULTI LEVEL PAGE TABLE EXAMPLE - 2** = (#5) How many bytes (or KB) are required for a single level page table? Let's assume a simple HelloWorld.c program. ■ HelloWorld.c requires virtual address translation for 4 pages: ■ 1 - code page 1 - stack page ■ 1 - heap page 1 - data segment page • (#6) Assuming a two-level page table scheme, how many bits are required for the Page Directory Index (PDI)? (#7) How many bits are required for the Page Table Index (PTI)? TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, University of Washington - Tacoma May 29, 2025 L17.78

77 78

Slides by Wes J. Lloyd

OBJECTIVES - 5/29

Questions from 5/27

Memory Segmentation Activity + answers (available in Canvas)

Assignment 2 - June 5 AOE

A3: (Tutorial) Intro to Linux Kernel Modules - June 10 AOE

Final exam - Thursday June 12 @ 3:40pm

Quiz 4 - Page Tables - Due June 8 AOE

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables, Multi-level Page Tables, N-level Page Tables

Chapter 21/22: Beyond Physical Memory

Swapping Mechanisms, Swapping Policies

May 29, 2025

TCSS422: Operating Systems (Spring 2025)

School of Ergineering and Technology, University of Washington - Tacoma

82

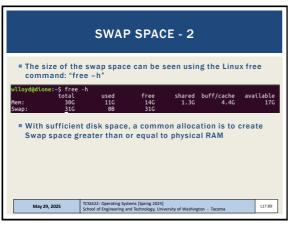

91

83

89 90

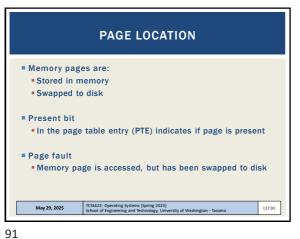

**PAGE FAULT** OS steps in to handle the page fault Loading page from disk requires a free memory page ■ Page-Fault Algorithm PFN = FindFreePhysicalPage() // no free page found if (PFN == -1) 3: PFN = EvictPage() // run replacement algorith // sleep (waiting for I/O) DiskRead(PTE.DiskAddr, pfn) 5: PTE.present = True // set PTE bit to present // reference new loaded page RetryInstruction() // retry instruction May 29, 2025 L17.92 rsity of Washington - Tacoma

92

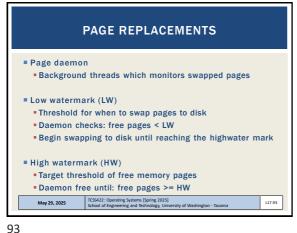

**OBJECTIVES - 5/29** ■ Questions from 5/27 Memory Segmentation Activity + answers (available in Canvas) Assignment 2 - June 5 AOE A3: (Tutorial) Intro to Linux Kernel Modules - June 10 A0E Final exam - Thursday June 12 @ 3:40pm Quiz 4 - Page Tables - Due June 8 AOE ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables Chapter 21/22: Beyond Physical Memory Swapping Mechanisms

Swapping Policies May 29, 2025 L17.94

94

**CACHE MANAGEMENT** Replacement policies apply to "any" cache Goal is to minimize the number of misses Average memory access time (AMAT) can be estimated:  $AMAT = (P_{Hit} * T_M) + (P_{Miss} * T_D)$ Meaning The cost of accessing memory (time) The cost of accessing disk (time) The probability of finding the data item in the cache(a hit) The probability of not finding the data in the cache(a miss Consider T<sub>M</sub> = 100 ns, T<sub>D</sub> = 10ms • Consider  $P_{hit}$  = .9 (90%),  $P_{miss}$  = .1 ■ Consider P<sub>hit</sub> = .999 (99.9%), P<sub>miss</sub> = .001 May 29, 2025 L17.96 rsity of Washington - Tacoma

95 96

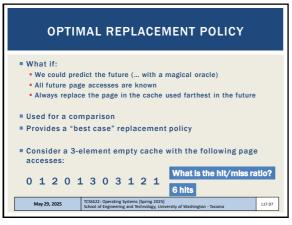

**FIFO REPLACEMENT**  Oueue based Always replace the oldest element at the back of cache ■ Simple to implement Doesn't consider importance... just arrival ordering Consider a 3-element empty cache with the following 0 1 2 0 1 3 0 3 1 2 1 4 hits ■ What is the hit/miss ratio? LRU inc How is FIFO different than LRU? L17.98

98

100

97

RANDOM REPLACEMENT Pick a page at random to replace Simple and fast implementation Performance depends on luck of random choices 0 1 2 0 1 3 0 3 1 2 1 May 29, 2025 L17.99

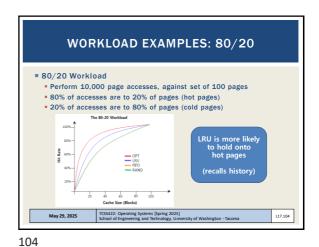

**HISTORY-BASED POLICIES** ■ LRU: Least recently used Always replace page with oldest access time (front) Always move end of cache when element is read again ■ LRU requires constant reorganization of the cache Considers temporal locality (when pg was last accessed) What is the hit/miss ratio? 0 1 2 0 1 3 0 3 1 2 1 6 hits ■ LFU: Least frequently used Always replace page with the fewest # of accesses (front) ■ Incorporates frequency of use - must track pg accesses Consider frequency of page accesses Hit/miss ratio is=6 hits 0 1 2 0 1 3 0 3 1 2 1 May 29, 2025 L17.100

99

Consider a 3-element cache. With a FIFO replacement policy, how many hits occur with the following page access sequence: 12013120213 2 hits 3 hits 4 hits 5 hits 6 hits TCSS422: Operating Systems [Spring 2025]

"Screduler Englisering and Testificitism" of Washington Pollmacemiare. L17.

Consider a 3-element cache. With an LRU replacement policy, how many hits occur with the following page access sequence: 12013120213 2 hits 3 hits 4 hits 5 hits 6 hits TCSS422: Operating Systems [Spring 2025]

May 29, 2035; the presentations expode the transparker in the presentations of the presentation of the presentation

102

Slides by Wes J. Lloyd

101

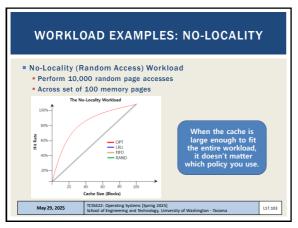

**WORKLOAD EXAMPLES: SEQUENTIAL** Looping sequential workload • Refer to 50 pages in sequence: 0, 1, ..., 49 Repeat loop Random performs better than FIFO and LRU for cache sizes < 50 Algorithms should provide May 29, 2025 L17.105

With small cache sizes, for the looping sequential workload, why do FIFO and LRU fail to provide cache hits? Memory accesses are unpredictable and too dom. Unpredictable accesses require a random cache replacement policy for cache hits Unlike Random cache replacement, both FIFO and LRU fail to speculate memory accesses in advance to improve caching

105

**IMPLEMENTING LRU** Implementing last recently used (LRU) requires tracking access time for all system memory pages ■ Times can be tracked with a list For cache eviction, we must scan an entire list Consider: 4GB memory system (232), with 4KB pages (212) ■ This requires 2<sup>20</sup> comparisons !!! ■ Simplification is needed Consider how to approximate the oldest page access TCSS422: Operating Systems (Spring 2025) School of Engineering and Technology, University of Washington - Tacoma May 29, 2025 L17.107

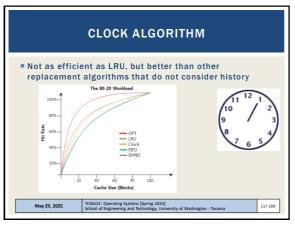

**IMPLEMENTING LRU-2** ■ Harness the Page Table Entry (PTE) Use Bit ■ HW sets to 1 when page is used OS sets to 0 ■ Clock algorithm (approximate LRU) Refer to pages in a circular list Clock hand points to current page Loops around • IF USE\_BIT=1 set to USE\_BIT = 0 • IF USE\_BIT=0 replace page TCSS422: Operating Systems (Spring 2025) School of Engineering and Technology, University of Washington - Tacoma May 29, 2025 L17.108

108

106

107

**CLOCK ALGORITHM - 2** Consider dirty pages in cache ■ If DIRTY (modified) bit is FALSE No cost to evict page from cache ■ If DIRTY (modified) bit is TRUE Cache eviction requires updating memory Contents have changed Clock algorithm should favor no cost eviction TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, University of Washington - Tacoma May 29, 2025 L17.110

110

112

114

109

WHEN TO LOAD PAGES ■ On demand → demand paging Prefetching Preload pages based on anticipated demand Prediction based on locality Access page P, suggest page P+1 may be used What other techniques might help anticipate required memory pages? Prediction models, historical analysis In general: accuracy vs. effort tradeoff High analysis techniques struggle to respond in real time May 29, 2025

OTHER SWAPPING POLICIES ■ Page swaps / writes Group/cluster pages together Collect pending writes, perform as batch Grouping disk writes helps amortize latency costs Occurs when system runs many memory intensive processes and is low in memory Everything is constantly swapped to-and-from disk May 29, 2025

111

**OTHER SWAPPING POLICIES - 2** Working sets Groups of related processes When thrashing: prevent one or more working set(s) from running Temporarily reduces memory burden Allows some processes to run, reduces thrashing May 29, 2025 L17.113 113

QUESTIONS

Slides by Wes J. Lloyd