|  | Questi                | on 1       |          |         |                         |           |           |          |         | 0.5 pts                   |   |

|--|-----------------------|------------|----------|---------|-------------------------|-----------|-----------|----------|---------|---------------------------|---|

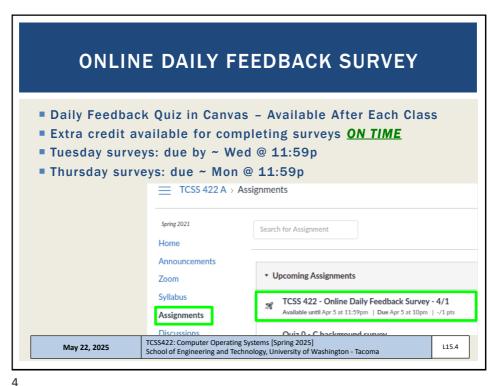

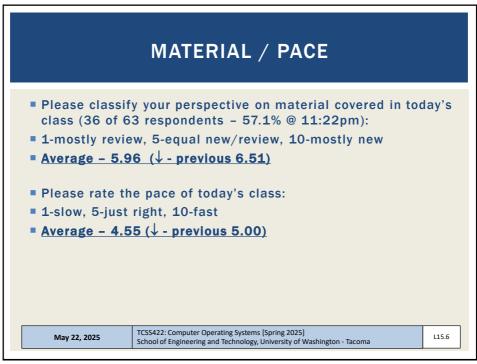

|  | -                     |            | to 10, j | please  | lassify yo              | our persp | pective o | on mater | ial cov | vered in today's          | 1 |

|  | class:                | _          |          |         |                         |           |           |          | _       |                           |   |

|  | 1<br>Mostly<br>Review | 2<br>To Me | 3        | 4       | 5<br>Equal<br>ew and Re | 6         | 7         | 8        | 9       | 10<br>Mostly<br>New to Me |   |

|  |                       |            |          |         |                         |           |           |          |         |                           |   |

|  |                       |            |          |         |                         |           |           |          |         |                           |   |

|  |                       |            |          |         |                         |           |           |          |         |                           | _ |

|  | Questi                | on 2       |          |         |                         |           |           |          |         | 0.5 pts                   | _ |

|  | Please I              | rate the   | pace of  | today's | class:                  |           |           |          |         |                           |   |

|  | 1<br>Slow             | 2          | 3        | 4       | 5<br>Just Right         | 6         | 7         | 8        | 9       | 10<br>Fast                |   |

|  |                       |            |          |         |                         |           |           |          |         |                           |   |

| <br>FEEDBACK FROM 5/20                   |       |

|------------------------------------------|-------|

|                                          |       |

|                                          |       |

|                                          |       |

|                                          |       |

|                                          |       |

|                                          |       |

|                                          |       |

| TCSS422: Operating Systems [Spring 2025] |       |

|                                          | L15.7 |

ſ

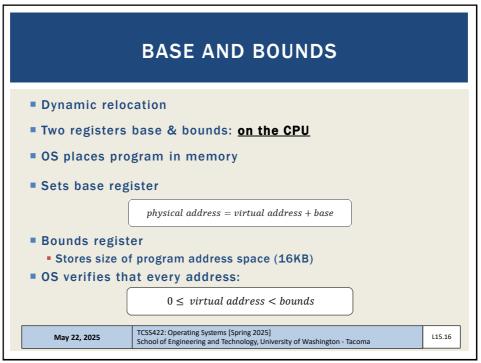

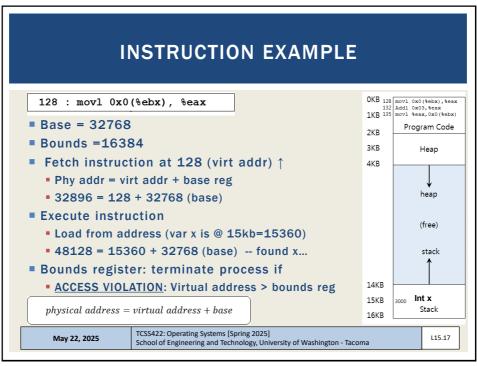

| DYNAMIC RELOCATION OF PROGRAMS                                                             |                                                   |                                                                             |  |  |  |  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Hardware requ                                                                              | irements:                                         |                                                                             |  |  |  |  |

| Requirements                                                                               |                                                   | HW support                                                                  |  |  |  |  |

| Privileged mode                                                                            |                                                   | CPU modes: kernel, user                                                     |  |  |  |  |

| Base / bounds registers                                                                    |                                                   | Registers to support address translation                                    |  |  |  |  |

| Translate virtual addr; check if in bounds                                                 |                                                   | Translation circuitry, check limits                                         |  |  |  |  |

| Privileged instruction(s) to<br>update base / bounds regs                                  |                                                   | Instructions for modifying base/bound registers                             |  |  |  |  |

| Privileged instruction(s)<br>to register exception handlers<br>Ability to raise exceptions |                                                   | Set code pointers to OS code to handle faults                               |  |  |  |  |

|                                                                                            |                                                   | For out-of-bounds memory access, or<br>attempts to access privileged instr. |  |  |  |  |

| May 22, 2025                                                                               | TCSS422: Operating Sys<br>School of Engineering a | stems [Spring 2025]<br>Ind Technology, University of Washington - Tacoma    |  |  |  |  |

|                                                           | SEGMENT REGISTERS                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                              |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|

| <ul> <li>First two bits</li> <li>Remaining bit</li> </ul> | erence memory during translation         13       12       11       10       9       8       7       6       5       4       3       2       1       0         13       12       11       10       9       8       7       6       5       4       3       2       1       0         Segment       Offset         Gegment type         identify memory offset         Jal heap address 4200 (010000011 | 01000)                                |                              |

| 13 12 11 1                                                |                                                                                                                                                                                                                                                                                                                                                                                                        | Segment<br>Code<br>Heap<br>Stack<br>- | bits<br>00<br>01<br>10<br>11 |

| I              | MEMORY HEADERS - 3                                                                                                  |        |

|----------------|---------------------------------------------------------------------------------------------------------------------|--------|

| N bytes + size | user malloc size                                                                                                    |        |

|                | <pre>tee (void *ptr) {     header_t *hptr = (void *)ptr - sizeof(header_t);    </pre>                               |        |

| May 22, 2025   | TCSS422: Operating Systems [Spring 2025]<br>School of Engineering and Technology, University of Washington - Tacoma | L15.55 |

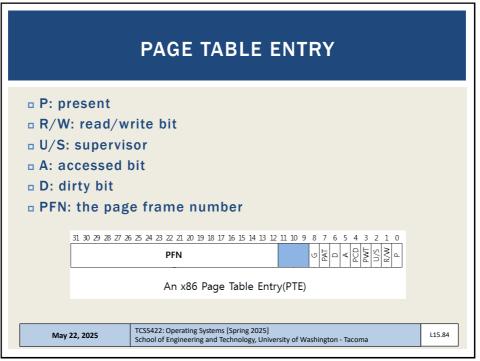

| PAGE TABLE ENTRY - 2                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Common flags:                                                                                                                                           |

| Valid Bit: Indicating whether the particular translation is valid.                                                                                      |

| Protection Bit: Indicating whether the page could be read<br>from, written to, or executed from                                                         |

| Present Bit: Indicating whether this page is in physical memory or on disk(swapped out)                                                                 |

| Dirty Bit: Indicating whether the page has been modified since<br>it was brought into memory                                                            |

| Reference Bit(Accessed Bit): Indicating that a page has been                                                                                            |

| accessed                                                                                                                                                |

| May 22, 2025         TCSS422: Operating Systems [Spring 2025]<br>School of Engineering and Technology, University of Washington - Tacoma         L15.85 |

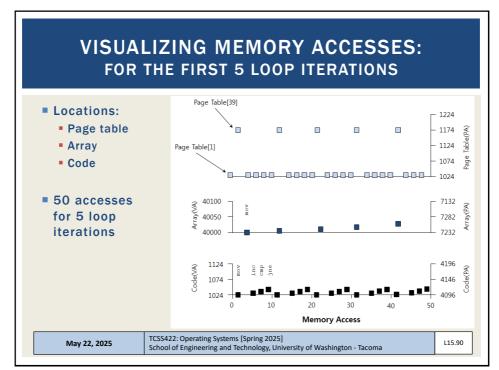

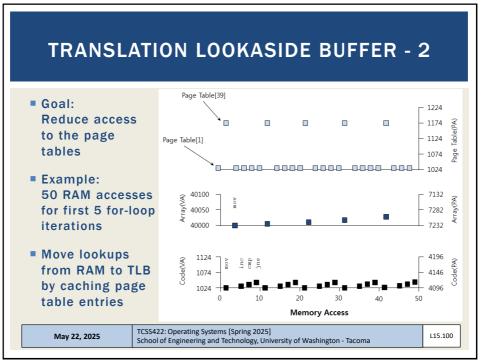

| COU                                                    | NTING MEMORY ACCESSES                                                                                 |  |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

| Example: Use                                           | e this Array initialization Code                                                                      |  |

| int array                                              | [1000];                                                                                               |  |

|                                                        | ); i < 1000; i++)                                                                                     |  |

|                                                        | rray[i] = 0;                                                                                          |  |

| <ul> <li>Assembly eq</li> </ul>                        | <pre>rray[i] = 0;<br/>uivalent:</pre>                                                                 |  |

| Assembly eq<br>0x1024 more                             | <pre>rray[i] = 0;<br/>uivalent:<br/>/1 \$0x0, (%edi, %eax, 4)</pre>                                   |  |

| Assembly eq     Ox1024 mor     Ox1028 in     Ox102c cm | <pre>rray[i] = 0;<br/>uivalent:<br/>/1 \$0x0, (%edi, %eax, 4)<br/>/1 %eax<br/>bl \$0x03e8, %eax</pre> |  |

| Assembly eq<br>0x1024 mo<br>0x1028 in                  | <pre>rray[i] = 0;<br/>uivalent:<br/>/1 \$0x0, (%edi, %eax, 4)<br/>/1 %eax<br/>bl \$0x03e8, %eax</pre> |  |

| Assembly eq     Ox1024 mor     Ox1028 in     Ox102c cm | <pre>rray[i] = 0;<br/>uivalent:<br/>/1 \$0x0, (%edi, %eax, 4)<br/>/1 %eax<br/>bl \$0x03e8, %eax</pre> |  |

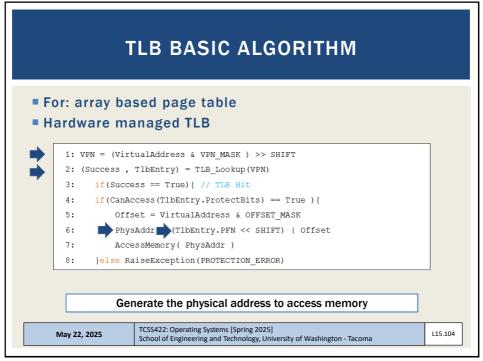

| <pre>11: else{ //TLB Miss 12: PTEAddr = PTBR + (VPN * sizeof(PTE)) 13: PTE = AccessMemory(PTEAddr) 14: () // Check for, and raise exceptions 15: 16: TLB_Insert( VPN , PTE.PFN , PTE.ProtectBits) 17: RetryInstruction()</pre> |               | TLB BASIC ALGORITHM - 2                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------|

| <pre>12: PTEAddr = PTBR + (VPN * sizeof(PTE)) 13: PTE = AccessMemory(PTEAddr) 14: () // Check for, and raise exceptions 15: 16: TLB_Insert(VPN, PTE.PFN, PTE.ProtectBits)</pre>                                                |               |                                                                                                                     |

| <pre>12: PTEAddr = PTBR + (VPN * sizeof(PTE)) 13: PTE = AccessMemory(PTEAddr) 14: () // Check for, and raise exceptions 15: 16: TLB_Insert( VPN , PTE.PFN , PTE.ProtectBits)</pre>                                             |               |                                                                                                                     |

| <pre>13: PTE = AccessMemory(PTEAddr) 14: () // Check for, and raise exceptions 15: 16: TLB_Insert( VPN , PTE.PFN , PTE.ProtectBits)</pre>                                                                                      | 11:           | else{ //TLB Miss                                                                                                    |

| <pre>14: () // Check for, and raise exceptions 15: 16: TLB_Insert( VPN , PTE.PFN , PTE.ProtectBits)</pre>                                                                                                                      | 12:           | <pre>PTEAddr = PTBR + (VPN * sizeof(PTE))</pre>                                                                     |

| 15:<br>16: TLB_Insert(VPN, PTE.PFN, PTE.ProtectBits)                                                                                                                                                                           | 13:           | PTE = AccessMemory(PTEAddr)                                                                                         |

| 16: TLB_Insert( VPN , PTE.PFN , PTE.ProtectBits)                                                                                                                                                                               | 14:           | () // Check for, and raise exceptions                                                                               |

|                                                                                                                                                                                                                                | 15:           |                                                                                                                     |

| 17: RetryInstruction()                                                                                                                                                                                                         | 16:           | TLB_Insert( VPN , PTE.PFN , PTE.ProtectBits)                                                                        |

|                                                                                                                                                                                                                                | 17:           | RetryInstruction()                                                                                                  |

| 18: }                                                                                                                                                                                                                          | 18:           | )                                                                                                                   |

| 19:}                                                                                                                                                                                                                           | 19:}          |                                                                                                                     |

|                                                                                                                                                                                                                                |               | Retry the instruction (requery the TLB)                                                                             |

| Retry the instruction (requery the TLB)                                                                                                                                                                                        | /lay 22, 2025 | TCSS422: Operating Systems [Spring 2025]<br>School of Engineering and Technology, University of Washington - Tacoma |

106

| TLB EXAMPLE - 4                                 |                                                                                 |                              |                      |      |      |       |     |  |

|-------------------------------------------------|---------------------------------------------------------------------------------|------------------------------|----------------------|------|------|-------|-----|--|

| 0:                                              | int sum = 0 ;                                                                   |                              |                      | 00 0 | OF   | SET   | 1   |  |

| 1:                                              | <pre>for( i=0; i&lt;10; i++) {</pre>                                            |                              | VPN = 00             |      | 4 00 |       |     |  |

| 2:                                              | <pre>sum+=a[i];</pre>                                                           |                              | VPN = 01             |      |      |       |     |  |

| 3:                                              | }                                                                               |                              | VPN = 03             |      |      |       |     |  |

| Ļ                                               |                                                                                 | _                            | VPN = 04             |      |      |       |     |  |

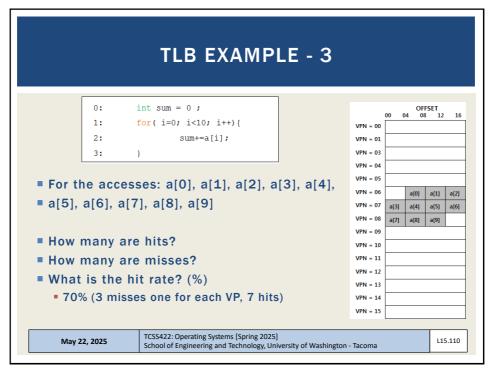

| What factors affect the hit/miss rate?          |                                                                                 |                              | VPN = 05             | i    |      |       |     |  |

|                                                 |                                                                                 |                              |                      |      | a[0] | a[1]  | a[2 |  |

| Page size                                       |                                                                                 |                              | VPN = 07             | a[3] | a[4] | a[5]  | a[6 |  |

| Data/Acces                                      | s locality (how is data                                                         | accessed?)                   | VPN = 08             | a[7] | a[8] | a[9]  |     |  |

| 1                                               | · · · · · · · · · · · · · · · · · · ·                                           |                              | VPN = 09             |      |      |       |     |  |

| Sequential array access vs. random array access |                                                                                 |                              | VPN = 10<br>VPN = 11 |      |      |       |     |  |

| Temporal locality                               |                                                                                 | VPN = 12                     |                      |      |      |       |     |  |

| Size of the 1                                   | [] B cache                                                                      |                              | VPN = 13             |      |      |       |     |  |

| (how much history can you store?)               |                                                                                 |                              | VPN = 14             |      |      |       |     |  |

|                                                 | story can you store?)                                                           |                              | VPN = 15             |      |      |       |     |  |

|                                                 |                                                                                 |                              |                      |      |      |       |     |  |

| May 22, 2025                                    | TCSS422: Operating Systems [Spring 20.<br>School of Engineering and Technology, |                              | acoma                |      |      | L15.1 | 11  |  |

|                                                 | 1 School of Engineering and rechnology,                                         | Shiversity of Washington - I | aconna               |      |      |       |     |  |