Τ

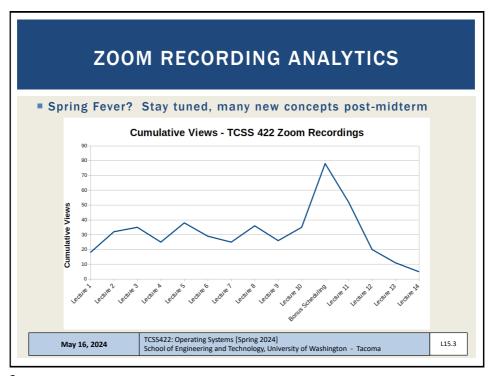

# MATERIAL / PACE ■ Please classify your perspective on material covered in today's class (26 respondents): ■ 1-mostly review, 5-equal new/review, 10-mostly new ■ Average - 5.96 (↓ - previous 6.68) ■ Please rate the pace of today's class: ■ 1-slow, 5-just right, 10-fast ■ Average - 5.42 (↑ - previous 5.28) May 16, 2024 TCSS422: Computer Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

7

### **OBJECTIVES - 5/16**

- Questions from 5/14

- Assignment 2 May 31

- Quiz 3 Synchronized Array May 23

- Tutorial 2 Pthread, locks, conditions tutorial -Fri May 24

- Assignment 3 (as a Tutorial) to be posted...

- Chapter 16: Segmentation

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

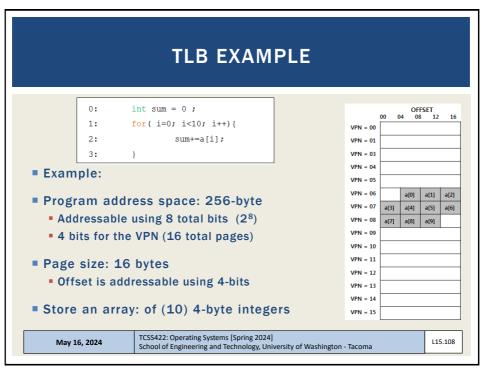

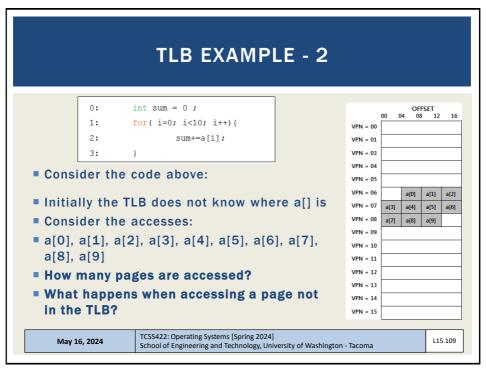

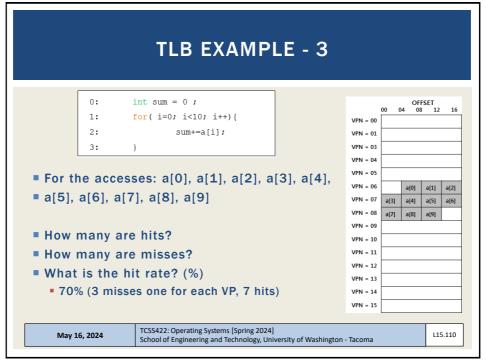

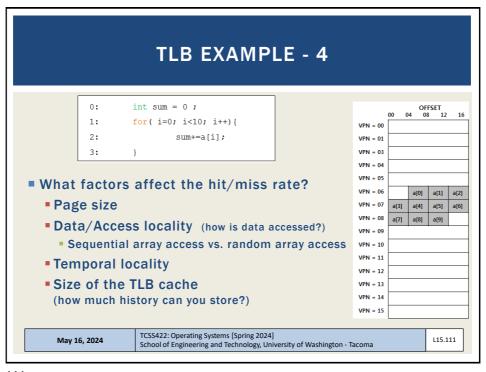

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Hit-to-Miss Ratios

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

May 16, 2024

TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

### **OBJECTIVES - 5/16**

- Questions from 5/14

- Assignment 2 May 31

- Quiz 3 Synchronized Array May 23

- Tutorial 2 Pthread, locks, conditions tutorial -Fri May 24

- Assignment 3 (as a Tutorial) to be posted...

- Chapter 16: Segmentation

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Hit-to-Miss Ratios

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

May 16, 2024

TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

L15.10

### **OBJECTIVES - 5/16**

- Questions from 5/14

- Assignment 2 May 31

- Quiz 3 Synchronized Array May 23

- Tutorial 2 Pthread, locks, conditions tutorial -Fri May 24

- Assignment 3 (as a Tutorial) to be posted...

- Chapter 16: Segmentation

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Hit-to-Miss Ratios

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

May 16, 2024

TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

11

### **OBJECTIVES - 5/16**

- Questions from 5/14

- Assignment 2 May 31

- Quiz 3 Synchronized Array May 23

- Tutorial 2 Pthread, locks, conditions tutorial -Fri May 24

- Assignment 3 (as a Tutorial) to be posted...

- Chapter 16: Segmentation

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Hit-to-Miss Ratios

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

May 16, 2024

TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

L15.12

### **OBJECTIVES - 5/16** Questions from 5/14 Assignment 2 - May 31 Quiz 3 - Synchronized Array - May 23 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... Chapter 16: Segmentation ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma May 16, 2024 L15.26

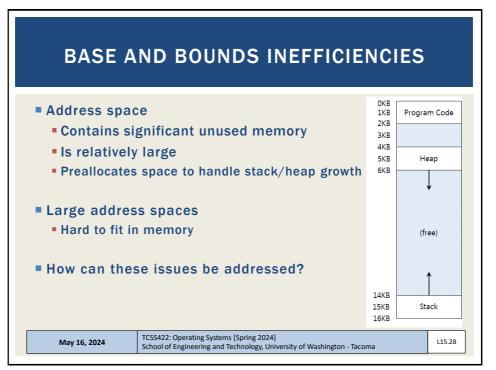

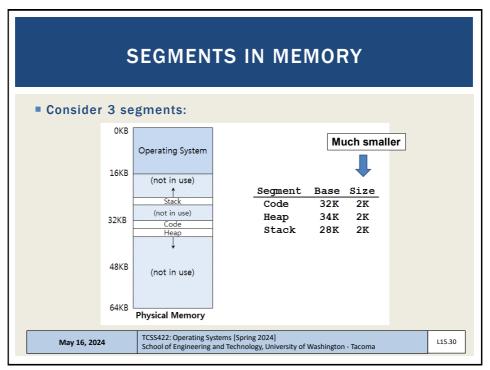

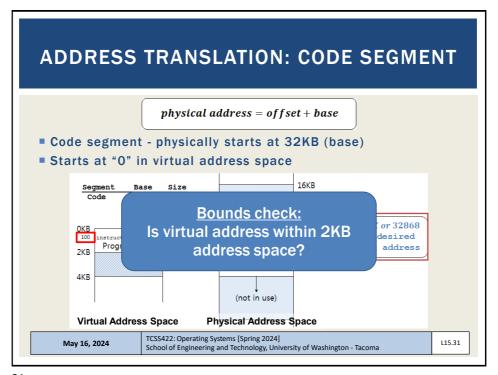

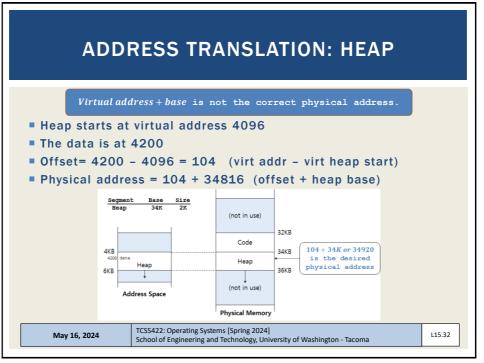

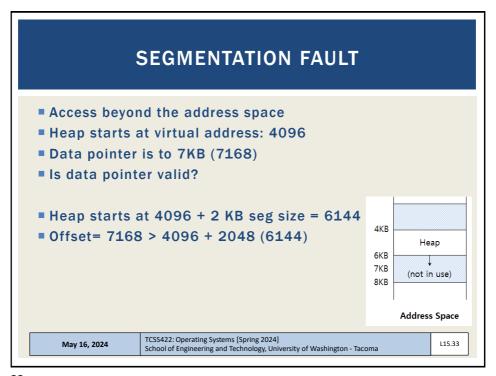

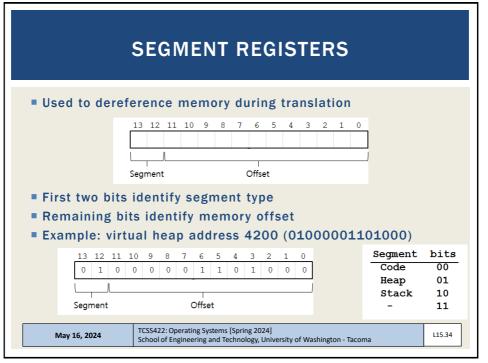

## MULTIPLE SEGMENTS Memory segmentation Manage the address space as (3) separate segments Each is a contiguous address space Provides logically separate segments for: code, stack, heap Each segment can placed separately Track base and bounds for each segment (registers)

29

```

SEGMENTATION DEREFERENCE

// get top 2 bits of 14-bit VA

Segment = (VirtualAddress & SEG_MASK) >> SEG_SHIFT

// now get offset

Offset = VirtualAddress & OFFSET MASK

if (Offset >= Bounds[Segment])

RaiseException(PROTECTION_FAULT)

PhysAddr = Base[Segment] + Offset

Register = AccessMemory(PhysAddr)

VIRTUAL ADDRESS = 01000001101000

(on heap)

SEG_MASK = 0x3000 (1100000000000)

■ SEG_SHIFT = 01 → heap

(mask gives us segment code)

OFFSET_MASK = 0xFFF (00111111111111)

• OFFSET = 000001101000 = 104

(isolates segment offset)

■ OFFSET < BOUNDS: 104 < 2048

TCSS422: Operating Systems [Spring 2024]

L15.35

May 16, 2024

School of Engineering and Technology, University of Washington - Tacoma

```

### OBJECTIVES - 5/16

- Questions from 5/14

- Assignment 2 May 31

- Quiz 3 Synchronized Array May 23

- Tutorial 2 Pthread, locks, conditions tutorial -Fri May 24

- Assignment 3 (as a Tutorial) to be posted...

- Chapter 16: Segmentation

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Hit-to-Miss Ratios

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

May 16, 2024

TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

L15.43

43

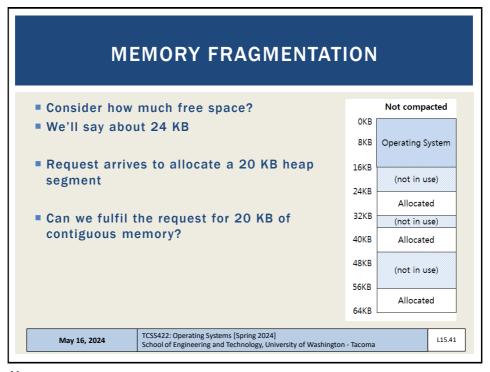

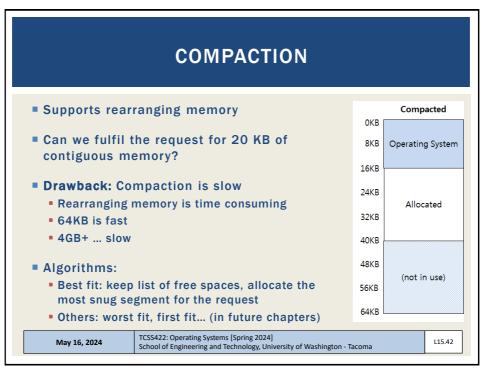

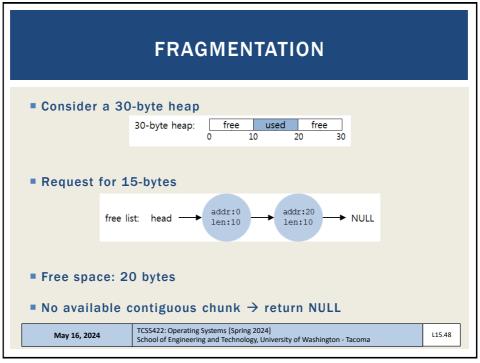

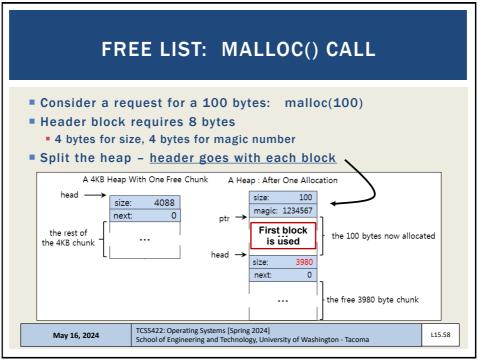

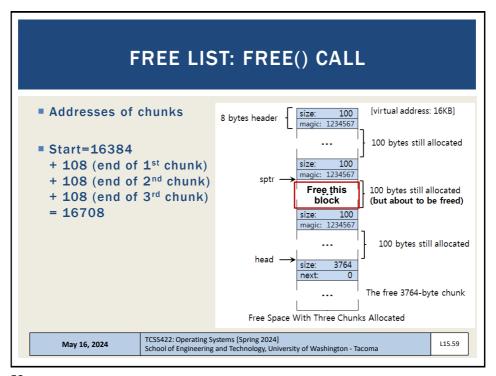

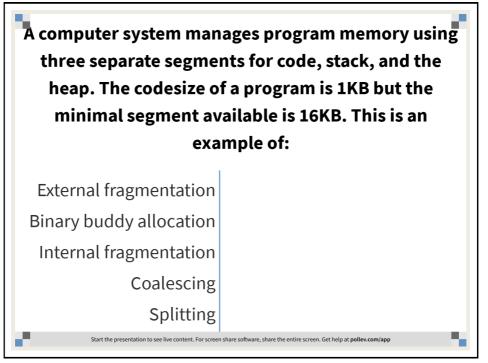

### FRAGMENTATION - 2 External: OS can compact Example: Client asks for 100 bytes: malloc(100) OS: No 100 byte contiguous chunk is available: returns NULL Memory is externally fragmented - - Compaction can fix! Internal: lost space - OS can't compact OS returns memory units that are too large Example: Client asks for 100 bytes: malloc(100) OS: Returns 125 byte chunk Fragmentation is \*in\* the allocated chunk Memory is lost, and unaccounted for - can't compact May 16, 2024 TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

49

```

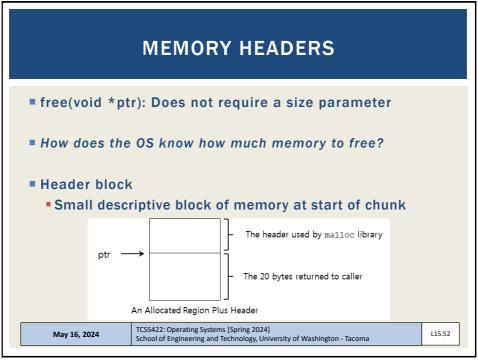

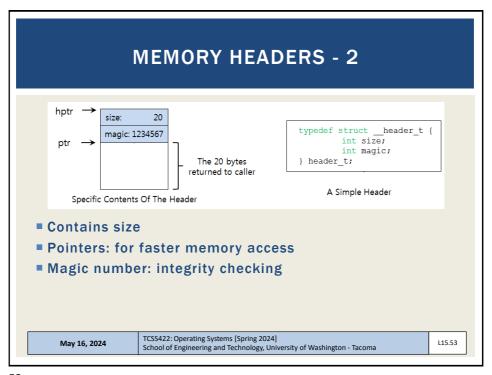

MEMORY HEADERS - 3

Size of memory chunk is:

Header size + user malloc size

N bytes + sizeof(header)

Easy to determine address of header

void free (void *ptr) {

header_t *hptr = (void *)ptr - sizeof(header_t);

}

May 16, 2024

TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma

```

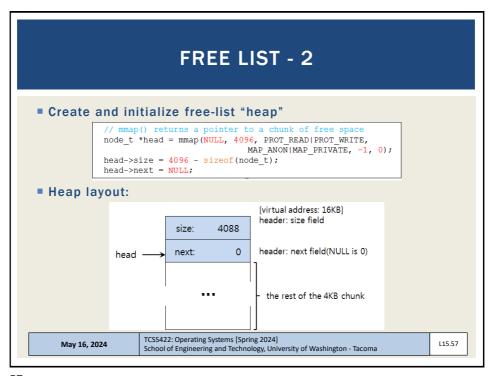

```

THE FREE LIST

■ Simple free list struct

typedef struct __node_t {

int size;

struct __node_t *next;

} nodet t;

Use mmap to create free list

4kb heap, 4 byte header, one contiguous free chunk

// mmap() returns a pointer to a chunk of free space

node_t *head = mmap(NULL, 4096, PROT_READ|PROT_WRITE,

MAP_ANON|MAP_PRIVATE, -1, 0);

head->size = 4096 - sizeof(node_t);

head->next = NULL;

TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma

May 16, 2024

L15.56

```

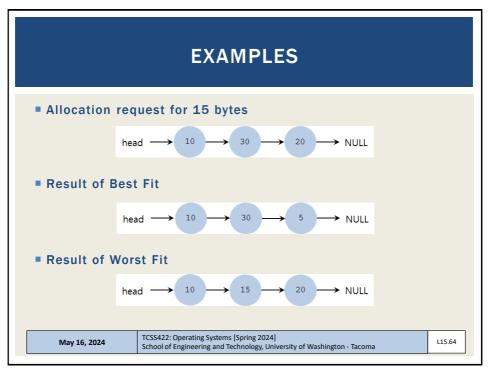

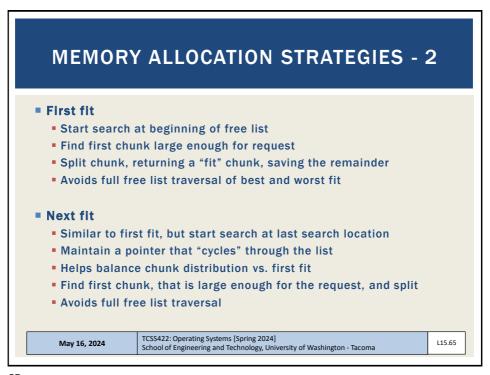

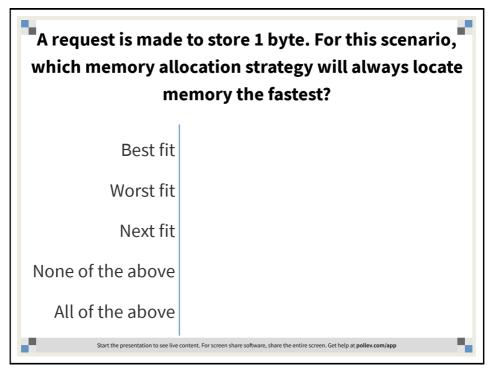

## MEMORY ALLOCATION STRATEGIES Best fit Traverse free list Identify all candidate free chunks Note which is smallest (has best fit) When splitting, "leftover" pieces are small (and potentially less useful -- fragmented) Worst fit Traverse free list Identify largest free chunk Split largest free chunk, leaving a still large free chunk TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

63

## SEGREGATED LISTS For popular sized requests e.g. for kernel objects such as locks, inodes, etc. Manage as segregated free lists Provide object caches: stores pre-initialized objects How much memory should be dedicated for specialized requests (object caches)? If a given cache is low in memory, can request "slabs" of memory from the general allocator for caches. General allocator will reclaim slabs when not used TCSS422: Operating Systems (Spring 2024) School of Engineering and Technology, University of Washington - Tacoma

67

### **OBJECTIVES - 5/16** Questions from 5/14 Assignment 2 - May 31 Quiz 3 - Synchronized Array - May 23 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 16: Segmentation ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma May 16, 2024 L15.72

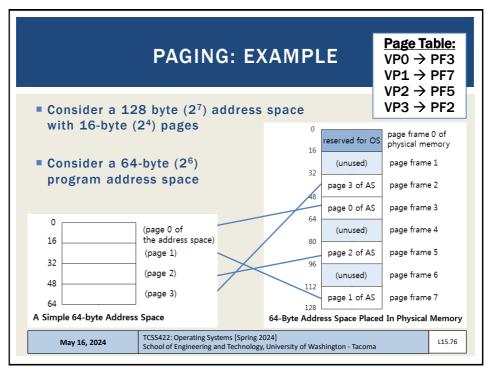

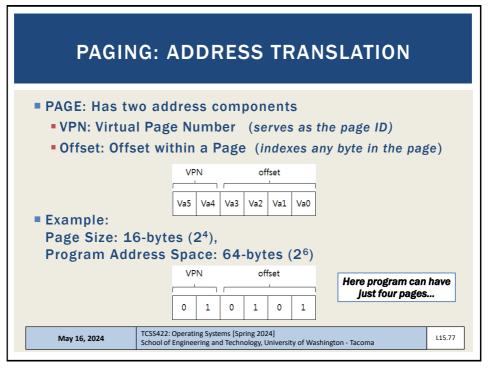

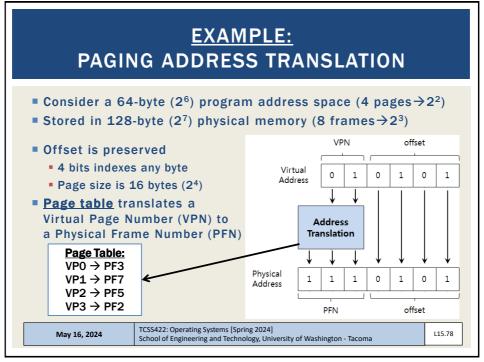

# PAGING Split up address space of process into fixed sized pieces called pages Alternative to variable sized pieces (Segmentation) which suffers from significant fragmentation Physical memory is split up into an array of fixed-size slots called page frames. Each process has a page table which translates virtual addresses to physical addresses TCSS42: Operating Systems (Spring 2024) School of Engineering and Technology, University of Washington - Tacoma

### ADVANTAGES OF PAGING Flexibility Abstracts the process address space into pages No need to track direction of HEAP / STACK growth Just add more pages... No need to store unused space As with segments... Simplicity Pages and page frames are the same size Easy to allocate and keep a free list of pages May 16, 2024 TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

75

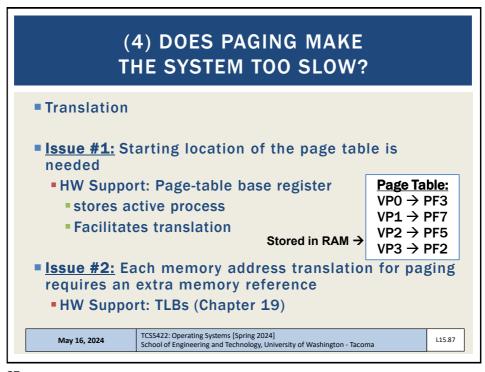

### PAGING DESIGN QUESTIONS

- (1) Where are page tables stored?

- (2) What are the typical contents of the page table?

- (3) How big are page tables?

- (4) Does paging make the system too slow?

May 16, 2024

TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma

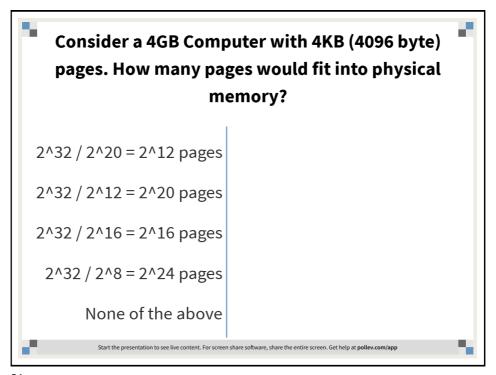

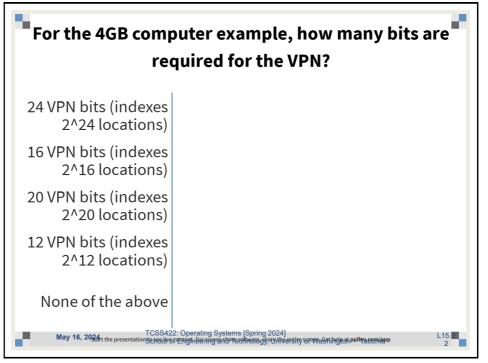

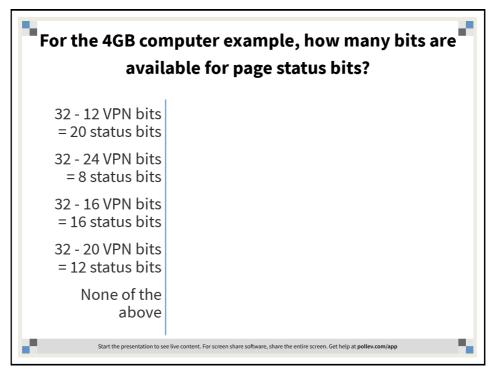

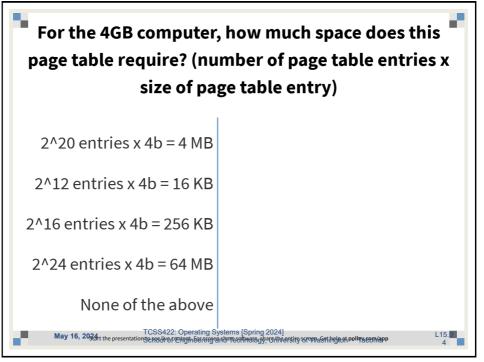

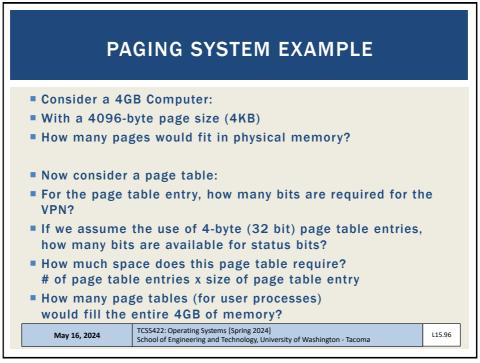

### (1) WHERE ARE PAGE TABLES STORED?

- **Example:**

- Consider a 32-bit process address space (4GB=2<sup>32</sup> bytes)

- With 4 KB pages (4KB=2<sup>12</sup> bytes)

- 20 bits for VPN (2<sup>20</sup> pages)

- 12 bits for the page offset (2<sup>12</sup> unique bytes in a page)

- Page tables for each process are stored in RAM

- Support potential storage of 2<sup>20</sup> translations

- **= 1,048,576 pages per process**

- Each page has a page table entry size of 4 bytes

May 16, 2024

TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma

80

L15.80

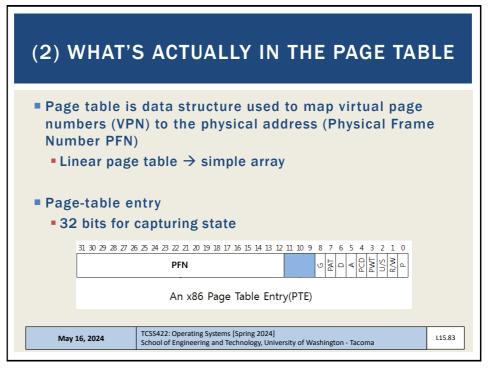

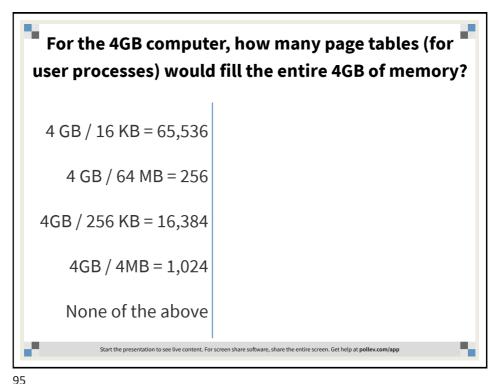

### PAGE TABLE EXAMPLE With 2<sup>20</sup> slots in our page table for a single process Each slot (i.e. entry) dereferences a VPN VPN<sub>o</sub> Each entry provides a physical frame number VPN<sub>1</sub> $VPN_2$ Each entry requires 4 bytes (32 bits) 20 for the PFN on a 4GB system with 4KB pages 12 for the offset which is preserved ... • (note we have no status bits, so this is VPN<sub>1048576</sub> unrealistically small) How much memory is required to store the page table for 1 process? Hint: # of entries x space per entry 4,194,304 bytes (or 4MB) to index one process TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma May 16, 2024

81

# NOW FOR AN ENTIRE OS If 4 MB is required to store one process Consider how much memory is required for an entire OS? With for example 100 processes... Page table memory requirement is now 4MB x 100 = 400MB If computer has 4GB memory (maximum for 32-bits), the page table consumes 10% of memory 400 MB / 4000 GB Is this efficient? May 16, 2024 TCSS422: Operating Systems (Spring 2024) School of Engineering and Technology, University of Washington - Tacoma

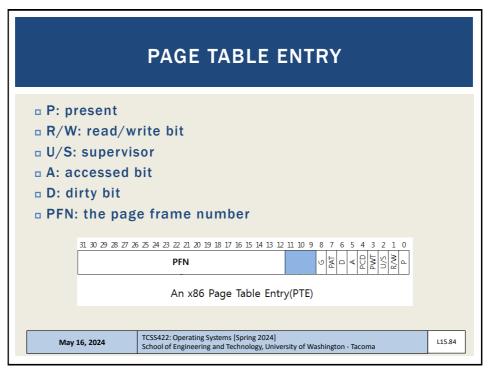

### **PAGE TABLE ENTRY - 2**

- Common flags:

- Valid Bit: Indicating whether the particular translation is valid.

- Protection Bit: Indicating whether the page could be read from, written to, or executed from

- Present Bit: Indicating whether this page is in physical memory or on disk(swapped out)

- Dirty Bit: Indicating whether the page has been modified since it was brought into memory

- Reference Bit(Accessed Bit): Indicating that a page has been accessed

TCSS422: Operating Systems [Spring 2024] May 16, 2024 L15.85 School of Engineering and Technology, University of Washington - Tacoma

85

### (3) HOW BIG ARE PAGE TABLES?

- Page tables are too big to store on the CPU

- Page tables are stored using physical memory

- Paging supports efficiently storing a sparsely populated address space

- Reduced memory requirement Compared to base and bounds, and segments

May 16, 2024

TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma

86

115.86

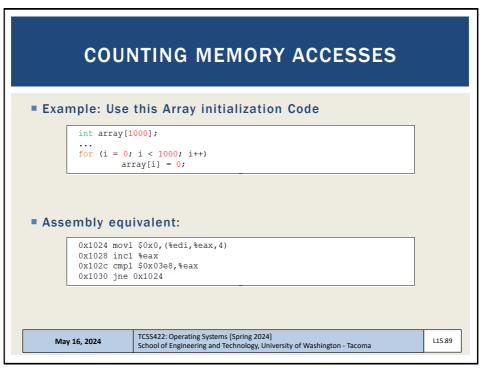

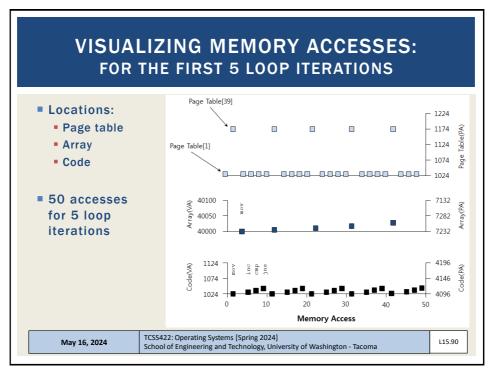

```

PAGING MEMORY ACCESS

// Extract the VPN from the virtual address

VPN = (VirtualAddress & VPN_MASK) >> SHIFT

// Form the address of the page-table entry (PTE)

PTEAddr = PTBR + (VPN * sizeof(PTE))

// Fetch the PTE

PTE = AccessMemory(PTEAddr)

8.

// Check if process can access the page

10.

11.

if (PTE.Valid == False)

RaiseException(SEGMENTATION_FAULT)

12.

13.

else if (CanAccess(PTE.ProtectBits) == False)

14.

RaiseException(PROTECTION_FAULT)

15.

else

16.

// Access is OK: form physical address and fetch it

17.

offset = VirtualAddress & OFFSET_MASK

18.

PhysAddr = (PTE.PFN << PFN_SHIFT) | offset

19.

Register = AccessMemory(PhysAddr)

TCSS422: Operating Systems [Spring 2024]

May 16, 2024

115.88

School of Engineering and Technology, University of Washington - Tacoma

```

### OBJECTIVES - 5/16

- Questions from 5/14

- Assignment 2 May 31

- Quiz 3 Synchronized Array May 23

- Tutorial 2 Pthread, locks, conditions tutorial -Fri May 24

- Assignment 3 (as a Tutorial) to be posted...

- Chapter 16: Segmentation

- Chapter 17: Free Space Management

- Chapter 18: Introduction to Paging

- Chapter 19: Translation Lookaside Buffer (TLB)

- TLB Algorithm, Hit-to-Miss Ratios

- Chapter 20: Paging: Smaller Tables

- Smaller Tables, Multi-level Page Tables, N-level Page Tables

May 16, 2024

TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

L15.97

97

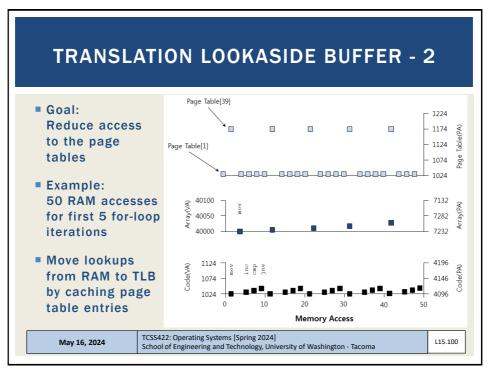

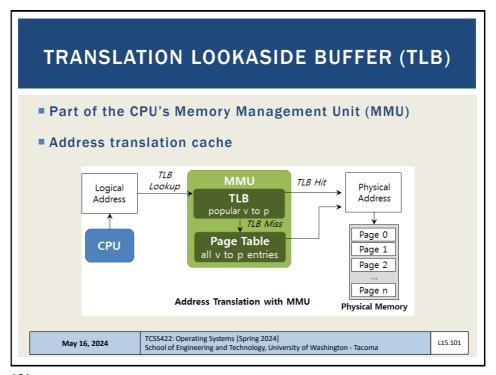

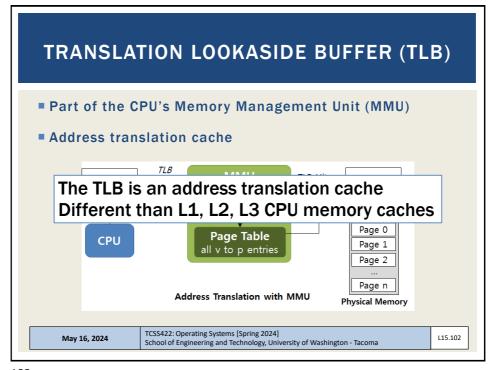

# TRANSLATION LOOKASIDE BUFFER ■ Legacy name... ■ Better name, "Address Translation Cache" ■ TLB is an on CPU cache of address translations ■ virtual → physical memory | TCSS422: Operating Systems [Spring 2024] | School of Engineering and Technology, University of Washington - Tacoma

99

### OBJECTIVES - 5/16 Questions from 5/14 Assignment 2 - May 31 Quiz 3 - Synchronized Array - May 23 Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... Chapter 16: Segmentation Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables. Multi-level Page Tables. N-level Page Tables May 16, 2024 CCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

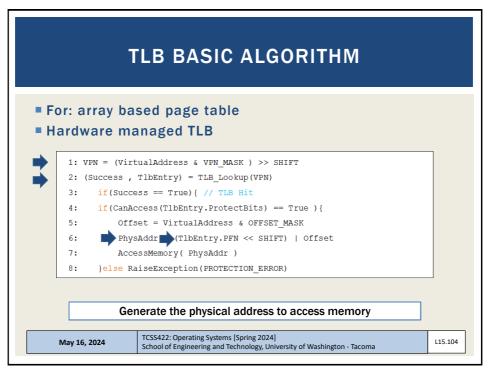

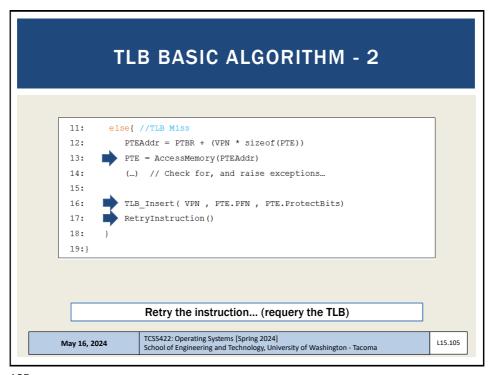

103

### OBJECTIVES - 5/16 Questions from 5/14 Assignment 2 - May 31 Quiz 3 - Synchronized Array - May 23 Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... Chapter 16: Segmentation Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios

Smaller Tables, Multi-level Page Tables, N-level Page Tables

School of Engineering and Technology, University of Washington - Tacoma

TCSS422: Operating Systems [Spring 2024]

Chapter 20: Paging: Smaller Tables

107

May 16, 2024

### **OBJECTIVES - 5/16** Questions from 5/14 Assignment 2 - May 31 Quiz 3 - Synchronized Array - May 23 Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... Chapter 16: Segmentation ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables, Multi-level Page Tables, N-level Page Tables TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma May 16, 2024 L15.112