L

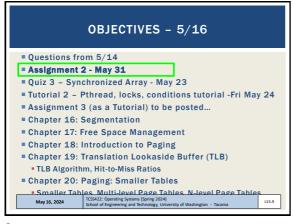

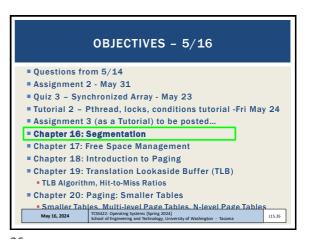

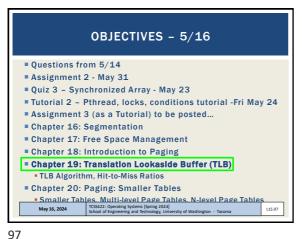

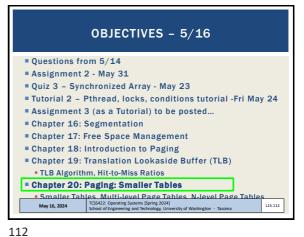

OBJECTIVES - 5/16

Questions from 5/14

Assignment 2 - May 31

Quiz 3 - Synchronized Array - May 23

Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24

Assignment 3 (as a Tutorial) to be posted...

Chapter 16: Segmentation

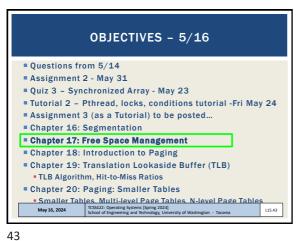

Chapter 17: Free Space Management

Chapter 18: Introduction to Paging

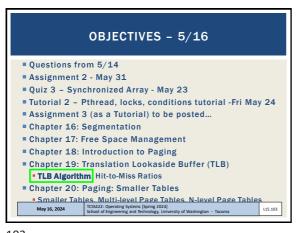

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm, Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables Multi-level Page Tables N-level Page Tables

Smaller Tables Multi-level Page Tables N-level Page Tables

Smaller Tables Multi-level Page Tables N-level Page Tables

3

5

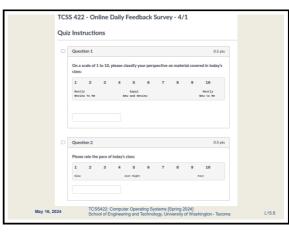

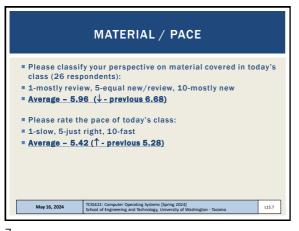

FEEDBACK FROM 5/14 May 16, 2024 L15.8

**OBJECTIVES - 5/16** ■ Questions from 5/14 Assignment 2 - May 31 Quiz 3 – Synchronized Array - May 23 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 16: Segmentation Chapter 17: Free Space Management Chapter 18: Introduction to Paging ■ Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables Multi-level Page Tables N-level Page Tabl May 16, 2024 L15.10

10

12

9

**OBJECTIVES - 5/16** Questions from 5/14 Assignment 2 - May 31 Quiz 3 - Synchronized Array - May 23 Tutorial 2 – Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 16: Segmentation ■ Chapter 17: Free Space Management ■ Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables Multi-level Page Tables N-level Page Table May 16, 2024 TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma L15.11 11

**OBJECTIVES - 5/16** ■ Questions from 5/14 Assignment 2 - May 31 Quiz 3 - Synchronized Array - May 23 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... Chapter 16: Segmentation ■ Chapter 17: Free Space Management Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables Multi-level Page Tables N-level Page Table May 16, 2024 TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma L15.12

.5

17 18

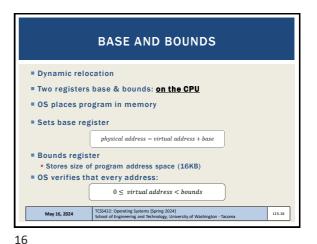

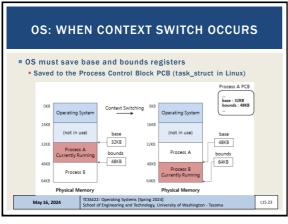

**DYNAMIC RELOCATION** OS can move process data when not running 1. OS un-schedules process from scheduler 2. OS copies address space from current to new location 3. OS updates PCB (base and bounds registers) 4. OS reschedules process When process runs new base register is restored to CPU Process doesn't know it was even moved! TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma May 16, 2024 L15.24

23 24

21

29 30

34 33

35 36

Consider a program with 2KB of code, a 1 KB stack, and a 2 KB heap. This program runs on a 64 KB computer that manages memory with 4 kb segments. If the computer is empty and segments were allocated as: code, stack, heap, how large can the heap grow to?

32 KB

56 KB

24 KB

4 KB

0 KB

38

40

37

SEGMENTATION GRANULARITY - 2

Fine-grained

Manage memory as list of segments

Code, heap, stack segments composed of multiple smaller segments

Segment table

On early systems

Stored in memory

Tracked large number of segments

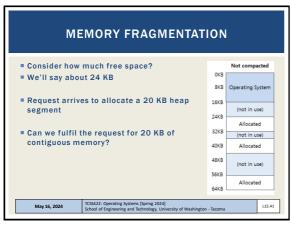

**COMPACTION** ■ Supports rearranging memory Compacted Can we fulfil the request for 20 KB of 8KB Operating Syste contiguous memory? 16KE Drawback: Compaction is slow Rearranging memory is time consuming 32KB • 64KB is fast 4GB+ ... slow 40KF 48KE Algorithms: (not in use) Best fit: keep list of free spaces, allocate the 56KB most snug segment for the request • Others: worst fit, first fit... (in future chapters) May 16, 2024 L15.42

41 42

) I

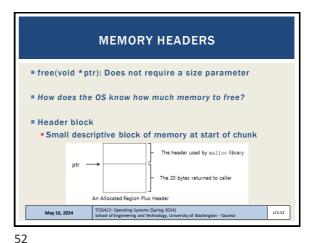

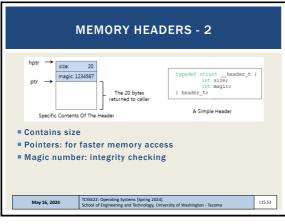

MEMORY HEADERS - 3

Size of memory chunk is:

Header size + user malloc size

N bytes + sizeof(header)

Easy to determine address of header

void free (void \*ptr) {

header\_t \*hptr = (void \*)ptr - sizeof(header\_t);

}

May 16, 2024

ICSS422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Tacoma

53 54

59 60

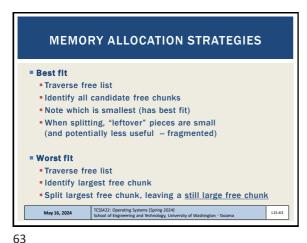

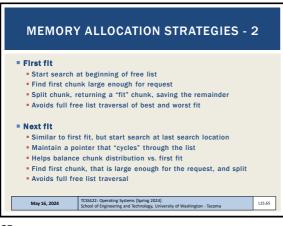

**EXAMPLES** Allocation request for 15 bytes Result of Best Fit Result of Worst Fit May 16, 2024 L15.64

64

Which memory allocation strategy is more likely to $^{lacktree}$ distribute free chunks closer together which could help when coalescing the free space list? Best Fit Worst Fit First Fit None of the above All of the above

65 66

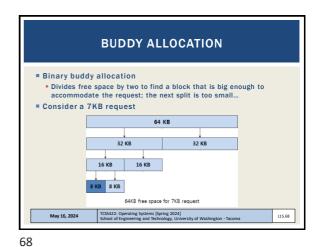

**BUDDY ALLOCATION - 2** Buddy allocation: suffers from internal fragmentation Allocated fragments, typically too large Coalescing is simple Two adjacent blocks are promoted up May 16, 2024 L15.69

A computer system manages program memory using three separate segments for code, stack, and the heap. The codesize of a program is 1KB but the minimal segment available is 16KB. This is an example of: External fragmentation Binary buddy allocation Internal fragmentation Coalescing **Splitting**

70

72

69

A request is made to store 1 byte. For this scenario, which memory allocation strategy will always locate memory the fastest? Best fit Worst fit Next fit None of the above All of the above 71

**OBJECTIVES - 5/16** ■ Questions from 5/14 Assignment 2 - May 31 Quiz 3 - Synchronized Array - May 23 ■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24 Assignment 3 (as a Tutorial) to be posted... ■ Chapter 16: Segmentation Chapter 17: Free Space Management - Chapter 18: Introduction to Paging Chapter 19: Translation Lookaside Buffer (TLB) TLB Algorithm, Hit-to-Miss Ratios Chapter 20: Paging: Smaller Tables Smaller Tables Multi-level Page Tables N-level Page Table May 16, 2024 TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma L15.72

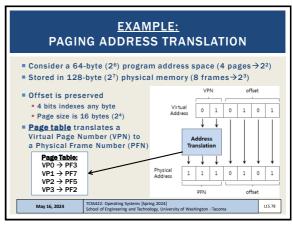

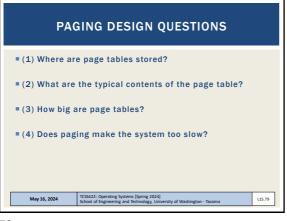

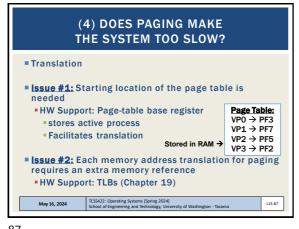

(1) WHERE ARE PAGE TABLES STORED?

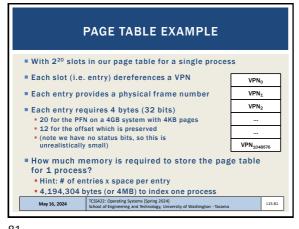

Example:

Consider a 32-bit process address space (4GB=2<sup>32</sup> bytes)

With 4 KB pages (4KB=2<sup>12</sup> bytes)

Distriction of the page of

80

82

79

NOW FOR AN ENTIRE OS

If 4 MB is required to store one process

Consider how much memory is required for an entire OS?

With for example 100 processes...

Page table memory requirement is now 4MB x 100 = 400MB

If computer has 4GB memory (maximum for 32-bits), the page table consumes 10% of memory

400 MB / 4000 GB

Is this efficient?

May 16, 2024

TCS422: Operating Systems (Spring 2024)

School of Engineering and Technology, University of Washington - Tacoma

81

83 84

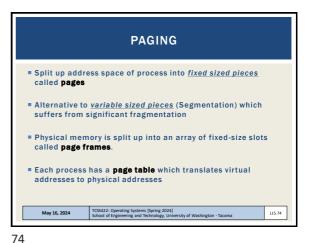

(3) HOW BIG ARE PAGE TABLES? Page tables are too big to store on the CPU Page tables are stored using physical memory Paging supports efficiently storing a sparsely populated address space Reduced memory requirement Compared to base and bounds, and segments May 16, 2024 L15.86

86

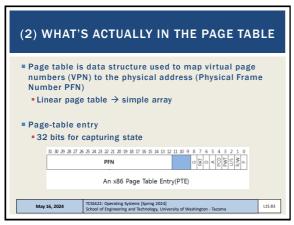

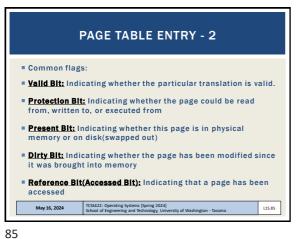

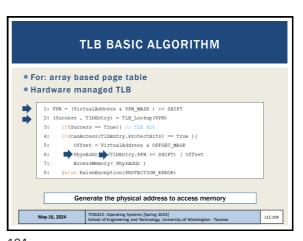

**PAGING MEMORY ACCESS** // Extract the VPN from the VITTUAL address

VPN = (VirtualAddress & VPN\_MASK) >> SHIFT // Form the address of the page-table PTEAddr = PTBR + (VPN \* sizeof(PTE)) PTE = AccessMemory(PTEAddr) 9. 10. 11. // Check if process can

if (PTE.Valid == False) RaiseException(SEGMENTATION\_FAULT)

else if (Canaccess(PTE.ProtectBits) == False)

RaiseException(PROTECTION\_FAULT) 12. 13. 14. 15. ical address and fetch it offset = VirtualAddress & OFFSET\_MASK PhysAddr = (PTE.PFN << PFN\_SHIFT) | offset Register = AccessMemory(PhysAddr) May 16, 2024 L15.88

88

87

```

COUNTING MEMORY ACCESSES

Example: Use this Array initialization Code

int array[1000];

for (i = 0; i < 1000; i++)

array[i] = 0;

Assembly equivalent:

0x1024 movl S0x0, (%edi, %eax, 4)

0x1028 incl %eax

0x102c cmpl S0x03e8, %eax

0x1030 jne 0x1024

TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma

May 16, 2024

L15.89

```

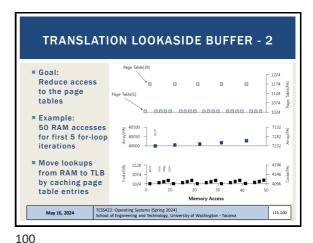

**VISUALIZING MEMORY ACCESSES:** FOR THE FIRST 5 LOOP ITERATIONS Locations: Page table 1174 Array - 1124 • Code 1074 0 0000 0000 0000 0000 000 - 1024 ■ 50 accesses for 5 loop 7282 iterations 4146 TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, Uni May 16, 2024 L15.90 ersity of Washington - Tacoma

89 90

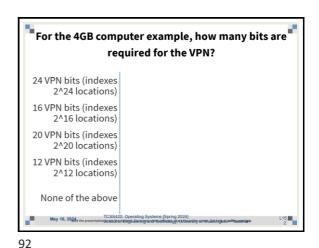

For the 4GB computer example, how many bits are available for page status bits?

32 - 12 VPN bits

= 20 status bits

32 - 24 VPN bits

= 8 status bits

32 - 16 VPN bits

= 16 status bits

32 - 12 VPN bits

= 12 status bits

None of the above

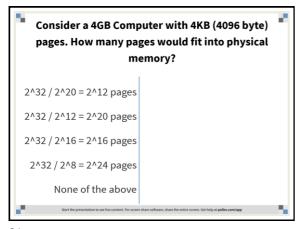

For the 4GB computer, how much space does this page table require? (number of page table entries x size of page table entry)

2^20 entries x 4b = 4 MB

2^12 entries x 4b = 16 KB

2^16 entries x 4b = 256 KB

2^24 entries x 4b = 64 MB

None of the above

93

For the 4GB computer, how many page tables (for user processes) would fill the entire 4GB of memory?

4 GB / 16 KB = 65,536

4 GB / 64 MB = 256

4GB / 256 KB = 16,384

4GB / 4MB = 1,024

None of the above

**PAGING SYSTEM EXAMPLE** Consider a 4GB Computer: With a 4096-byte page size (4KB) How many pages would fit in physical memory? Now consider a page table: For the page table entry, how many bits are required for the VPN? If we assume the use of 4-byte (32 bit) page table entries, how many bits are available for status bits? How much space does this page table require? # of page table entries x size of page table entry How many page tables (for user processes) would fill the entire 4GB of memory? TCSS422: Operating Systems [Spring 2024] School of Engineering and Technology, Uni May 16, 2024 L15.96

96

94

95

9/

101 102

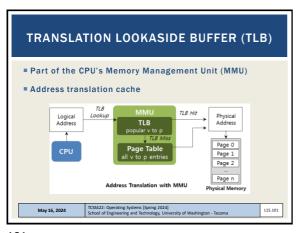

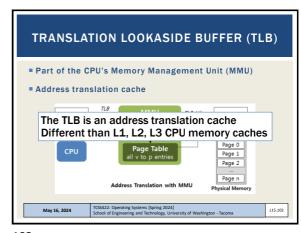

TLB - ADDRESS TRANSLATION CACHE

\*\*Key detail:

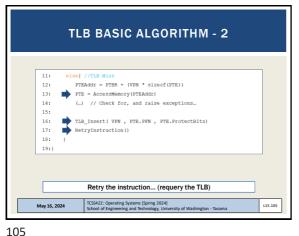

\*\*For a TLB miss, we first access the page table in RAM to populate the TLB... we then requery the TLB

\*\*All address translations go through the TLB

\*\*May 16, 2024

TCSS42: Operating Systems [Spring 2024] School of Engineering and Technology, University of Washington - Tacoma

105 106

```

OBJECTIVES - 5/16

Questions from 5/14

Assignment 2 - May 31

Quiz 3 - Synchronized Array - May 23

■ Tutorial 2 - Pthread, locks, conditions tutorial -Fri May 24

Assignment 3 (as a Tutorial) to be posted...

■ Chapter 16: Segmentation

■ Chapter 17: Free Space Management

Chapter 18: Introduction to Paging

Chapter 19: Translation Lookaside Buffer (TLB)

TLB Algorithm Hit-to-Miss Ratios

Chapter 20: Paging: Smaller Tables

Smaller Tables Multi-level Page Tables N-level Page Table

May 16, 2024

TCSS422: Operating Systems [Spring 2024]

School of Engineering and Technology, University of Washington - Tacoma

L15.107

```

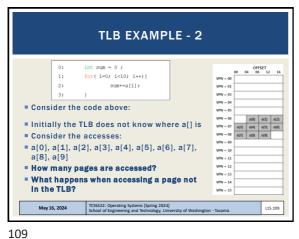

**TLB EXAMPLE** for( i=0; i<10; i++){ VPN = 03 Example: VPN - 05 Program address space: 256-byte Addressable using 8 total bits (28) VPN = 08 VPN = 09 4 bits for the VPN (16 total pages) VPN = 1 Page size: 16 bytes VPN = 12 Offset is addressable using 4-bits VPN - 14 Store an array: of (10) 4-byte integers May 16, 2024 L15.108 ersity of Washington - Tacoma

107 108

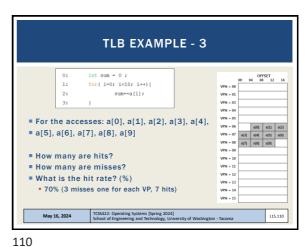

| TLB EXAMPLE - 4                                                                                                                                                                     |                                                  |                                                          |                                  |                                |                      |              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------|----------------------------------|--------------------------------|----------------------|--------------|

|                                                                                                                                                                                     | t sum = 0 ;<br>r( i=0; i<10; i++){<br>sum+=a[i]; |                                                          | VPN = 00<br>VPN = 01<br>VPN = 03 | 0 04                           | FFSET<br>08 12       | 16           |

| <ul> <li>What factors affect the hit/miss rate?</li> <li>Page size</li> <li>Data/Access locality (how is data accessed?)</li> </ul>                                                 |                                                  |                                                          | VPN = 05<br>VPN = 06<br>VPN = 07 | a[0]<br>a[3] a[4]<br>a[7] a[8] | a[1]<br>a[5]<br>a[9] | a[2]<br>a[6] |

| <ul> <li>Sequential array access vs. random array access</li> <li>Temporal locality</li> <li>Size of the TLB cache</li> </ul>                                                       |                                                  | VPN = 10<br>VPN = 11<br>VPN = 12<br>VPN = 13<br>VPN = 14 | - 11<br>- 12<br>- 13             |                                |                      |              |

| (how much history can you store?)  WN - 14  WN - 15  May 16, 2024  TCSS422: Operating Systems (Spring 2024) School of Engineering and Technology, University of Washington - Tacoma |                                                  |                                                          |                                  |                                |                      |              |

113