| FEEDBACK FROM 5/15 |  |

|--------------------|--|

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

|                    |  |

Slides by Wes J. Lloyd

14

15

17

Openation

Openation

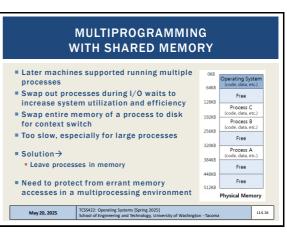

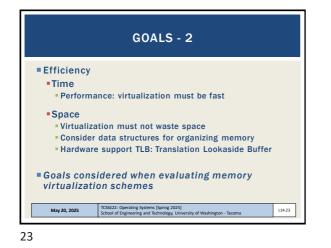

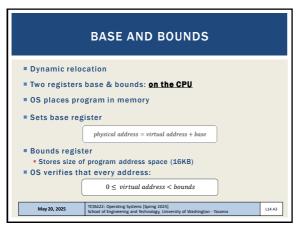

• Transparency

• Memory shouldn't appear virtualized to the program

• OS multiplexes memory among different jobs behind the scenes

• Protection

• Isolation among processes

• OS itself must be isolated

• One program should not be able to affect another (or the OS)

26

27

29

33

35

CALLOC()

finclude <stdlib.h>

void \*calloc(size\_t num, size\_t size)

Allocate \*C"lear memory on the heap

Calloc wipes memory in advance of use...

size\_t num : number of blocks to allocate

size\_t size : size of each block(in bytes)

Calloc() prevents...

Char \*dest = malloc(20);

printf("dest string=%s\n", dest);

dest string=□□F

TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, Uni

sity of Washington - Ta

34

May 20, 2025

L14.34

39

41

40

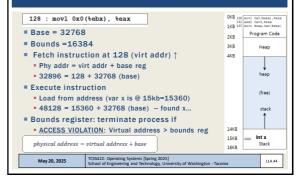

**INSTRUCTION EXAMPLE**

44

45

46

48

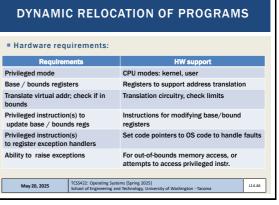

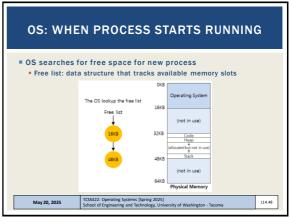

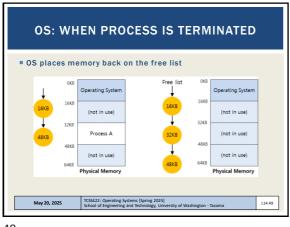

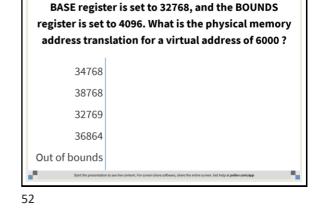

## OS SUPPORT FOR MEMORY VIRTUALIZATION For base and bounds OS support required When process starts running Allocate address space in physical memory When a process is terminated Reclaiming memory for use When context switch occurs Saving and storing the base-bounds pair Exception handlers Function pointers set at OS boot time May 20, 202 Total Eggenerg Setting Systems (Bring 202)

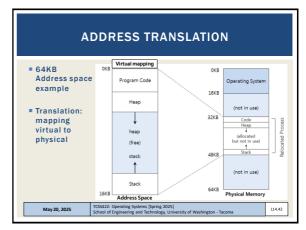

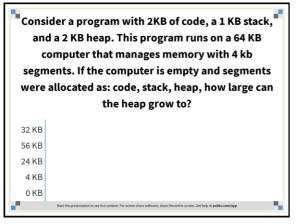

Consider a 64KB computer the loads a program. The

**OS: WHEN CONTEXT SWITCH OCCURS**

Saved to the Process Control Block PCB (task\_struct in Linux)

166

Operating Syster

(not in use)

Process A

Physical Me

of Wa

Context Switching

32KB

48KB

ocess A PCE

base : 32KB bounds : 48KB

L14.50

48KB

64KB

OS must save base and bounds registers

Operating Syste

(not in use)

Process B Physical Mem

May 20, 2025

50

TCSS422 School of

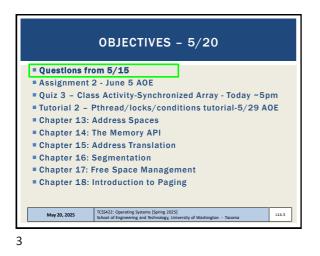

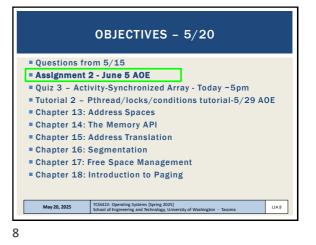

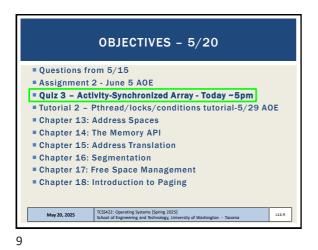

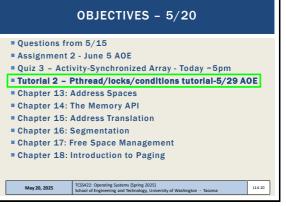

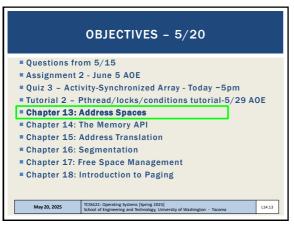

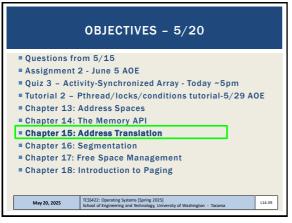

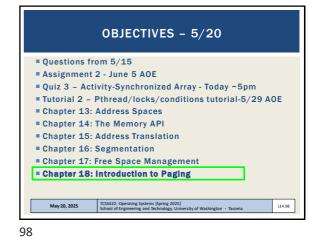

OBJECTIVES - 5/20

• Questions from 5/15

• Assignment 2 - June 5 AOE

• Quiz 3 - Activity-Synchronized Array - Today ~5pm

• Tutorial 2 - Pthread/locks/conditions tutorial-5/29 AOE

• Chapter 13: Address Spaces

• Chapter 14: The Memory API

• Chapter 15: Address Translation

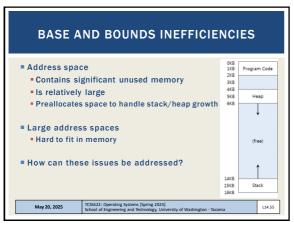

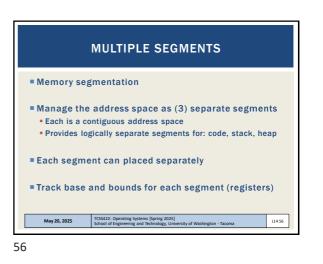

• Chapter 16: Segmentation

• Chapter 17: Free Space Management

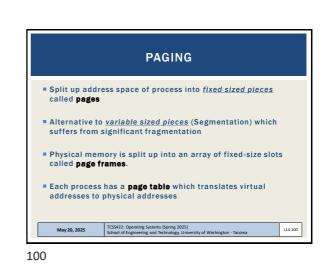

• Chapter 18: Introduction to Paging

57

59

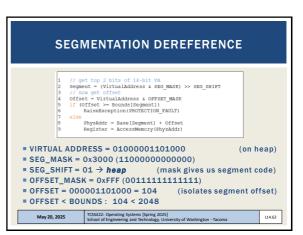

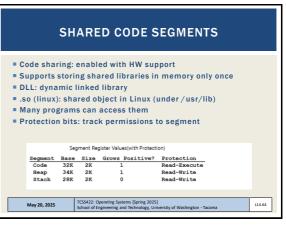

|                              | SEGMENT REGIST                                                                                                                        | ERS                               |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|                              | ierence memory during trans           13         12         11         10         9         7         6         5         4         3 | 2 1 0                             |

| Remaining bi                 | identify segment type<br>ts identify memory offset<br>ual heap address 4200 (010                                                      | 00001101000)                      |

| 13 12 11<br>0 1 0<br>Segment | 10 9 8 7 6 5 4 3 2 1 0<br>0 0 0 0 1 1 1 0 1 0 0 0<br>0 0 0 0 0 1 1 1 0 1 0                                                            | SegmentbitsCode00Heap01Stack10-11 |

| May 20, 2025                 | TCSS422: Operating Systems [Spring 2025]<br>School of Engineering and Technology, University of Was                                   | shington - Tacoma                 |

63

65

62

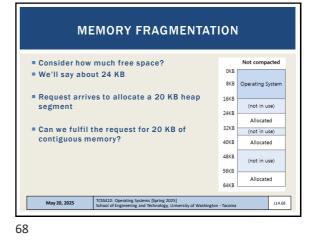

COMPACTION Supports rearranging memory Compacted OKB Can we fulfil the request for 20 KB of 8KB Operating System contiguous memory? 16K Drawback: Compaction is slow 24KB Rearranging memory is time consuming Allocated 32KE 64KB is fast 4GB+ ... slow 40KF 48KE Algorithms: (not in use) Best fit: keep list of free spaces, allocate the 56KB most snug segment for the request 64KE • Others: worst fit, first fit... (in future chapters) TCSS422: Operating Systems [Spring 2025] School of Engineering and Technology, Uni May 20, 2025 L14.69

69

71

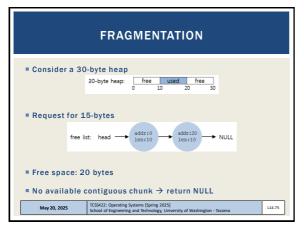

74

75

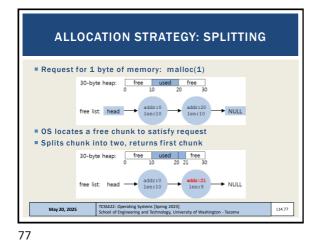

76

81

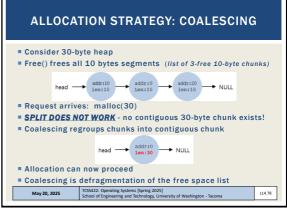

80

87

86

88

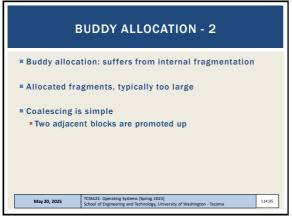

SEGREGATED LISTS

• For popular sized requests e.g. for kernel objects such as locks, inodes, etc.

• Manage as segregated free lists

• Provide object caches: stores pre-initialized objects

• How much memory should be dedicated for specialized requests (object caches)?

• If a given cache is low in memory, can request "slabs" of memory from the general allocator for caches.

• General allocator will reclaim slabs when not used

May 20, 2025

TCSM22: Operating Systems [Spring 2023] School of Engineering and Technology, University of Washington - Tacoma

93

99

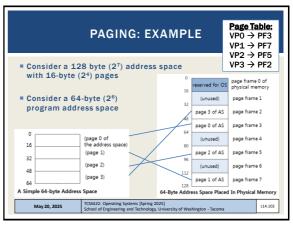

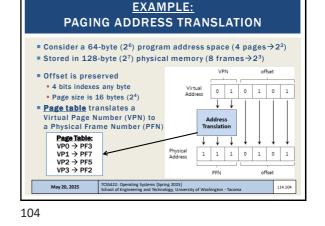

| PAGING:                                                                         | ADDRESS TRANSLATION                                                                                     |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| VPN: Virtual Pa                                                                 | ddress components<br>ge Number (serves as the page ID)<br>vithin a Page (indexes any byte in the page)  |

| <ul> <li>Example:</li> <li>Page Size: 16-by</li> <li>Program Address</li> </ul> | VPN offset<br>vs5 vs4 vs3 vs2 vs1 vs0<br>rtes (2 <sup>4</sup> ),<br>s Space: 64-bytes (2 <sup>6</sup> ) |

|                                                                                 | VPN         offset           0         1         0         1                                            |

|                                                                                 | 22: Operating Systems [Spring 2025]<br>of Engineering and Technology, University of Washington - Tacoma |

105

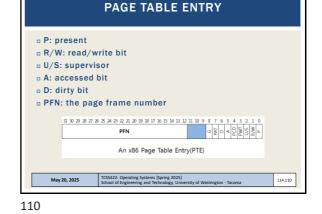

| (2) WHAT'S ACTUALLY IN THE PAGE TABLE                                                                                                                    |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| <ul> <li>Page table is data structure used to map virtual page<br/>numbers (VPN) to the physical address (Physical Frame<br/>Number PFN)</li> </ul>      |   |

| <ul> <li>Linear page table → simple array</li> <li>Page-table entry</li> <li>32 bits for capturing state</li> </ul>                                      |   |

| 31 30 29 28 27 26 26 34 23 22 21 20 19 19 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 1<br>PFN U U E O F ( )                                               |   |

| An x86 Page Table Entry(PTE)                                                                                                                             |   |

| May 20, 2025         TCSS422: Operating Systems [Spring 2025]<br>School of Engineering and Technology. University of Washington - Tacoma         L14.109 | , |

PAGE TABLE ENTRY - 2

• Common flags:

• Yalid Bit: Indicating whether the particular translation is valid.

• Protection Bit: Indicating whether the page could be read from, written to, or executed from

• Present Bit: Indicating whether this page is in physical memory or on disk(swapped out)

• Dirty Bit: Indicating whether the page has been modified since it was brought into memory

• Reference Bit(Accessed Bit): Indicating that a page has been accessed

May 20, 223

TCS422: Operating Systems (pring 2025) School of Engineering and Rehnology, University of Washington - Tacoma

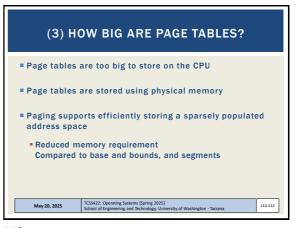

111

112

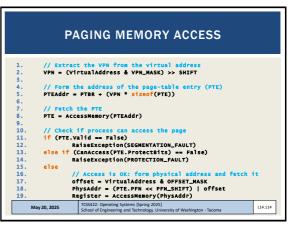

|                                 | 4) DOES PAGING MAKE<br>HE SYSTEM TOO SLOW?                                                                         |                                                                                                 |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Translation                     |                                                                                                                    |                                                                                                 |

| ■ <u>Issue #1:</u> St<br>needed | arting location of the page tab                                                                                    | le is                                                                                           |

| stores ac                       | rt: Page-table base register<br>tive process<br>es translation<br>Stored in RAM →                                  | Page Table:VP0 $\rightarrow$ PF3VP1 $\rightarrow$ PF7VP2 $\rightarrow$ PF5VP3 $\rightarrow$ PF2 |

| requires an                     | ch memory address translatio<br>extra memory reference<br>rt: TLBs (Chapter 19)                                    | n for paging                                                                                    |

| May 20, 2025                    | TCSS422: Operating Systems [Spring 2025]<br>School of Engineering and Technology, University of Washington - Tacor | ma L14.113                                                                                      |

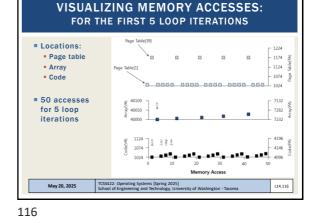

117

123