# B EE 215 - Laboratory 5 - Second Order Circuits

## Authors

R.D. Christie

## **Objectives**

At the end of this lab, you will be able to:

- Observe and classify the time response of a second order circuit.

- Design with RLC circuits

## Materials and Supplies

See Laboratory 1 for information on the parts kit and multimeter, and for identifying many of the parts used in Laboratory 5.

### Parts for This Lab

No new types of parts are used in this lab.

## Laboratory Procedures, Measurements and Questions

Procedure 1: (60 points) Series RLC Circuit

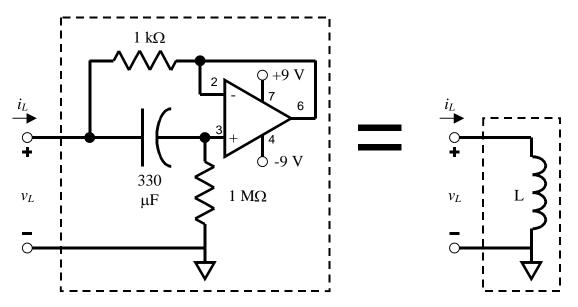

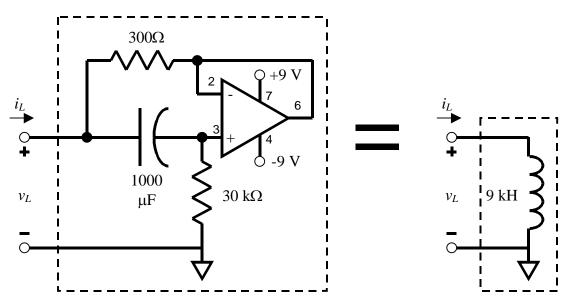

Figure P1-1 Simulated inductor circuit

**a.** (**20 points**) In this portion of the laboratory we will use a simulated inductor with components shown in Figure P1-1. This simulated inductor has an inductance of

$$L_{eq} = R_s R_f C = 1k \cdot 1M \cdot 330\mu = 330kH$$

(This is an incredibly high inductance that would be almost impossible to build using a core and windings!)

The nominal internal DC resistance of the simulated inductor is 1 k $\Omega$ .

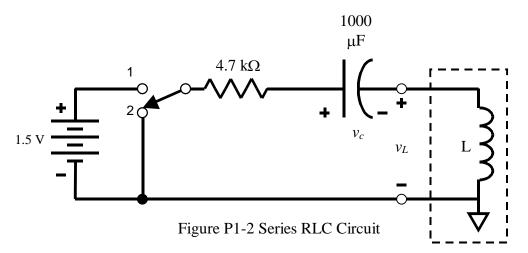

For the circuit of Figure P1-2, using the simulated inductor from Figure P1-1, the switch has been in the down (2) position for a long time. Using nominal component values, find the complete time response of the capacitor voltage,  $v_c(t)$ , when the switch is moved to the up (1) position at t = 0s. Prepare a table of computed voltage values for 15 second intervals between 0 and 180 seconds. Plot the time response for  $0 \le t \le 180$  seconds. (Note: You will add data to this plot in later parts.)

Is this response overdamped, underdamped or critically damped?

**b.** (**30 points**) Construct the circuit of Figure P1-2.

After reaching steady state with the switch in the down (2) position, move the switch to the up (1) position and record capacitor voltage  $v_c$  every 15 seconds for three minutes. Additional observers should note the time and magnitude of any maximum and minimum voltages observed.

Record the observed values next to the computed values from part (a).

Add the observed data to the graph from part (a). Comment on differences.

Note: With time constants as long as are present in this experiment, obtaining a steady state initial condition can take an annoyingly long time. The following steps will achieve a near-steady state condition suitable for starting:

1. Short both capacitors with jumper wires.

2. A few seconds before t = 0, pull the shorts across the capacitors. Capacitor voltage may slowly start to change, but the effect of moving the switch should be much more significant.

Also, recall the advice from Lab 4 about op amp power supplies. If your circuit is not responding as expected, check the power supplies first.

c. (10 points) Add a 30 k $\Omega$  resistor to the series resistance so the total is 34.7 k $\Omega$  plus inductor internal resistance. Establish an initial steady state condition with the switch in the down (2) position. Move the switch to the up (1) position and record capacitor voltage every 15 seconds for three minutes. Add this data to your table of results and graph.

Based on the graph, is this time response overdamped, underdamped, or critically damped?

#### Procedure 2 (30 points) Design with LCR Circuits

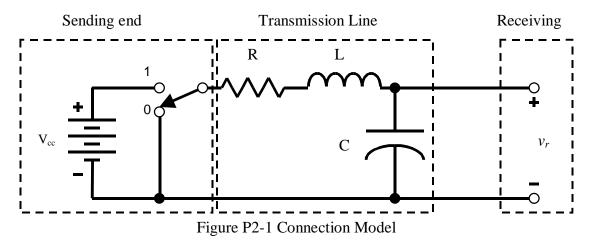

Design with LCR circuits, particularly with transient response, is often more about coping with the existence of L and C rather than creating a circuit to perform a specific function. Consider the problem of sending a bit from one part of a computer to another. The parts are connected by conducting traces on an insulating circuit board. To a first approximation, these are just wires - short circuits. But the traces have a small but non-zero resistance, and as you will learn in electromagnetics, they also form distributed inductance and capacitance. A trace is a form of transmission line. Most transmission lines - "short" ones - can be modeled with a series LCR circuit, as shown in Figure P2-1.

The R, L and C of the transmission line can be changed only by changing the physical properties of the lines - length, width, insulation type and thickness, conductor material. These are generally dictated by other considerations. For example, length is always minimized, and conductor material is chosen for the best tradeoff between performance and cost.

The effect of the non-ideal transmission line on the movement of a bit from the sending end to the receiving end depends on the component values. As you have seen in procedure 1, if the RLC circuit is underdamped, the receiving end voltage can vary quite a bit around the nominal end value. This is called *ringing*. Ringing causes voltages higher than the final steady state voltage (*overshoot*) to appear at the receiving end. This can exceed voltage ratings and cause damage to the receiving end electronics. The receiving end knows that a "1" has been sent when its voltage exceeds a threshold somewhat below the final voltage. Ringing cause the receiving end voltage to exceed and then drop below this threshold, causing the receiving end to think that it has gotten a "1", a "0" and then a "1" when only a "1" was sent. Thus excessive ringing cause damage or malfunction.

On the other hand, if the RLC circuit is overdamped, the receiving end voltage does not exceed its final value, but approaches it slowly. This means that the time between the sending end sending the "1" and the receiving end receiving the "1" is longer, and the computer runs slower.

Similar issues appear when a "1" to "0" transition occurs at the sending end.

**a.** (**15 points**) The design challenge is to modify the RLC characteristic of a transmission line to achieve good sending end to receiving end performance for a "0" to "1" transition.

"Good performance" for this problem means that when the sending end goes high (switch up, (1)), the receiving end voltage crosses 90% of its final value as quickly as possible (minimum *rise time*), and does not go back under 90% of its final value after crossing it.

Good performance also means overshoot of less than 10% of the final value.

(Good performance also means a final value within a specified, high percentage of the supply voltage,  $V_{cc}$ , but this is not a design requirement for this problem.)

Given the known inaccuracies in actual transistor values, an obvious way to achieve good performance is to adjust the RLC circuit to achieve critical damping. A critically damped circuit will have neither overshoot nor ringing, and will approach the final value faster than an overdamped circuit. A more aggressive design might allow a small amount of ringing in exchange for a faster rise time, but for this design problem, critical damping is desired.

Add a resistor to the transmission line circuit of Figure P2-1 with  $V_{cc} = 1.5$  V, R = 350  $\Omega$ , L = 9 kH and C = 330  $\mu$  to achieve critical damping. Compute a resistance value using nominal component values, then choose an appropriate resistor from the set of resistors supplied with your lab kit. Plot the expected time response of the receiving end voltage for a "0" to "1" transition. Include your design calculations.

Note that you cannot insert components inside the dashed lines in Figure P2-1. The R, L and C shown are not individual components you can separate out, but rather properties inherent in one physical object, the trace connecting the two ends.

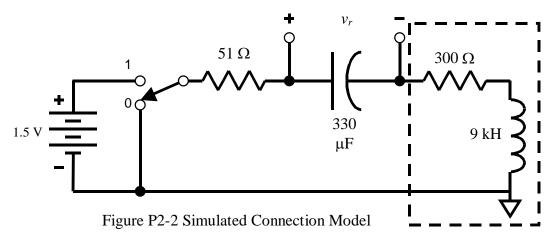

**b.** (15 points) Build the circuit of Figure P2-2 with the simulated inductor of Figure P2-3. For a switch transition from down (0) to up (1), observe and record the maximum value, the next minimum value, and the time to 90% of the final value of the "receiving end" voltage  $v_r$ .

Add your design resistance to the circuit in the appropriate location For a switch transition from down (2) to up (1), observe and record the maximum value, the next minimum value, and the time to 90% of the final value of the "receiving end" voltage  $v_r$ . Comment on how well your circuit meets the design criteria of step a.

Note: Because the simulated inductor must have one end grounded, the inductor and capacitor locations are swapped compared to Figure P2-1. This does not change the terminal voltage response! Also, the internal resistance of the simulated inductor is counted as part of the total resistance of the transmission line (R in Figure P2-1).

Figure P2-3 Simulated inductor circuit for Procedure 2

Note also! The component values of the transmission line in this experiment are obviously NOT those of a transmission line on a computer circuit board. The component values here are chosen to permit you to observe the change in voltage with a voltmeter and a stopwatch. In a computer, transition times are much, much, much smaller.

#### Procedure 3. (30 points) Simulation using LTspice

WASHINGTON

- a. (10 points) Run transient simulations for Figure P1-2, assuming the switch was turned up after it has been down for a very long time. Plot the time response of the voltage across the capacitor for  $0 \le t \le 180$  seconds. Determine whether the response is overdamped, underdamped, or critically damped. Take a note of the local maxima and minima points of the graph and compare them with the corresponding points on the graphs obtained analytically and through measurement.

- b. (10 points) Repeat the above procedure (procedure 3a) by the changing the value of the resistor to the one given in procedure 1c. Determine whether the response is overdamped, underdamped, or critically damped? Compare the graph obtained with that of procedure 1b.

- c. (10 points) Simulate the transition from "0" to "1" of your RLC design in procedure 2. Check from your graph, if the response meets the performance requirements.